System Generator是Xilinx公司进行数字信号处理开发的一种设计工具,它通过将Xilinx开发的一些模块嵌入到Simulink的库中,可以在Simulink中进行定点仿真,可以设置定点信号的类型,这样就可以比较定点仿真与浮点仿真的区别。并且可以生成HDL文件,或者网表,可以在ISE中进行调用。或者直接生成比特流下载文件。能够加快DSP系统的开发进度。

一、利用MCode调用MATLAB代码

1、简介

本设计是利用MCode设计一个有限状态机(FSM),从而实现一个序列检测器。

FPGA设计中经常用到一些控制逻辑,如有限状态机(FSM),如果用各种block搭建一个FSM比较麻烦。System Generator支持调用MATLAB代码,通常可以编写MATLAB代码来实现FSM等控制逻辑,通过MCode block调用到System Generator设计中。

具体介绍大家可以看看这篇博文,Verilog序列检测器-两例 https://blog.csdn.net/Pieces_thinking/article/details/78704437 。

本文将使用MATLAB代码设计一个FSM,对“1011”这个序列进行检测。

2、本设计使用到的block

Xilinx block

MCode(->Index):调用MATLAB函数

其它block

Repeating Sequence Stair(Simulink->Sources):生成序列

3、Generator设计流程

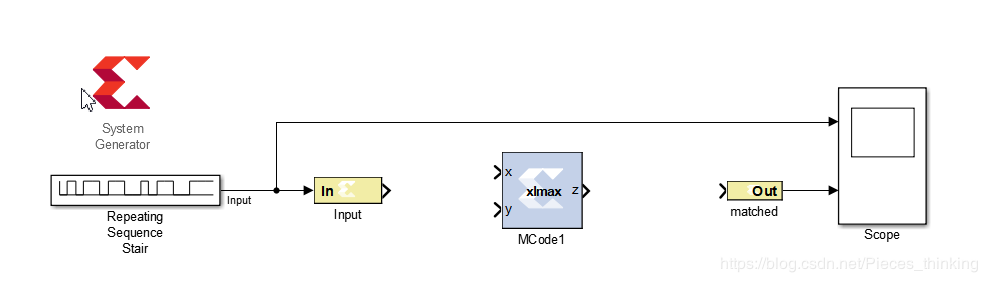

在库中在库中找到Repeating Sequence Stair、Gateway In、MCode、Gateway Out、System Generator、scope,分别添加到model中,如下:

3.1 生成二进制序列

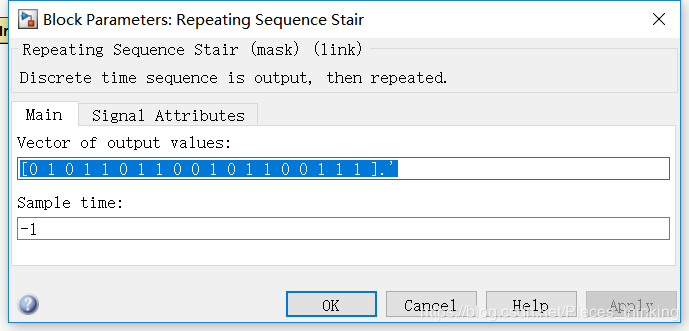

双击Repeating Sequence Stair,如下设置:

该block可以产生重复的离散时间序列,在Vector of output values中设置一组序列(该值不是必须设置为0或1,只是本设计要检测二进制序列)。Signal Attributes->Output data type中可以设置输出数据的类型,这里设置为Boolean。

设置完毕后,该block在model中的图标会显示一个大致的波形,可以据此判断设置是否正确。

3.2 序列检测器设计

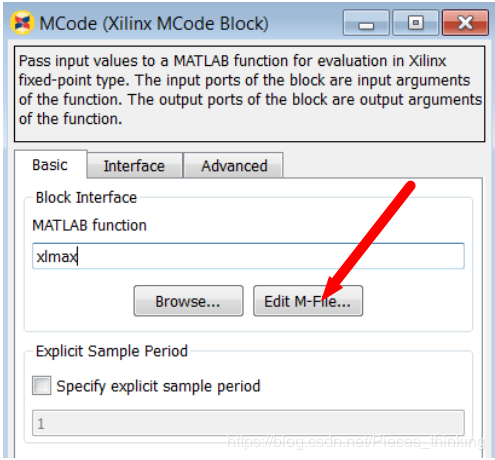

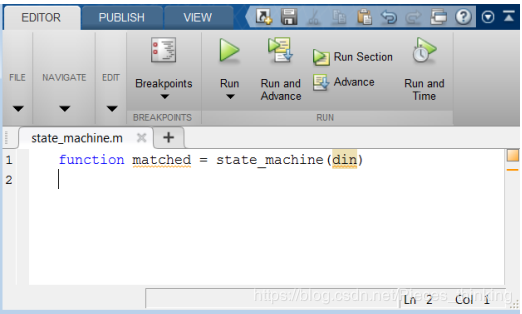

双击MCode块并单击Edit M-File,如下图所示:

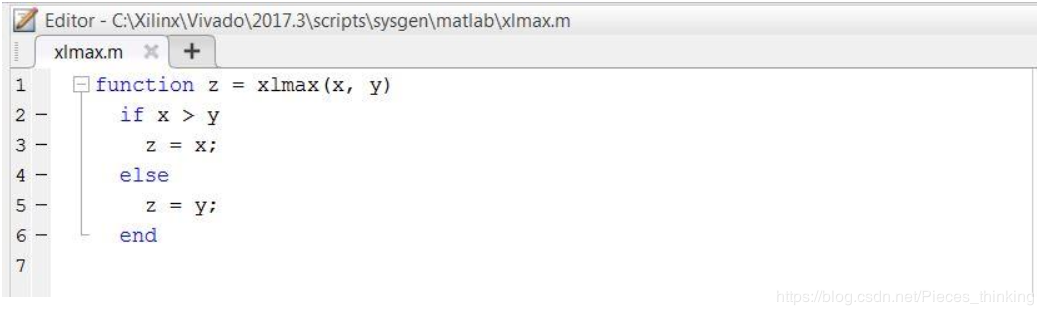

下图显示了MATLAB文本编辑器中的默认m代码。

编辑默认的MATLAB函数,包括函数名state_machine和匹配的输入din和输出matched。

进行编辑后,使用Save As将MATLAB文件保存为state_machine.m到相关工程文件夹。

PS:在MCode属性编辑器中,可以使用Browse按钮引用本地M-code文件(state_machine.m)。

在MCode Properties Editor单击 OK按钮。

设置完毕后,该block在model中的图标会更换为对应的函数名称及输入/输出接口。再添加1个scope观察二进制序列与检测结果。model连接图如下:

3.3 有限状态机设计

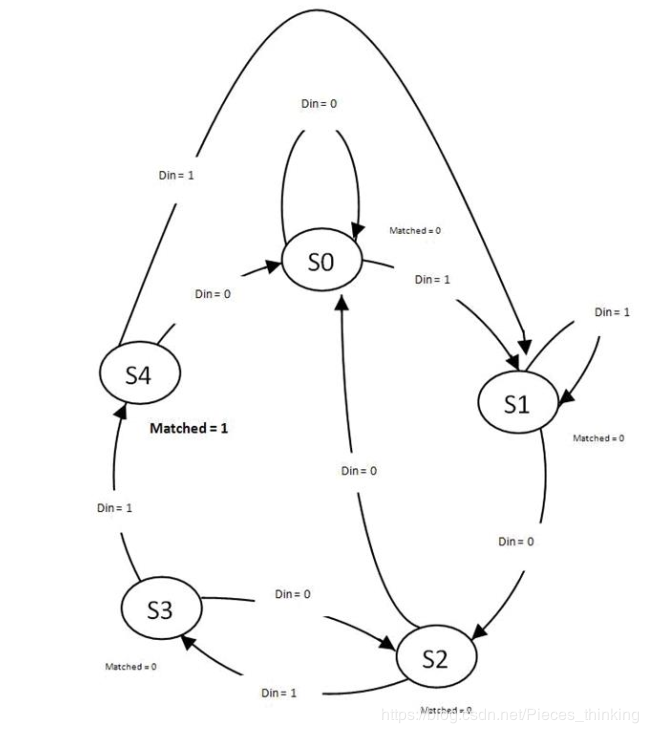

现在可以开始编写状态机了。这个状态机的气泡图如下图所示。该FSM有五种状态,能够连续检测两个序列。

状态机的工作流程如下:

3.4 MATLAB代码设计

Edit the M-code file, state_machine.m

function matched = state_machine(din)

persistent state, state = xl_state(0,{xlUnsigned, 3, 0});

switch state

case 0

if din == 1

state = 1;

else

state = 0;

end

matched = 0;

case 1

if din == 0

state = 2;

else

state = 0;

end

matched = 0;

case 2

if din == 1

state = 3;

else

state = 0;

end

matched = 0;

case 3

if din == 1

state = 4;

else

state = 2;

end

matched = 0;

case 4

if din == 0;

state = 0;

else

state = 1;

end

matched = 1;

otherwise

state = 0;

matched = 0;

end

定义一个3Bits宽的(3-0)无符号(xlUnsigned)状态变量xl_state,使用switch语法控制状态之间的转移。由于3Bits位宽数据可表示07,而FSM状态只有04,所以一定要加上otherwise控制状态转移。

System Generator并不是支持所有的MATLAB语法和格式,还有一部分为Xilinx自定义的函数和数据格式,这部分的详细内容(支持的所有MATLAB语法)都记录在ug958这篇文档中。具体可参考该文档,下面也会简单进行介绍。

3.5 将设计导出到FPGA

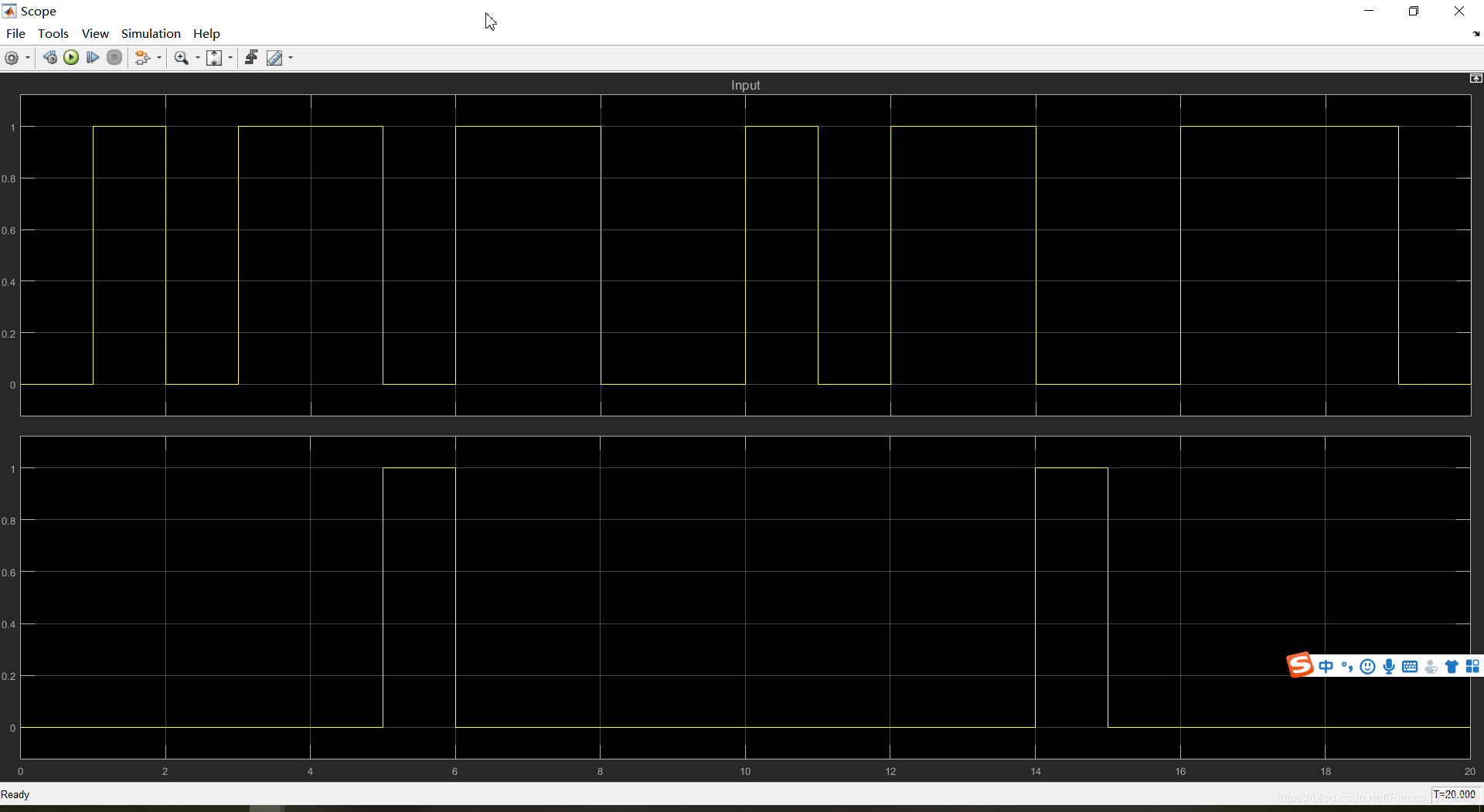

在System Generator block中设置好Simulink采样周期,设置好运行时间,开始运行验证设计。这里介绍一个仿真运行时间的设计技巧:假设系统采样率为50MHz,示波器中只需要显示20个点即可,运行时间可设置为“20/50e6”。

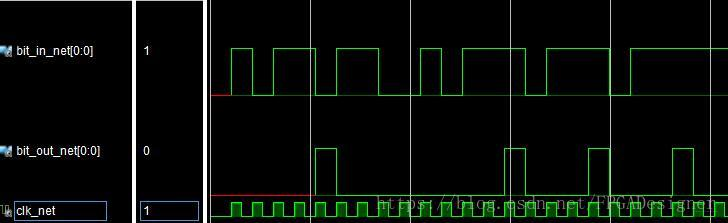

可以看到每检测到一组“1011”序列后,便输出一个时钟周期的高电平。生成FPGA设计,在Vivado中进行仿真,结果与Simulink中仿真相同:

4、支持的MATLAB语法

原文:https://blog.csdn.net/FPGADesigner/article/details/80963366

详细的信息可以参考xilinx官方文档ug958->第一章->MCode小节,传送门。

4.1 MCode block特性

MCode用于在Simulink环境下执行MATLAB函数。MCode的名称与管脚即为函数名称与函数接口。在将System Generator设计导出到FPGA时,软件会将MATLAB代码转换为对应的HDL模型。MCode经常用于实现一些简单的算法功能、有限状态机和控制逻辑。

调用的MATLAB函数必须遵循以下三条基本规则:

当初次使用MCode时,会自动调用一个示例文件xlmax.m。博主建议先在slx文件目录下创建好新的m文件,再用Browse定位。

4.2 支持的MATLAB语法

4.2.1 所支持的MATLAB语法结构包括:

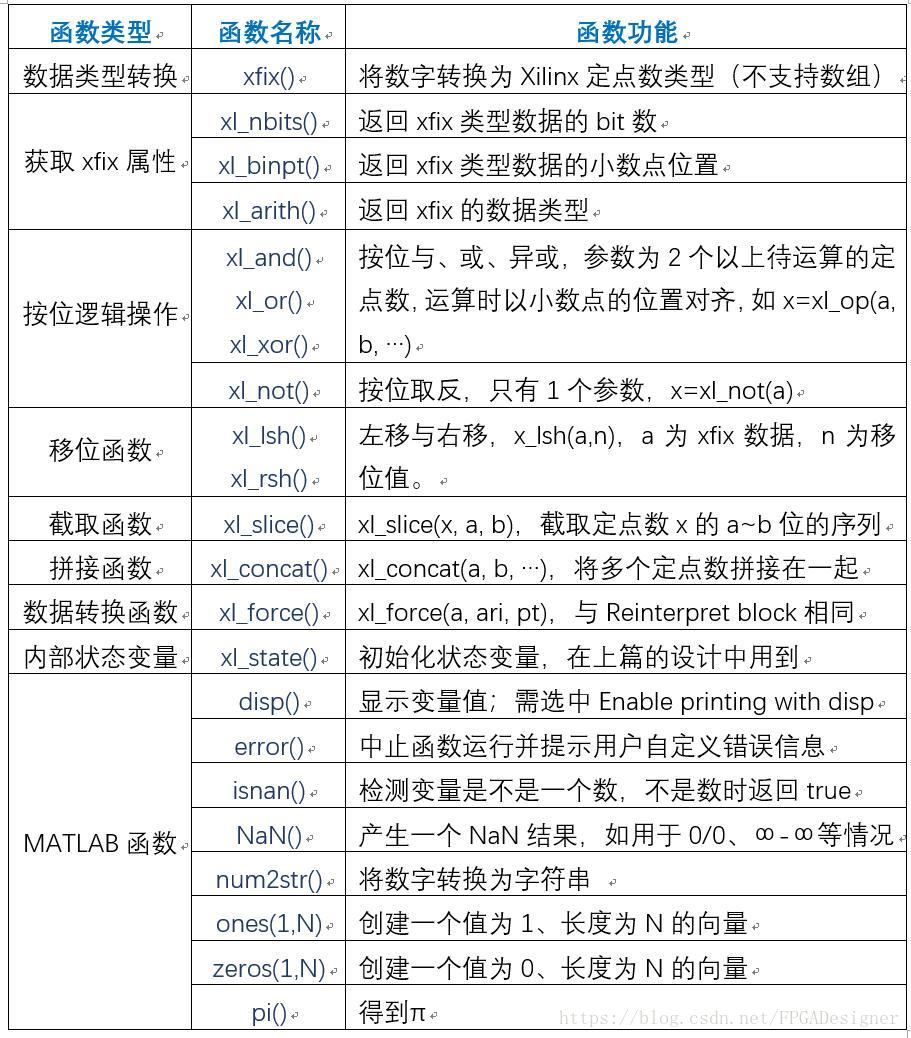

4.2.1 所支持的MATLAB函数及其功能

4.3 xfix数据类型

xfix有三种数据类型:无符号定点数(xlUnsigned)、带符号定点数(xlSigned)、布尔值(xlBoolean)。使用xl_arith()判断数据类型时分别返回1、2、3。需要注意几点:

编写MATLAB代码时,仍然可以使用整数、浮点数、布尔值来定义常量。整数和布尔值都会自动转换为xifix类型;浮点数需要用xfix()函数转换。xfix()函数还可以完成不同xifix数据类型的转换,其基本形式为:

x = xfix(type_spec, value);

value为待转换的数,type_spec为转换后的数据类型。比如将浮点数π转换为xfix类型:

x = xfix({xlSigned, 20, 16, xlRound, xlWrap}, 3.1415926);

转换后为Fix_20_16格式,Round量化,Wrap溢出(前面的文章中已经解释了这些含义)。量化方式可设置为xlTruncate、xlRound和xlRoundBBanker;溢出方式可设置为xlWrap、xlSaturate、xlThrowOverflow。

4.4 xl_state状态变量

在整个仿真过程中,一个MATLAB函数会执行多次,必须保证其中的状态变量在每次执行完时保留其值(类似与C++语言中的static静态变量),否则无法正确实现控制功能。

状态变量在MATLAB中需要用persistent关键词和xl_state函数定义,如下所示:

persistent s, s = xl_state(0, {xlSigned, 4, 0});

该函数有两个参数:第一个0表示状态初始值,必须是常数;第二个参数是状态变量的数据类型,与xfix函数中的type_spec用法相同。状态变量还可以是一个向量,并且拥有许多配套的函数,ug958中给出了多个使用xl_state完成的设计实例。

4.5 确保变量被正确转换

MATLAB是一种顺序执行代码,众所周知,HDL代码是并行执行的代码。为了能让MATLAB代码成功的转换为HDL模型,就要确保MATLAB用到的变量也能正确的转换(原文档描述为Variable Availability)。具体来讲就是要保证所有的变量在MATLAB语法的不同分支条件下都能够得到赋值。

ug958给出了一个示例代码:

function [x, y, z] = test1(a, b)

x = a;

if a>b

x = a + b; y = a;

end

switch a

case 0

z = a + b;

case 1

z = a - b;

end

其中y变量只在“if a>b”的条件下赋值,而不清楚另一种情况下怎么办;z变量在switch的其它情况下也不知道该怎么办(switch没有otherwise)。在执行时MATLAB都会报错。x变量虽然也没有在if对应的else条件中赋值,但其已经提前赋值“x=a”,这样在else时会默认保留原值,该变量满足Variable Availability。

---------------------

作者:碎碎思

来源:CSDN

原文:https://blog.csdn.net/Pieces_thinking/article/details/83693008