要做无线通信,必定会接触到傅里叶变换,要做傅里叶变换肯定会接触到IFFT变换,它将傅里叶变换的乘法和加法次数极大的缩减,而且在xilinx的IP中有关于IFFT的核,直接调用它可以缩短开发流程。

下面开始讲解vivado关于IFFT的IP核运用步骤:

1.要运用IP首先的明白几个参数

1).配置通道参数(s_config_valid/s_config_data/s_config_ready)

s_config_valid:拉高时表示配置参数有效。

s_config_data:配置参数(我们选取run simulatiom啥玩意,所以它只包含(PAD scl_scale FWD_INW PAD cycle前缀),SCL_SCALE表示缩放因子,毕竟你的IFFT经历那么多次乘法,加法,你的位宽的变,所以必须缩小,缩小多少具体情况,具体分析(后面会阐述),另外就是FWD_INW=1;表示FFT变化,=0表示IFFT变化,循环前缀根据你的需要)。

s_config_ready:表示从机做好了数据接收的准备,可以发数据了,只有

s_config_valid和s_config_ready同时有效时,数据才配置成功。

数据信息(s_data_valid/s_data_ready/s_data_tdata)

s_data_valid/s_data_ready:与上述内容差不多。

s_data_tdata:输入的数据,位宽由自己确定(低位表示实部,高位表示虚部)。

3.变换后数据输出(m——-乱七八糟)

跟上面差不多

废话不多说了,说一下调试过程,蛋疼。。。

重点1:你的s_config_valid在s_config_ready拉高后的一个时钟周期拉高,你的s_config_data可以从上电就保持有效,谨记s_config_valid只需要拉高一个时钟周期即可,但是这个时钟周期的保证你的配置数据有效的。

重点2:如果你插入了循环前缀,那么你在拉高s_data_valid之后(具体多少个时钟周期,由你输入的IFFT点数决定),你必须拉低循环前缀个数那么多个时钟周期(比如16个循环前缀,你就拉低16个clk)这个超级重要,否则时序不对。

重点3:你必须保证你送进去的有效点数真的有IP核设置的那么多个,否则时序会出错,因为IP无法识别。

重点4:记住送入IFFT的IP核数据(实部和虚部都是二进制补码的形式),即16QAM映射结束之后送入IP核中的数据都是补码,输出当然也是。

重点5:具体的仿真思路:

谨记不要去拿FPGA仿真后的数据去与MATlab输出的数据去做结果比对,对的你怀疑人生。。。。

首先,利用matlab产生一个正弦波,选取其中64个点作为实部

记住这64个点是浮点形的数据,将这64个点在matlab里做FFT变换,然后输出64个浮点数据,因为FPGA是以二进制补码形式输入,所以在matlab中进行浮点转二进制补码的变换。然后将变换后得到的数据送入FPGA的IP核中做IFFT变换,这时IFFT输出的数据格式也是二进制补码形,所以在把输出的数据给MAtlab做二进制补码转浮点形数据,把这个浮点形数据与送入MATlab之前的64个浮点形数据做比较,相等则结果对。

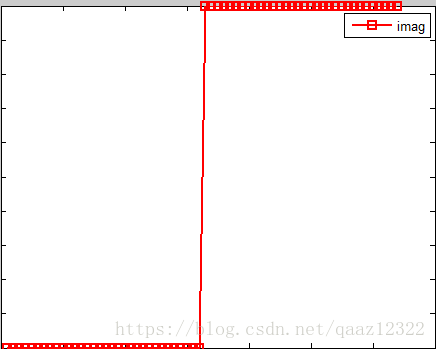

上面说的是实部,虚部我们就用一个方波吧,这里写图片描述

原理与实部变换相同。

以下是FPGA做完IFFT变换后,输出的64个数据

可以看出右边为虚部,只有两个形同的数据1111111111100和000000000011),右边则为64个正弦波数据,导入matlab中,产生的波形一比较,就知道结果了,(关于具体的缩减因子也是在这里调试的,根据FPGA输出的数据与MATLAB输入的数据做波形比较,根据幅度值来调节具体的缩减因子)。。。。。。结束。。

博文转载自:https://blog.csdn.net/qaaz12322/article/details/79935950