作者:碎碎思 来源:OpenFPGA微信公众号

概述

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

从时间阶段可以分为两部分,第一阶段是从FPGA上电开始直到配置(Configuration)完成之前。第二个阶段是配置完成之后,FPGA开始正常工作开始。

从引脚类型上分,可以分为三大类:第一类是普通的IO,其中又分为程序设计中使用到的IO和程序设计中没有使用的IO(即在ucf或者XDC文件中没有进行约束的IO);第二类是专用下载配置引脚(Dedicated Pins),这类引脚只用于专用的功能,包括有M[2:0]、TCK、TMS、PROGRAM_B、INIT_B等。第三类为功能复用引脚,这类引脚在使用特定的功能时使用,例如在使用BPI配置模式时,D[00-31]和A[00-28]需要使用。如果使用SYSMON时,I2C_SDA和I2C_SCL需要使用。但在当前没有使用该功能的情况下,功能复用引脚可以看成普通IO。

FPGA IO的基本结构

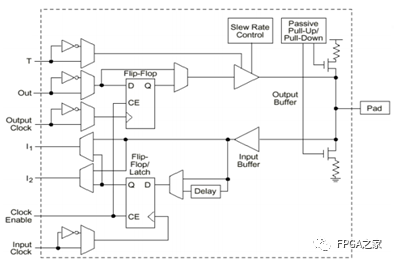

在《IO输入输出的各种模式》介绍了处理器IO的各种输入输出模式以及原理,那么FPGA的IO是什么样的结构和原理?图 1为Xilinx文档中提供的IOB的内部结构,可以看出:

在FPGA IOB内部,Pad输出之前,内置上下拉电阻。且可以通过Passive Pull-up/Pull-down模块控制两个MOS管的导通与否来控制是否使能上下拉电阻。

内部连接Pad的分别有一个Input Buffer和Output Buffer。其中Input Buffer对外应该始终呈现高阻状态,同时可以将Pad上的电平通过Input Buffer传到I1和I2,或者是下部的FF。Output Buffer有两个控制信号,分别是Slew Rate Control,用来控制输出信号的Slew Rate;另一个是三态控制信号T,可以控制Output Buffer输出高阻。

内部输出信号Out,可以通过上半部分的FF,经Output Clock同步后打出,也可以直接连接到Output buffer的输入端,直接输出。

同样Input Buffer的输出,可以直接连接到I1和I2,也可以经过下半部分的FF,经过input clock的同步之后输出到内部总线上。

上下两个MOS并不是推挽输出的两个MOS管,因为并不受到互补信号的控制,并不一定一个导通另一个闭合。

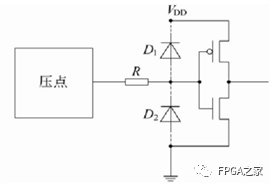

这里介绍一下输入缓存器的结构和原理,其结构如图 2所示,其原理与推挽输出电路非常类似,只是输入端信号作为了两个互补MOS管的控制端,控制着输出端的电平。由于输入缓冲器有自己的供电电压,所以输入电平必须与缓冲器的电源电压相匹配。D1和D2两个钳位二极管用于防治输入电压过低或者过高,损坏输入缓冲器。

普通IO

配置完成之前

在FPGA上电到配置完成之前,由于当前FPGA还没有下载程序,无法区分哪些引脚被设计所使用,哪些引脚没有被使用。此时的普通IO包括两部分:

该封装中所有的通用IO引脚。

当前所选择的模式下没有使用到的所有功能复用管脚。

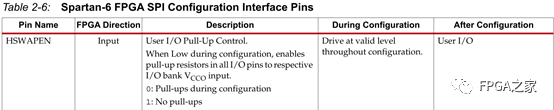

在Spartan6系列以及之前的器件中这些引脚的状态是根据HSWAPEN的状态决定的。

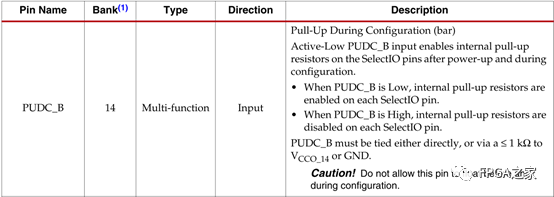

在7系列以后的器件,包括Ultrascale器件中,这些引脚的状态是根据PUDC_B(Pull-Up During Configuration)引脚

这两个引脚的功能是相似的,都是用来控制在Configuration完成之前,所有普通IO的上拉电阻是否使能的。对应到图 1中,即Output Buffer输出高阻,Input Buffer对外始终为高阻,此时选择是否连接上拉电阻。

配置完成之后

在配置完成之后,FPGA就进入正常工作的模式了。在配置完成之后,普通引脚可以分为以下两种:

工程设计中使用的IO,即在UCF或者XDC中有明确约束的IO。

其余没有使用,也没有约束的IO。(称为Unassigned Pins)

首先,对于第一种情况,由于已经在设计中明确设定了这些引脚的设置,包括方向、电平、驱动能力等等,所以在配置完成之后,这些引脚的状态已经被设置为了预设的状态。

对于没有约束的IO,又复杂一些了。在ISE开发环境下,工程完成Implement之后,在Processà Process properties àConfiguration Options中有"-g UnusedPin Unused IOB Pins"属性,可以选择Pull Down、Pull Up或者Floating。默认状态是Pull-Down。对应到图 1中,是高阻输出,导通下拉电阻。另两个设置就是高阻加上上拉电阻或者只是上下拉电阻均不导通。

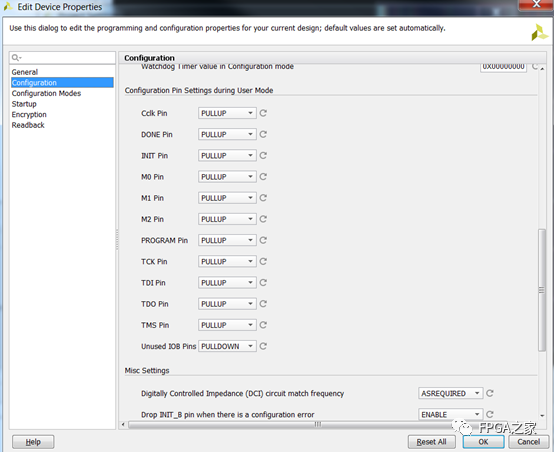

在Vivado中也有相同的设置,必须在实现完成之后,打开Implementation Design之后选择bitstream Settings,其中在"Configure additional bitstream settings"中的Configuration栏中,有如下属性选择项。

专用IO

所有的专用配置引脚全部位于Bank0,包括CFGBVS、M[2:0]、TCK、TMS、TDI、TDO、PRORAM_B、INIT_B、DONE以及CCLK。专用引脚的含义就是无论在配置过程中还是配置完成之后,这些引脚无论在什么阶段都只用于配置。

所以对于这些引脚考虑相对比较简单,分为输入信号和输出信号。输入信号的状态始终保持LVCMOS电平标准,电压值为VCCO(输入信号为什么也有电平标准要求,需要与Input buffer的供电电压相匹配,见图 2)。输出信号的状态始终保持LVCMOS电平标准,电压为VCCO,12mA drive,fast slew rate。

功能复用IO

相比于其他引脚,功能复用引脚的情况是最复杂的,这些管脚包括与配置相关的PUDC_B、EMCCLK、CSI_B、CSO_B、DOUT、RDWR_B、D00_MOSI、D01_DIN、D[00-31]、A[00-28]、FCS_B、FOE_B、FEW_B、ADV_B、RS0以及RS1;以及与System Monitor相关的AD0P至AD15P、AD0N至AD15N,I2C_SDA以及I2C_SCLK。

为了说清楚功能复用管脚在不同阶段的状态,将复用管脚分为以下几类:

在当前所选择的功能中使用到的功能复用管脚,例如在选择BPI配置时的D[00-31]和A[00-28]。

在当前所选择的功能中没有使用到的功能复用管脚。例如在选择SPI配置时的D[00-31]和A[00-28]。

在完成配置之前需要作为输出或者双向,总之有可能向外输出信号的管脚,例如I2C_SDA和I2C_SCLK。

配置完成之前

在FPGA上电至配置完成之前的这段时间内,前面列出的第一类引脚,即在当前所选择的功能中使用到的功能复用管脚,状态等同于专用配置IO管脚。输入信号的状态始终保持LVCMOS电平标准,电压值为VCCO。输出信号的状态始终保持LVCMOS电平标准,电压为VCCO,12mA drive,fast slew rate。

前面列出的第二类引脚,即在当前所选择的功能中没有使用到的功能复用管脚,视同于普通IO,其状态受到HSWAPEN或者PUDC_B信号的控制,决定是高阻还是连接弱上拉电阻。

第三类引脚的情况比较复杂,目前所知的只有I2C_SDA和I2C_SCLK,这两个信号会在配置完成前出现一些不确定的状态。所以如果FPGA的IO还有富余,并且要求所有连接到外部的引脚有确定的状态,那么最好不要使用这两个引脚作为连接外设的IO。

配置完成之后

在FPGA配置完成之后,前面提到的三种引脚会被分成另外三类:

第一类是在用户设计中明确配置了需要保留的功能引脚,例如对于配置相关的引脚设置了Persist option属性,这种情况下这些引脚会继续保持之前与配置相关的功能,其状态为输入信号的状态始终保持LVCMOS电平标准,电压值为VCCO。输出信号的状态始终保持LVCMOS电平标准,电压为VCCO,12mA drive,slow slew rate。再例如设计中使用了SYSMON,I2C_SDA和I2C_SCLK引脚则继续保持DRP I2C的功能。

第二类是在用户设计配置中没有要求保留其特殊功能,这些引脚在配置完成之后会变成普通IO,且在用户设计中没有使用到的IO。这些IO相当于Unassigned IO,如前所述,这些IO在配置完成之后的状态受到相应设置的影响,可以是上拉、下拉或者Floating。

第三类是在用户设计配置中没有要求保留其特殊功能,这些引脚在配置完成之后会变成普通IO,并且在用户设计中使用到的IO。这些IO的状态由用户设计控制,会在XDC或者UCF中设定。如果没有设定就会按照默认的状态,输入端口默认状态为LVCMOS电平标准,电压值为VCCO;输出信号默认状态为保持LVCMOS电平标准,电压为VCCO,12mA drive,slow slew rate。