本文转载自:数字IC-FPGA大叔博客

时钟就是脉搏,能否工作全靠它!

话不多说,直接上干货!

文中全部使用GTX代指GT Transceiver,同样适用于GTH。

一、参考时钟

1.1 收发测试能跑起来的基本参考时钟设置

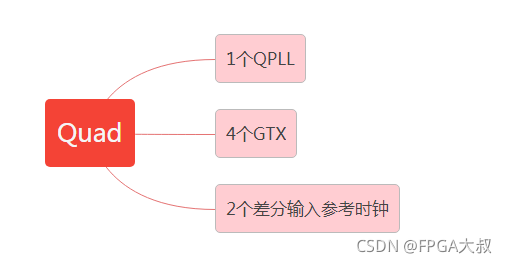

我们先回顾下上一节的基础知识:Quad、QPLL、CPLL、Channel、Common;基础知识理解了有利于后面内容的了解。

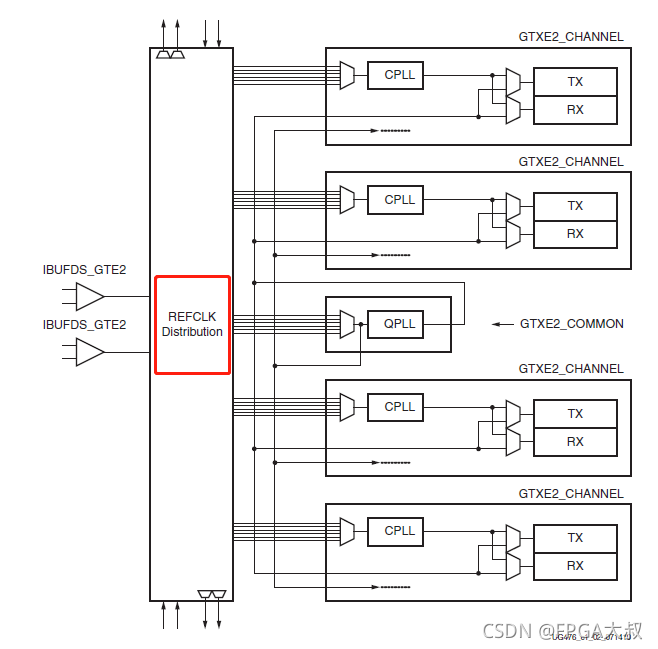

每一个GTX独有的CPLL,4个GTX共有的一个QPLL,2个外部参考时钟输入,和专用参考时钟布线(REFCLK Distribution)。

在Quad中,GTXE2_CHANNEL原语以及GTXE2_COMMON原语都必须例化,需要注意的是不管使用还是不使用QPLL,GT_COMMON都是要例化的,这是工具自动操作的。

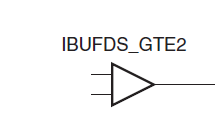

外部参考差分时钟输入经过 IBUFDS_GTE2原语转为单端时钟后,就是GTX的参考时钟输入端口:

IBUFDS IBUFDS_inst (

.O(O), // 1-bit output: Buffer output

.I(I), // 1-bit input: Diff_p buffer input (connect directly to top-level port)

.IB(IB) // 1-bit input: Diff_n buffer input (connect directly to top-level port)

);

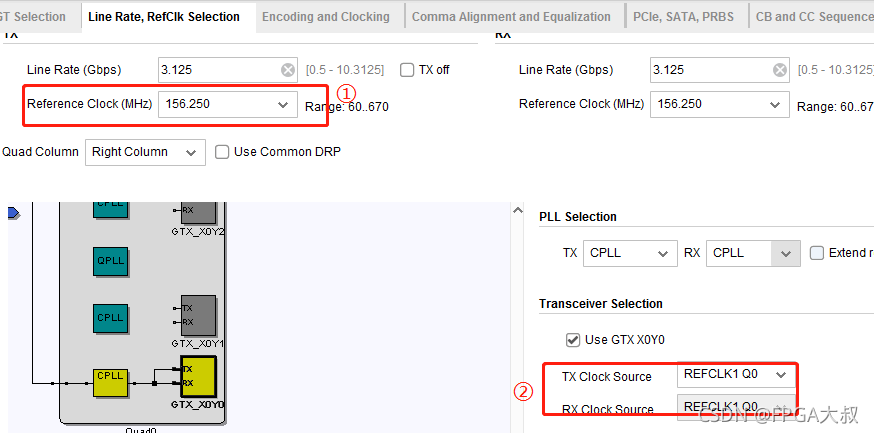

前文已说过,1个Quad有2个参考时钟,我们称之为REFCLK0,REFCLK1,具体用哪一个,看你外部板卡设计时,实际给了哪一路。然后在IP配置时候,选择使用对应的参考时钟:

总结如下:

①参考时钟根据板子实际时钟来选择频率;

②参考时钟给到REFCLK0 还是REFCLK1也由板子设计决定。

但是对于我们学习做仿真而言,暂时不用管它;如果按照上图配置来例化IP;那么对应到程序中就是:

(根据IP配置)差分输入参考时钟频率为156.25Mhz,然后经过IBUFDS原语后转为单端时钟并给到参考时钟REFCLK1;而REFCLK0由于没有使用,直接给0 。

1.2 继续了解时钟,走着

如果只是测试收发,跑跑仿真,那么到这里,我们就可以不用继续研究了。直接跳到第二章--系统时钟。但是GTX的时钟远不止如此;要知道K7325T有16个GTX ,V7系列更多;当GTX数量多了的时候,时钟又如何设定?

继续上图:

注意到红框的REFCLK Distribution了吗?专用参考时钟布线。

REFCLK Distribution的上下参考时钟引脚分别为南北时钟输入引脚。用于Quad之间共享参考时钟;也就是说,并不一定每一个Quad都需要外部参考时钟,有的Quad可以和其他Quad共享参考时钟,而共享的来源就是南北时钟输入引脚。Quad的南北参考时钟称为GTSOUTHREFCLK以及GTNORTHREFCLK。

我们再继续看来自QPLL参考时钟的4通道结构图:

又总结一下:

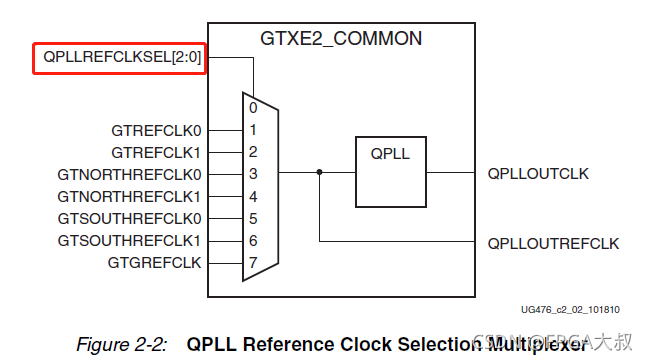

每个Quad中的GTX通道有6个可用的参考时钟输入:

两个外部输入参考差分时钟,经过IBUFDS后就是GTREFCLK0和GTREFCLK1;

来自于Quad上面的两个参考时钟引脚对,GTSOUTHREFCLK0和GTSOUTHREFCLK1;

来自于Quad下面的两个参考时钟引脚对,GTNORTHREFCLK0和GTNORTHREFCLK1;

好家伙,一下子来这么多参考时钟,GTX都蒙了,用哪个呢?

时钟多路选择器安排呗。

下图是QPLL参考时钟多路选择器:

注意:多了一个GTGREFCLK,这个时钟是由内部逻辑产生的参考时钟。貌似只用于内部测试。

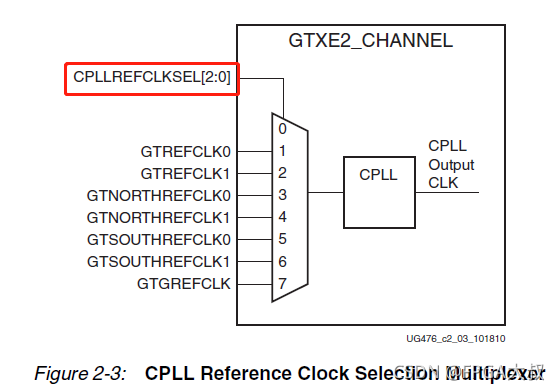

CPLL同理,就不啰嗦了,直接上图:

1.3 单个外部参考时钟使用情形

(1)单个外部参考时钟驱动单个Quad中的多个GTX

这种情况很简单,也很常见,一个Quad共用一个外部参考时钟,直接看图:

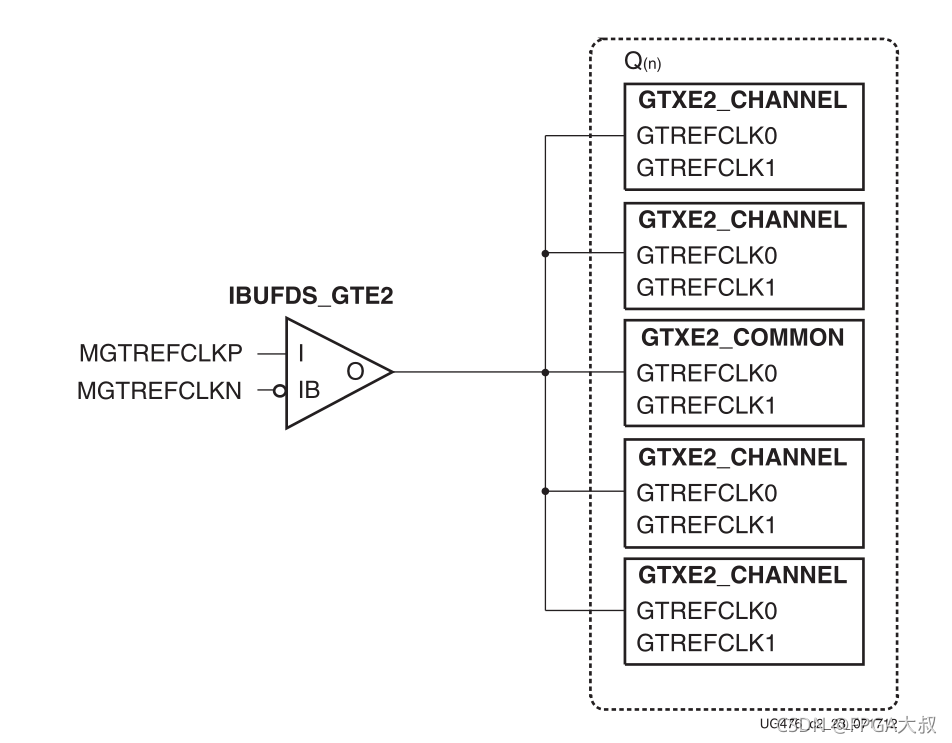

用户设计直接将外部参考时钟经过IBUFDS_GTE2输出REFCLK连接到GTX 的COMMON 、CHANNEL 原语。

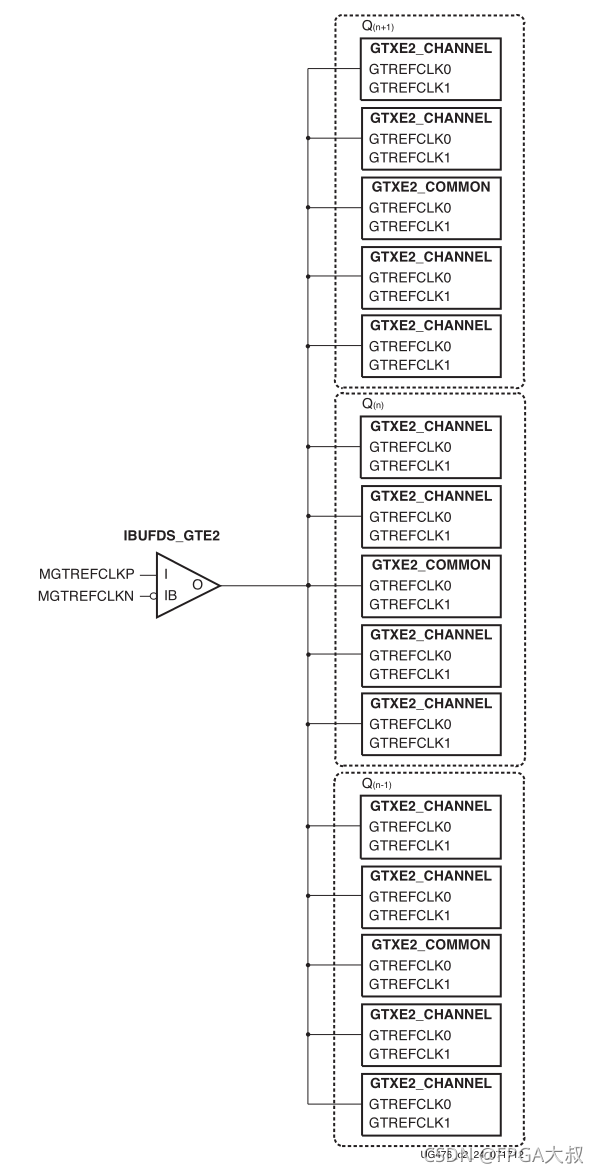

(2)单个外部参考时钟驱动多个Quad中的多个GTX

单个外部参考时钟也可以驱动多个Quad中的多个GTX,例如:

但是,须得遵守一定的规则:

源Quad上方的Quad数量不能超过1个;

源Quad下方的Quad数量不能超过1个;

源Quad,指的是直接连接到外部参考时钟的Quad。

即是说: 1个外部参考时钟所驱动的Quad总数不超过3个,或驱动的Transceiver不超过12个。

1.4 多个外部参考时钟使用情形

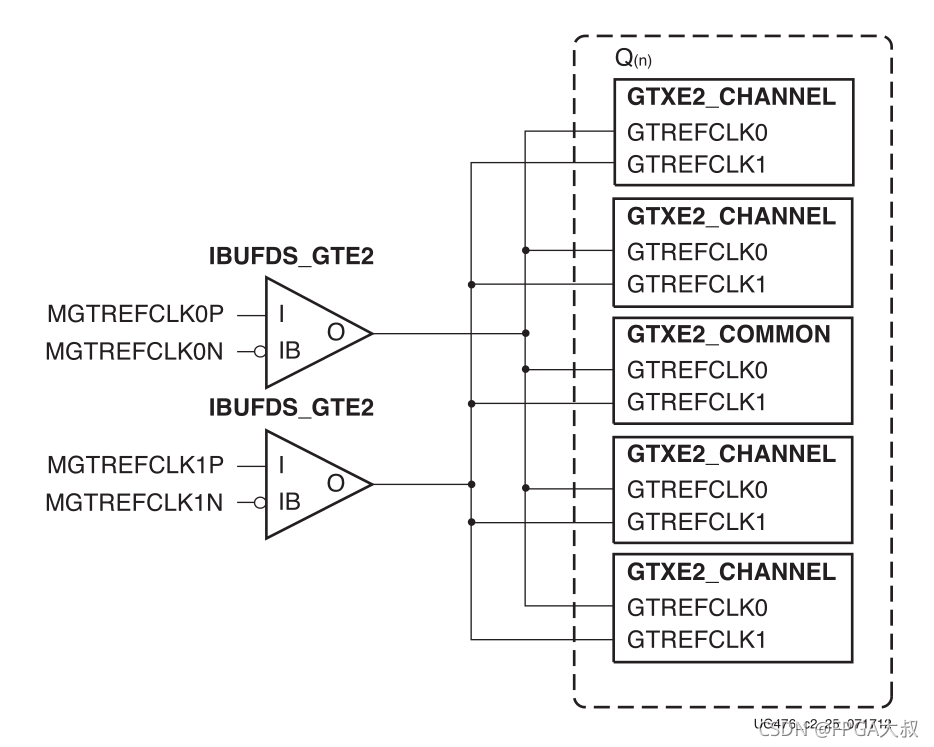

(1)同一个QUAD中,多个GTX Transceiver使用多个参考时钟

每个Quad有两个专用的差分时钟输入引脚(MGTREFCLK0[P/N]或 MGTREFCLK1[P/N]) ,可以连接到外部时钟源。 每个专用的参考时钟引脚对输入进来后必须例化IBUFDS_GTE2,再给到GTX使用。

说再多也不如一张图看的直接:

看图说话:MGTREFCLK0[P/N]连接到GTREFCLK0,将MGTREFCLK1[P/N]连接到GTREFCLK1管脚。

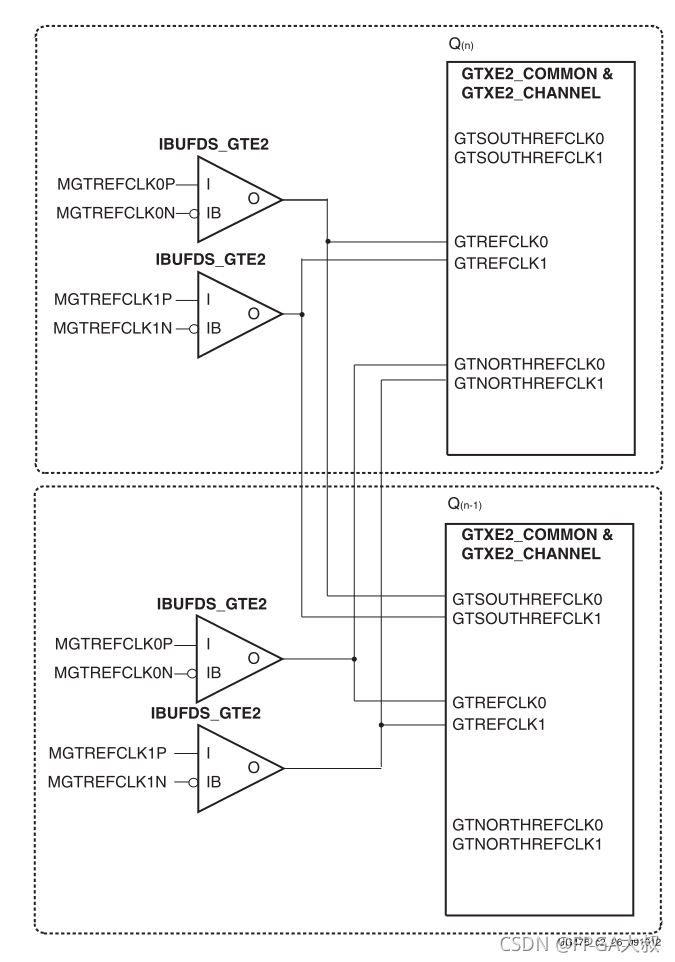

(2)不同QUAD中,多个GTX Transceiver 使用多个参考时钟

参考时钟选择结构的灵活性允许Quad中的每个Transceiver都可以访问上下Quad中的专用参考时钟。

不啰嗦,上图上图:

在每个GTX有多个参考时钟选项的情况下,设计的时候根据需求设置 QPLLREFCLKSEL[2:0]和CPLLREFCLKSEL[2:0]。该遵守的规则还是要遵守的:1个外部参考时钟所驱动的Quad总数不超过3个,或驱动的Transceiver不超过12个。

1.5 QPLL/CPLL工作原理

算了, 略过吧,有兴趣具体查阅手册《UG476》。

二、系统时钟

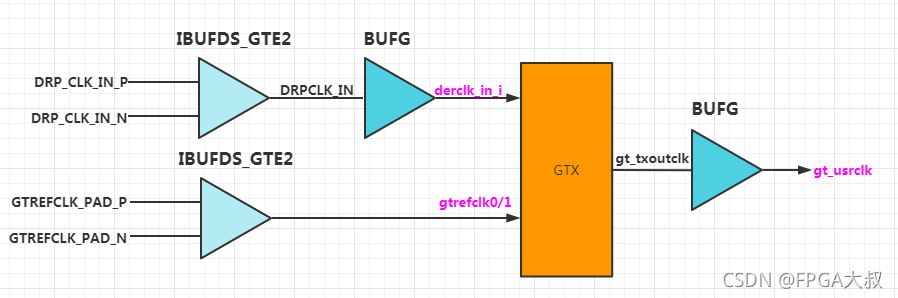

对应IP设置的第三页,我们所设置的时钟频率,也是DRP CLOCK;跟板子提供的时钟对应;

对应到代码:

input wire DRP_CLK_IN_P,

input wire DRP_CLK_IN_N,

我们参照Example Design中对该时钟的处理:

先经过IBUFDS转为单端时钟,然后经过BUFG,再给到GTX核。

IBUFDS IBUFDS_DRP_CLK (

.I (DRP_CLK_IN_P),

.IB (DRP_CLK_IN_N),

.O (DRPCLK_IN)

);

BUFG DRP_CLK_BUFG(

.I (DRPCLK_IN),

.O (drpclk_in_i)

);

这里,有个有意思的事情:

笔者使用50Mhz / 100Mhz 输入,最终GTX输出都是OK的,什么原因呢?

三、逻辑使用的时钟

TXUSRCLK 和 TXUSRCLK2 生成:

(以下内容为UG476翻译)

FPGA发送端包含两个并行时钟:TXUSRCLK 和 TXUSRCLK2,

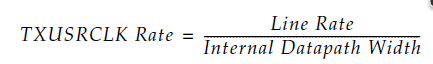

TXUSRCLK是GTX中PCS逻辑的内部时钟。它的频率由TX端的Line Rate和内部数据总线宽度共同决定:

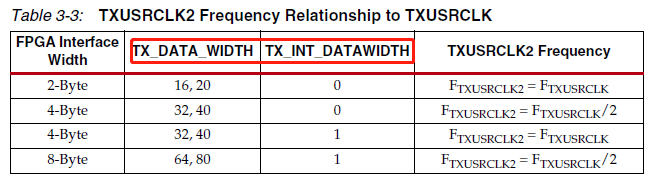

TXUSRCLK2是GTX的TX端信号的主要同步时钟。 GTX发送的大多数信号都是在TXUSRCLK2的上升沿进行采样。TXUSRCLK2和TXUSRCLK之间有一个固定比率关系,由TX_DATA_WIDTH 和TX_INT_DATAWIDTH决定,见下图:

回想一下,我们要通过某个IP核进行发送数据,那么发送数据模块所使用的时钟必然是该IP核出来的同步时钟。

对于GTX而言,我们发送数据所在的时钟域,就是由核输出的gt0_txoutclk_i。

再来看两种情况:

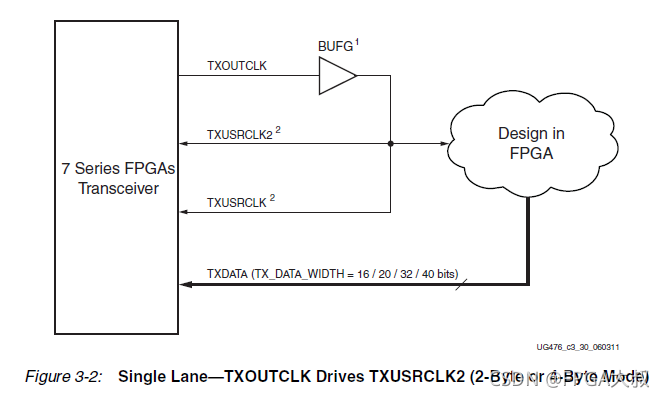

(1)单通道——TXOUTCLK 驱动TXUSRCLK2 (2-Byte 或者4-Byte 模式)

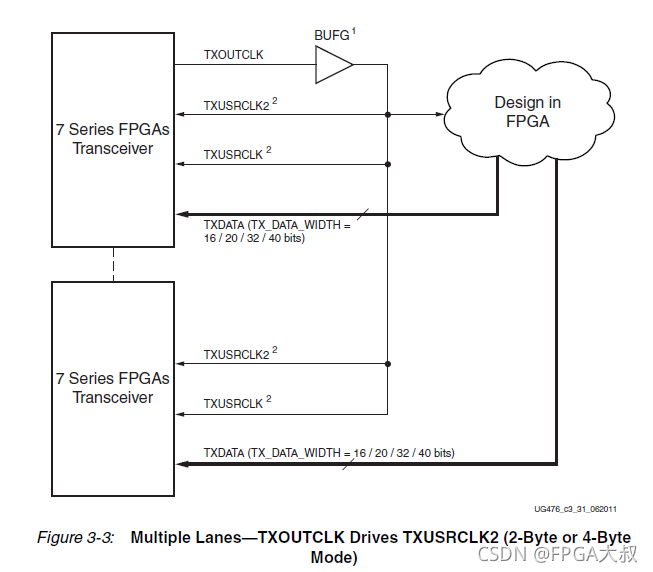

(2)多通道——TXOUTCLK 驱动TXUSRCLK2 (2-Byte or 4-Byte 模式)

四、时钟篇小结

前面解释的很详细了,最后放张图吧。