作者:ShownSun,文章来源: 时沿科技微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

1 DDS技术简介

随着电子技术的不断发展,传统的频率合成技术逐渐不能满足人们对于频率转换速度、频率分辨率等方面的追求,直接数字频率合成技术应运而生。

直接数字频率合成技术(DDS) 是把一系列数据量形式的信号通过D/A转换器转换成模拟量形式的信号合成技术。DDS具有很多优点,比如:频率转换快、频率分辨率高、相位连续、低功耗、低成本与控制方便。

DDS技术满足了人们对于速度稳定性的需求,但是在一些控制较为复杂的系统中,DDS专用芯片不能很好的贴合要求。利用现场可编程门阵列(FPGA)实现DDS具有很大的灵活性,基本能满足现在通信系统的使用要求。

2 DDS结构原理

2.1 基本结构

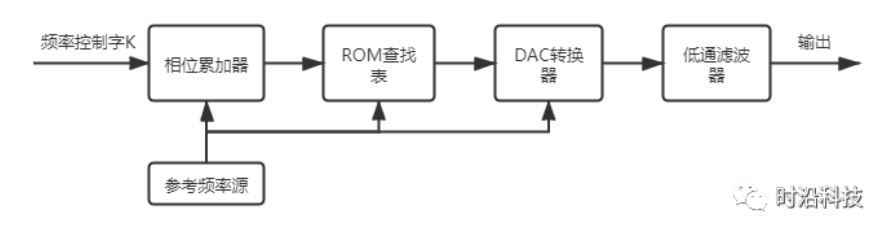

DDS基本结构框图主要由参考频率源、相位累加器、ROM查找表、DAC转换器、低通滤波器等构成。

DDS基本结构框图

相位累加器以一定的步长做累加, 而波形函数存储在ROM查找表中, 将相位累加器输出的相位值作为地址,寻找存储在ROM查找表中的波形函数的幅度值,从而完成相位到幅值的转换。其中,参考频率源一般是一个晶体振荡器,要求具有高稳定性,用于DDS中各部件之间的同步。

2.2 基本原理

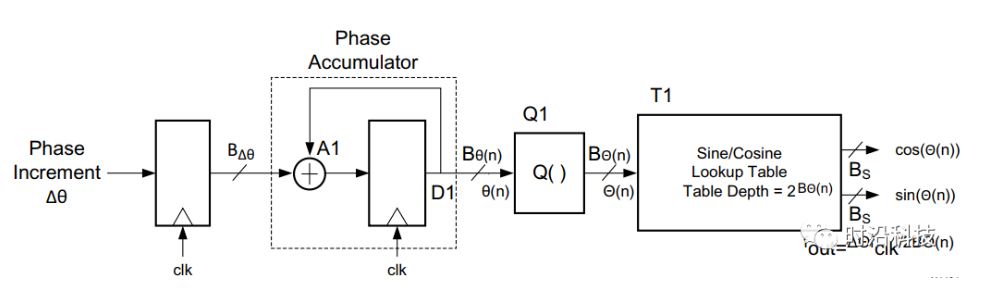

DDS Core结构图

上图为DDS Core结构图,∆θ是相位增量(对应图1中的频率控制字K),B∆θ 为相位累加器的位数,clk是参考时钟(对应图1中的参考频率源),A1、D1构成积分器(相位累加器),θ(n)是相位累加器输出的相位,Q1为量化器,用于将相位累加器位数与查找表地址之间的匹配,ϑ(n)为查找表输入地址,Bϑ(n) 为查找表输入地址位数,T1为查找表。

下面介绍DDS设计过程中常用到的公式,主要是输出频率公式及其变形。

3 基于FPGA的 DDS实现

For example:

设计一个参考时钟为100MHz,频率分辨率要求能够达到0.03Hz,输出sin信号频率为5.00000005MHz、查找表地址12位;

理论分析:

已知频率分辨率∆f与参考时钟f_clk,带入相位累加器位数公式计算

B∆θ = 31.634318

由于位数为整数,取整数32,所以实际的频率分辨率为

∆f = 0.023283064365386962890625Hz

将其带入相位增量公式计算,取整数

∆θ = 21474836694.7483648≈21474836

相位累加器输出32位,而查找表输入地址为12位,取相位累加器高12位作为查找表输入地址

3.1 利用RTL实现DDS

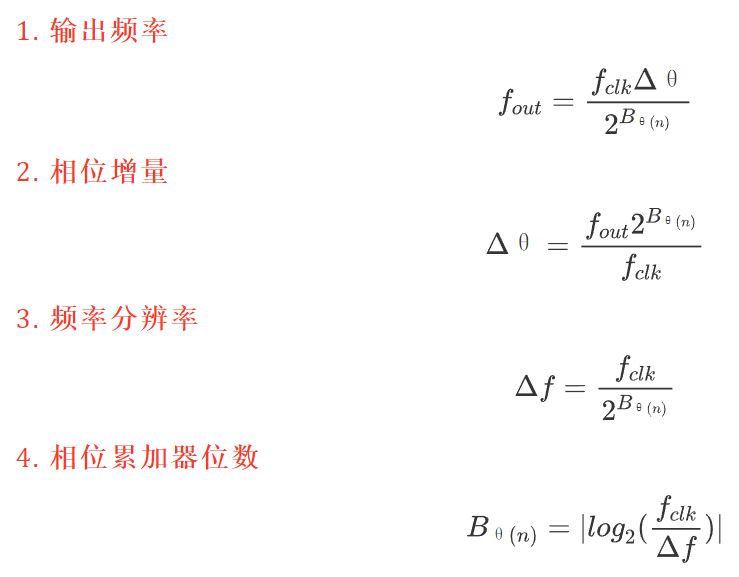

使用matlab产生sin(θ)数据,θϵ[0,π],点数为2^12=4096,并保存在FPGA的memory中。

wid = 12;

len = 2^wid;

amp = 10000;

t=0:2*pi/len:2*pi - 2*pi/len;

y = round(sin(t)*amp);

plot(y);

matlab生成sin信号

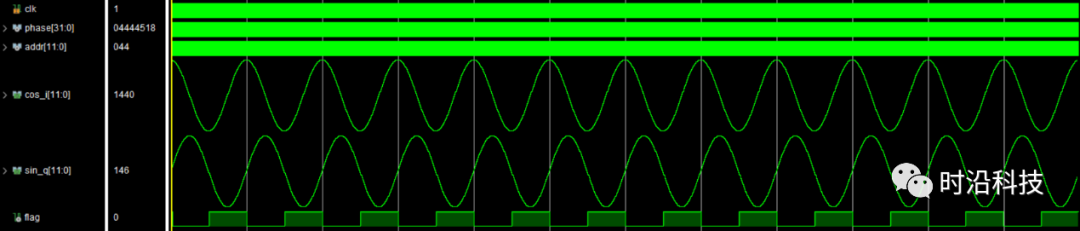

相位累加器就是一个积分器,很容易用FPGA实现。最终FPGA仿真结果如下,clk为参考时钟,phase为相位累加器输出,addr为查找表地址,cos_i、sin_q为信号输出:

DDS RTL仿真波形

3.2 利用Xlinx DDS IP实现

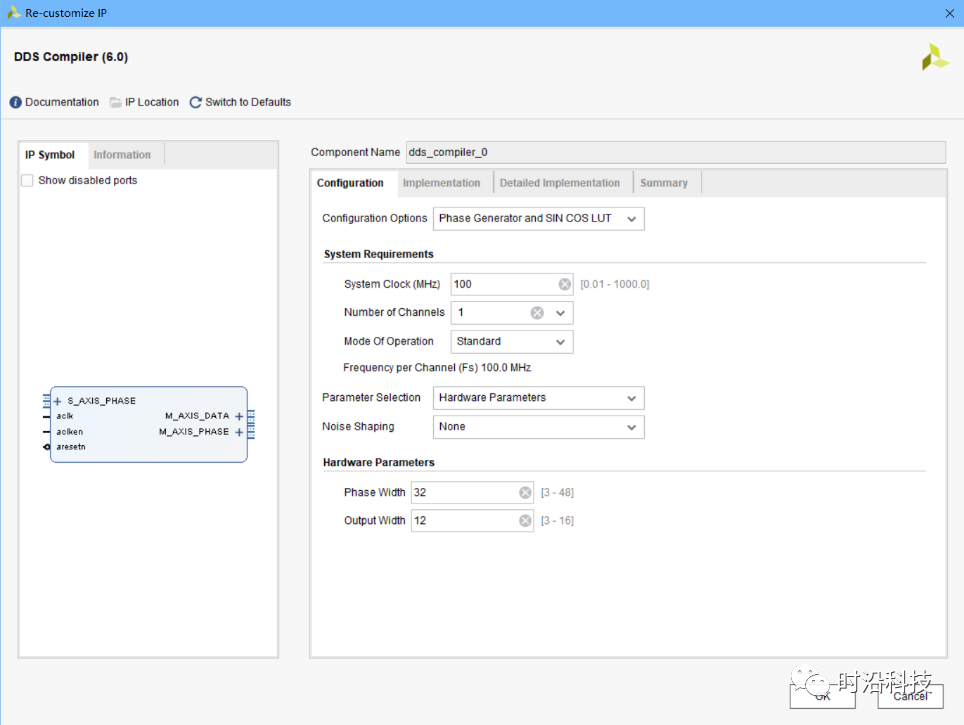

上述已经对DDS理论进行了详细概述,利用Xlinx DDS IP实现上述例子相对容易的多,只需要填入对应的参数信息。

DDS IP配置界面1

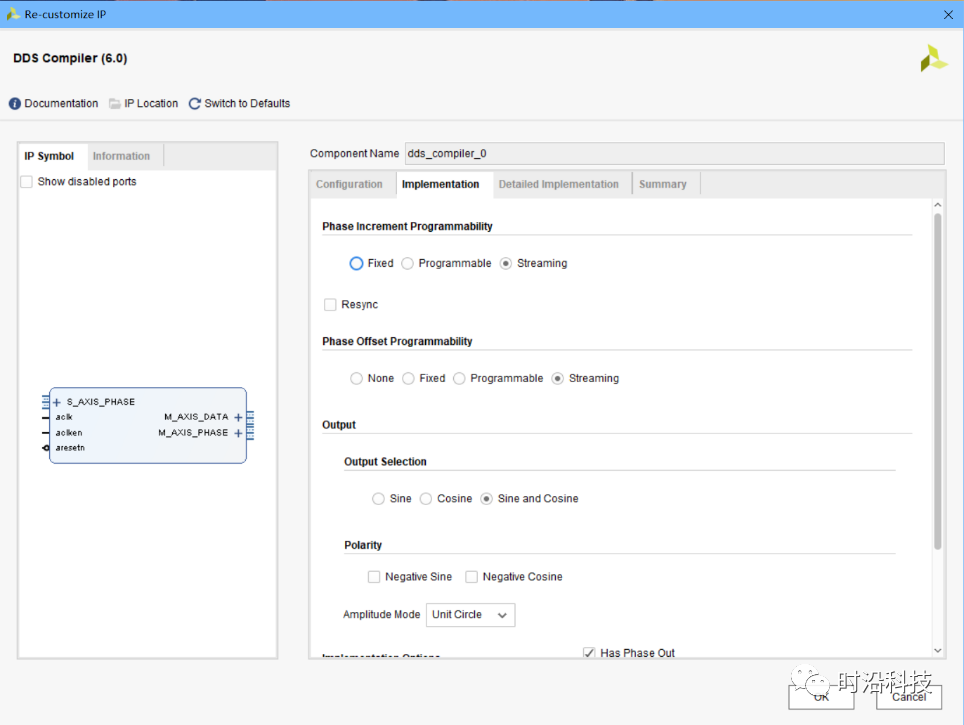

DDS IP配置界面2

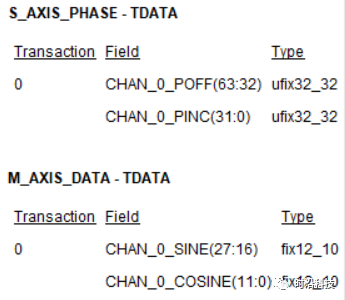

需要注意的是,输入相位端口S_AXIS_PHASE与输出信号端口M_AXIS_DATA的格式,通过设计界面的Information查看,CHAN_0_POFF为初始相位,没有特殊要求一般设置为0,CHAN_0_PINC为相位增量∆θ。

数据端口格式

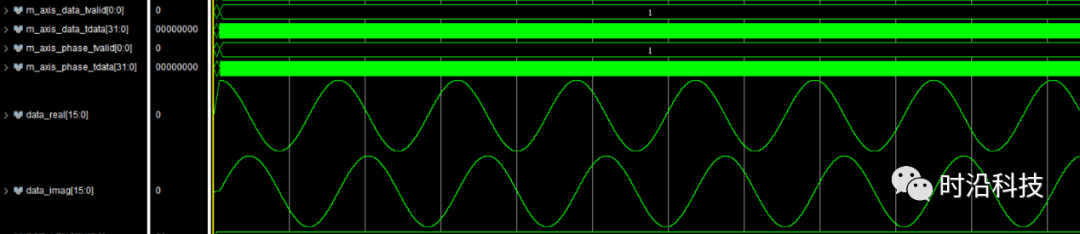

仿真结果如下图所示:

DDS IP仿真波形

4 DDS用途

DDS用途非常广泛,后续会利用Xlinx DDS IP设计一些有趣的信号,例如线性调频信号、非重复扫描系统等。