对FPGA设计而言如果想速度更快则应当努力减少路径上LUT的个数,而不是逻辑级数。如果想面积更小则应当努力减少LUT的个数而不是逻辑门数。

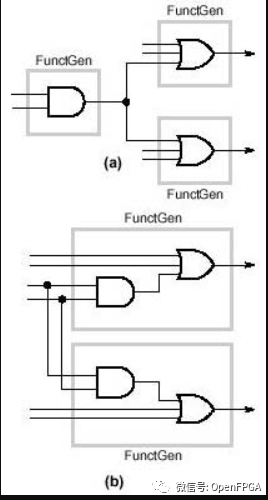

如下图:

采用图a结构,我们知道一个LUT只有一个输出,因此前面的2输入与门要占用一个LUT 后面的2个三输入或门要各占用一个LUT 总共占用3个LUT LUT级数是2级。

采用图b结构,其实现结果等效于图a结构,虽然增加了一个2输入与门并且逻辑级数与图a一样也是2级但我们根据LUT特点它只占用2个LUT:

2输入与门和3输入或门由一个LUT实现LUT级数只有1级,这就是一个门数增加逻辑级数未变但资源占用减少速度更快典型案例。

本文转载自:OpenFPGA