本文转载自:FPGA的现今未

最近在项目中需要使用PCIe接口,可能大家立马都会想到XDMA或者QDMA接口,当然这个对于使用UltraScale器件的人来说还是很友好的。如果你使用的是中低端器件,比如K7系列的器件,考虑到资源、以及一些定制化的功能,就需要自己来处理TLP报文和DMA,一个常见的模型如下图所示:

PCIe core往往是硬core,实现PCIe的物理层、链路层和事务层,完成serdes接口到TLP报文的处理;TLP处理模块则根据TLP层的协议 ,实现拆包和组包;DMA处理模块则实现基于用户需求的DMA协议。

其中TLP处理和DMA处理相对来说是比较难的,TLP处理模块需要实现对TLP拆包和组包的过程、TLP报文的底层协议的处理,尤其是TLP的乱序和排序的处理,这些都是相对比较难的。DMA模块,尤其是高性能多通道的DMA处理也比较复杂,这两个模块对于人员规模不大,积累不够的团队来说,是有一定难度的。

Xilinx有很多不同层次的IP,在Kintex®-7系列的FPGA中,有3个IP:

(1)7 series intergrated block for pci express:这个IP就相当于上图中的PCIe core,用户要组织好memory read和memory write类型的报文和PCIe core进行交互。

(2)axi memory mapped to pci express:如果对于TLP层的处理不太熟悉的话,那这个IP就比较合适了,它屏蔽了TLP协议的处理,通过AXI接口和IP交互数据,这个IP相当于上图中的PCIe core+TLP处理。

(3)dma/bridge subsystem for pci express(pcie):就是xdma,它不但处理了TLP,而且DMA也一起包含在IP中,相当于上图中的PCIe core+TLP处理+DMA处理。

究竟如何选择IP,需要从项目的需求、资源、团队的积累、开发时间等多个方面考虑。考虑到资源和对DMA的特定需求,笔者最近使用了第二个IP:axi memory mapped to pci express。

接口

该IP的接口数量比较多,但是相对比较简单,如下图所示:

axi接口主要是axi_master和axi_slave接口,实现host到FPGA和FPGA到host的读写操作;axi_lite接口是该IP内部寄存器的读写的接口;中断接口是发起msi中断的接口,时钟复位接口是该IP对用户提供的时钟和复位等。

时钟方案

该IP输入参考时钟的频率有多种选择,这里选择100M的差分时钟输入,差分时钟通过一个ibuf_gts变成单端时钟后,输入给IP core的reflk接口。

该IP输出2个时钟,一个是axi_master和axi_slave接口的时钟,axi_aclk_out;另一个是axi_lite接口的时钟,axi_ctl_aclk_out。因此对于整个系统而言,时钟方案就有2种,如下图所示:一个是PCIe时钟域(axi_aclk_out时钟域),在DMA模块做时钟域转换,转成用户时钟域。另一个方案就是整个系统都工作在PCIe时钟域。

考虑到方案和后续移植的灵活性,这里采用上述第一种时钟方案,在DMA模块做时钟域转换,用户逻辑可以根据需求灵活地配置用户时钟。对于gen2*4的配置,PCIe时钟域是125M的时钟,位宽为128bit。

复位

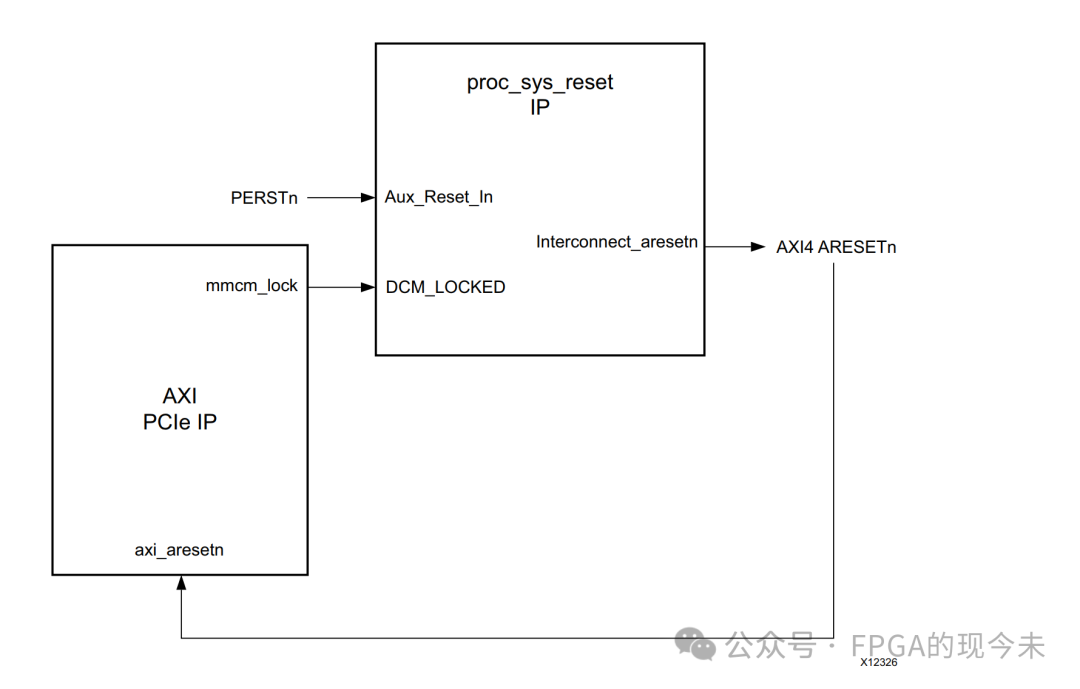

该IP需要一个复位信号来复位整个IP以及GT、PCIe、和AXI接口。在实际应用中,通常情况是不需要对PCIe接口进行复位的,因此该IP的复位条件就只有2个,一个是外部的整板复位信号的复位,另一个就是该IP内部的锁相环失锁的时候,在pg055中,给出了一个复位的参考。如下图所示,通过proc_sys_reset这个IP来产生一个给AXI PCIe IP的复位。该复位就是由外部的复位和AXI PCIe IP的mmcm_lock共同产生。

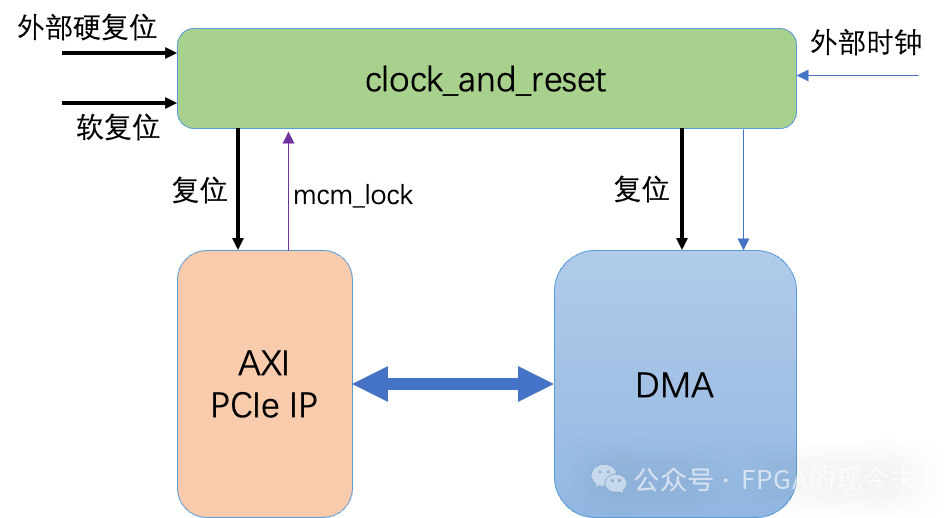

但是考虑到用户时钟域的复位,DMA的复位等,单独采用一个proc_sys_reset IP是不够的,这里采用了另一种复位方案,如下图所示:

外部的硬复位和AXI PCIe IP的mmcm_lock一起产生该IP的复位信号,外部的硬复位和系统时钟的mmcm的lock信号,以及软复位一起产生DMA模块的复位。需要注意的是:当AXI PCIe IP的mmcm_lock信号稳定以后,给它的复位信号还需要保持16个时钟周期。

未完待续……