作者:FPGA入门到精通

DDR4 SDRAM因其高速、大容量的特点,在FPGA设计中扮演着越来越重要的角色。

Xilinx提供的Memory Interface Generator (MIG) IP核,为FPGA与DDR4内存的交互提供了便捷的解决方案。

本文将详细介绍DDR4 MIG IP核及其配置过程。

一、DDR4内存基础

1、什么是DDR?

DDR(Double Data Rate)是一种内存技术,它允许内存模块在系统时钟的上升和下降沿都进行数据传输,因此每个时钟周期可以传输两次数据,就像一条双车道的高速公路,每个方向都可以同时跑车,这样就能比以前单方向的内存(比如SDRAM)传输更多的数据,从而提高了数据传输的速率。

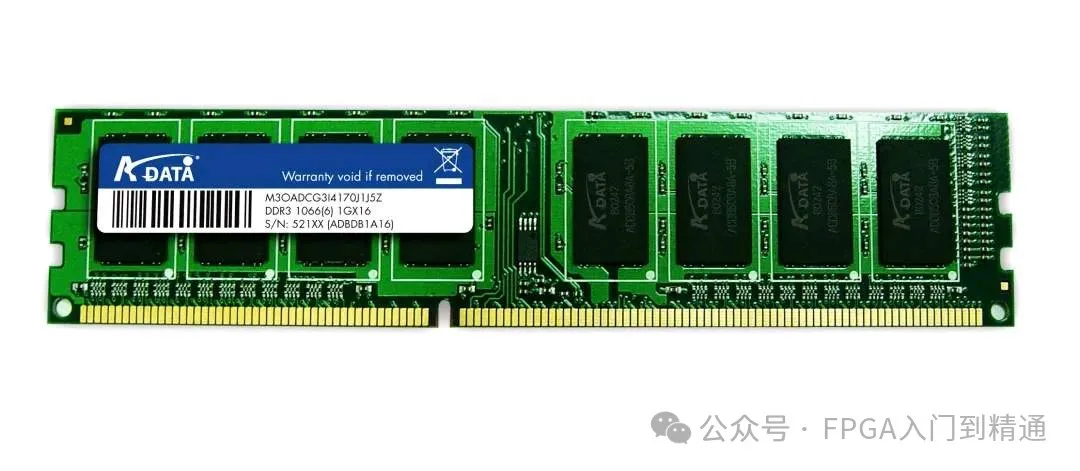

DDR SDRAM(同步动态随机存取存储器)是这种技术的早期版本,随后又发展出了DDR2、DDR3、DDR4和DDR5等多个版本,每一代都在前一代的基础上提供了更高的数据传输速率和带宽,以及更低的功耗和改进的稳定性。

很常见,我们电脑中使用的内存条就是DDR。

2、DDR4与DDR3的区别

DDR4是第四代双倍速率同步动态随机存取存储器,相较于DDR3,它在功耗、核心频率、容量上都有显著提升。

DDR4引入了Bank Group结构,有效降低了读写命令访问不同Bank的时延。

(1)更快的速度和更大的带宽

DDR3:最高支持2133 MT/s(兆传输每秒),实际使用中常见的速度有1333 MT/s和1600 MT/s。

DDR4:起始速度为2133 MT/s,最高支持速度超过3200 MT/s,常见的速度有2400 MT/s、2666 MT/s、2800 MT/s、3000 MT/s等。

(2)更低的工作电压,更低的功耗。

DDR3:工作电压为1.5V。

DDR4:工作电压为1.2V。

二、MIG IP核概述

MIG是Xilinx提供的一个用于自动生成与DDR4内存接口的硬件IP核。

它包括物理层、控制器和用户接口三个主要部分,极大地简化了FPGA与DDR4内存的集成和控制。

1、物理层

与外部DDR4 SDRAM的高速接口,包括高速时钟生成、数据传输、DDR初始化操作和校正操作等等

2、控制器

接收用户的读写命令,并有效传递到物理层,转换为具体的读写控制操作。

3、用户接口

提供给用户简单易使用的接口,有NATIVE接口和AXI4接口两种。

三、DDR4 MIG IP核配置步骤

DDR4 MIG IP核配置操作,比DDR3 MIG IP核配置操作简单很多。

1、打开Vivado项目

启动Vivado并创建新项目。

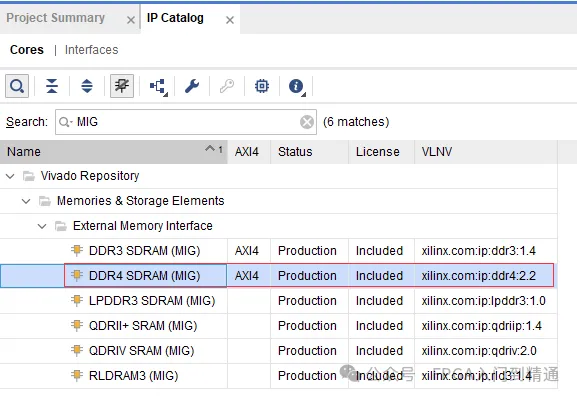

2、添加MIG IP核

在IP Catalog中搜索"MIG",选择DDR4 SDRAM(MIG),然后添加到项目中。

3、Board设置

如果工程选择的是xilinx官方开发板,则会有这个Board设置界面,否则没有。

这里可以选择设置sys_clk和DDR4芯片选择,可选择custom、板载时钟或DDR3芯片型号。

4、基本配置

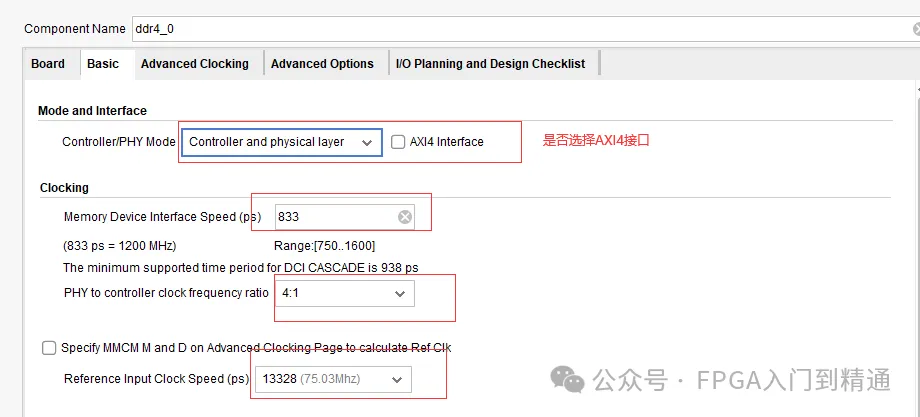

在Basic界面中,设置大部分参数。

(1)Controller/PHY Mode

设置控制器或物理层模式,默认选择Controller and physical layer即可,除非你想自己实现控制器或物理层。

(2)AXI4 Interface

是否选择AXI4接口,勾选表示选择AXI4接口,否则使用NATIVE接口。

(3)Clocking

Memory Device Interface Speed:DDR4内部运行时钟频率设置。

PHY to controller clock frequency ratio:物理层与控制层时钟频率比例,一般选择默认的4:1。

Reference Input Clock Speed:输入参考时钟频率。

(4)Controller Options

Configuration:选择DDR的类型,可选Components、DIMM(双列直插式存储模块)和SO-DIMM(小外形双双列直插式内存模块),一般默认选择Components。

Memory Part:DDR4芯片型号。

Slot:插槽类型,可选单插槽或双插槽,默认选择single。

IO Memory Voltage:io工作电压,默认选1.2v即可。

Data Width:数据位宽,根据实际的DDR芯片组选择即可,这里选择64。

其它几个参数可以不用管。

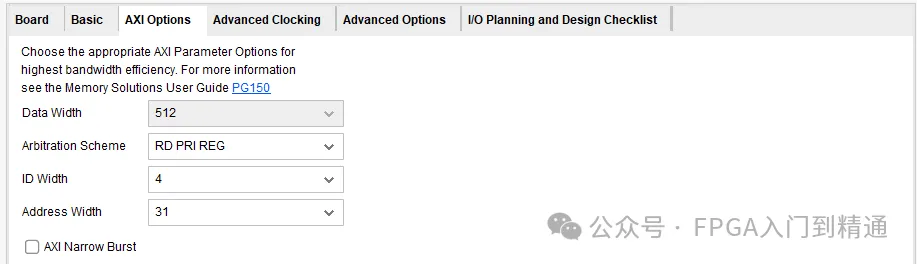

5、AXI Options

如果选择的AXI4接口,会多出一个AXI Options界面,一般默认即可,不需要修改。

Data Width:数据位宽

Arbitration Scheme:仲裁机制,不同的调度策略,默认选择RD PR IREG。

ID Width:ID信号位宽。

Address Width:地址信号位宽。

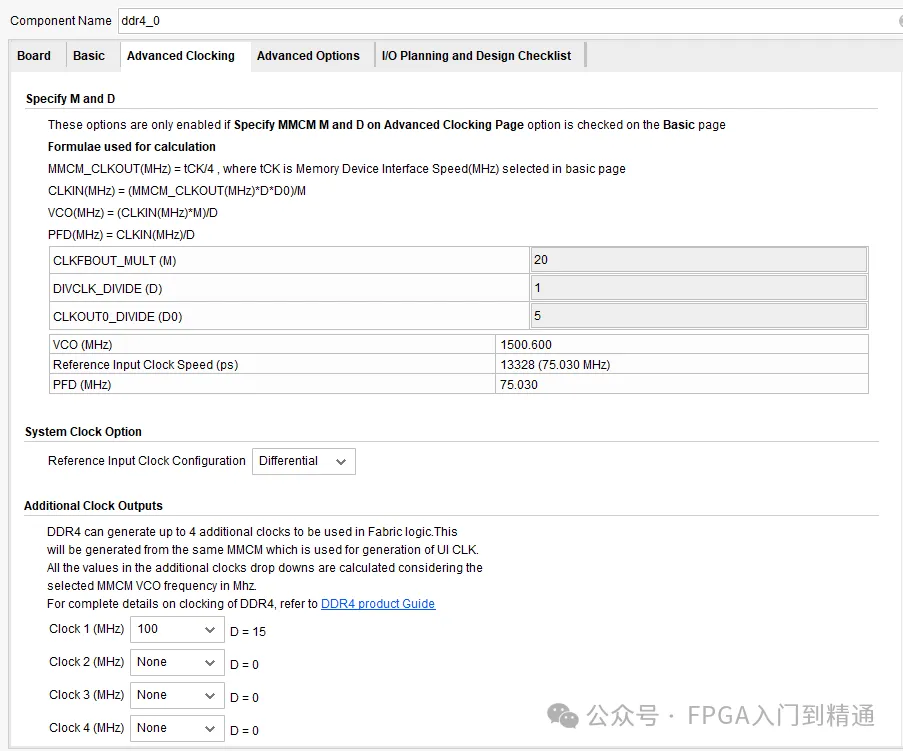

6、Advanced Clocking

根据需求配置额外的用户时钟。

System Clock Options:输入时钟类型选择,可选Differential(差分时钟)或No Buffer。

Additional Clock Output:额外输出4个时钟信号输出,可自定义输出时钟频率。

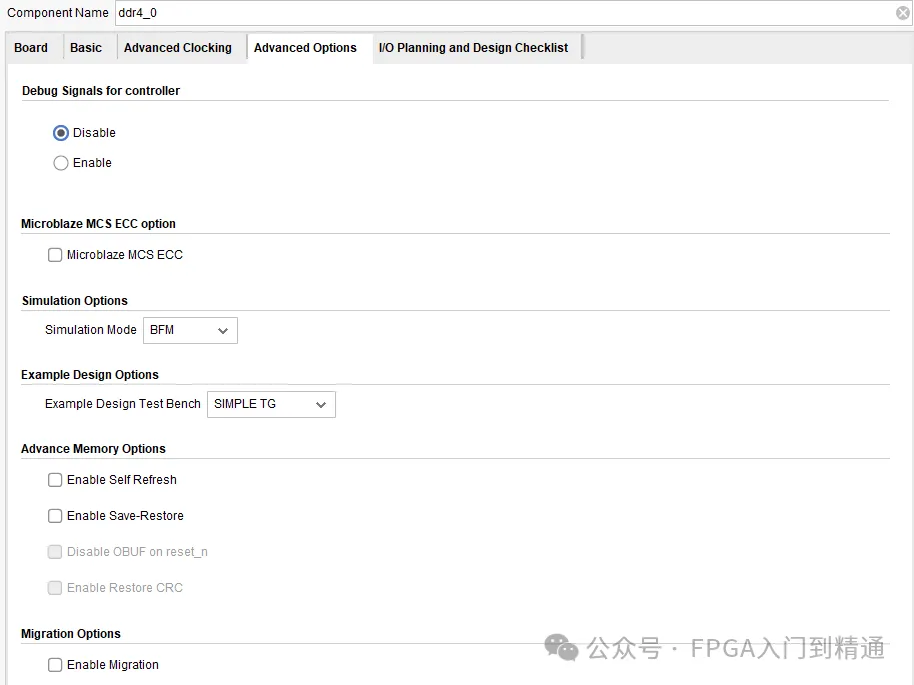

7、Advanced Options

高级选项设置,可设置调试接口信号,仿真测试模式,仿真测试激励,默认即可。

8、IO Planning and Design Check_list

IO引脚分配方式,设计概览清单,无参数设置,了解即可。

四、分析

与DDR3 MIG IP核配置相比,DDR4 MIG IP核配置操作更简单明了。

但大家有没有发现,DDR4( MIG)没有配置引脚约束。

这是因为DDR4的引脚约束,默认放到xdc约束文件中了,大家需要创建DDR4相关的引脚约束文件即可。