文章来源:FPGA的现今未

在使用mig控制器的时候,我们应该怎么仿真呢?关于这个问题其实有2个观点,第一个观点是不需要仿真,一来仿真麻烦,二来仿真的时间非常的慢;第二个观点是要仿真,用来仿真下性能等。最近刚好有项目使用了DDR,并做了一些仿真,做一个总结。

仿真带mig core

为什么要仿真mig和ddr_model呢?当然不是看看xilinx的mig core是否有bug,而是仿真mig的适配逻辑、以及适配逻辑和mig之间的交互机制、还有就是性能等。

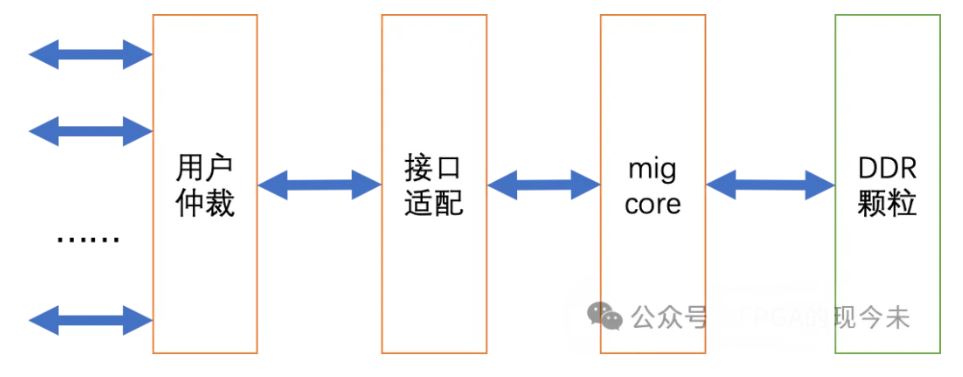

一般的mig core的使用方式,都如下图所示,仿真的时候带上mig core和DDR model,其中ddr model用来模拟DDR 颗粒。

在仿真mig core和DDR model的时候,有2个方面值得关注:

(1)、充分借鉴IP自带的仿真平台,它在example design的sim目录下。以VCS为例,找到对应的编译文件,在里面可以看到仿真的时候,编码了mig core的哪些文件。在我们自己的仿真平台的仿真文件列表中,把这些文件修改路径后copy过去即可。另外还有ddr_model和ddr_model_parameter这2个文件的使用,也可以“抄”example design。

(2)、就是mig core和ddr_model的例化,我们知道在例化的时候要接上时钟和复位等接口。如何连接,以及如何给激励,除了结合user guide的说明外,还可以“抄”仿真的顶层文件和工程的顶层文件。

在仿真mig的时候,首先是关注输出信号init_calib_complete,只有这个信号拉高后才表示初始化完成,即mig可以开始使用。如果没有拉高,一般情况下都是给mig输入的时钟或者复位信号有问题,比如时钟的频率,复位信号的极性等。

仿真不带mig core

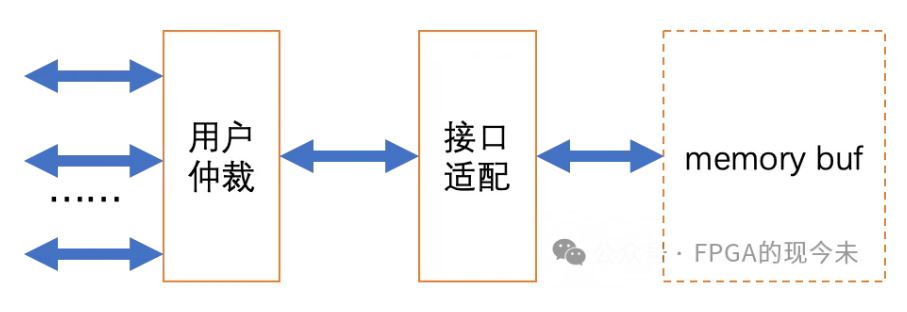

带mig仿真的最大问题就是太慢太慢……,而我们仿真的重点又是在适配逻辑等其他逻辑的时候,我们也可以考虑不带mig core仿真。最简单的方法就是模拟一个大的memory buf缓存,如下图所示:

memory buf采用mig core用户侧同样的接口,比如axi4接口或者native接口。buf的大小,根据项目的实际情况进行调整。我们以256bit位宽为例,假定深度为16K,即memory buf就是一个256bit*16K的ram,按照mig的用户侧接口要求对该ram实现读写即可。当项目中对buf的需要比较大的时候,比如需要1M的深度,可以参考这篇(仿真memory超过限制问题)中关于ram的使用。

这里也要注意2个问题,第一个问题就是这个memory buf也可以在内部产生一个init_calib_complete信号来模拟上电后不能立刻读写的场景。第二问题就是适配逻辑的工作时钟,也应该由这个memory buf模块来产生,而且最好和系统时钟是异步的,这样才能更好的模拟mig core的异步时钟域。

总结

在带ddr的项目进行仿真的时候,可以遵循一个简单的原则,对于和mig相关的用例,比如性能用例等需要带mig和ddr model来仿真,其他和mig不相关的功能用例,可以不带。