文章来源: FPGA入门到精通

DDS技术,即直接数字合成技术,是一种先进的频率合成方法,它在数字信号处理和硬件实现方面发挥着重要作用。这一技术以其低成本、低功耗、高分辨率和快速转换时间等优势而受到青睐。

本文将深入探讨基于FPGA的简易DDS信号发生器的设计原理和步骤,并提供Verilog代码示例。

一、DDS信号发生器设计原理

1、概述

DDS(Direct Digital Synthesizer,直接数字合成器)是一种数字合成技术,它利用数字方式生成模拟信号。

基本原理是通过查表法或计算法从存储有波形数据的ROM中查询并输出相应的波形点,再通过D/A转换器转换成模拟信号。

查表法因其结构简单而被广泛应用,它需要预先在ROM中存放不同相位对应的幅度序列,然后通过相位累加器的输出进行寻址。

2、基本结构

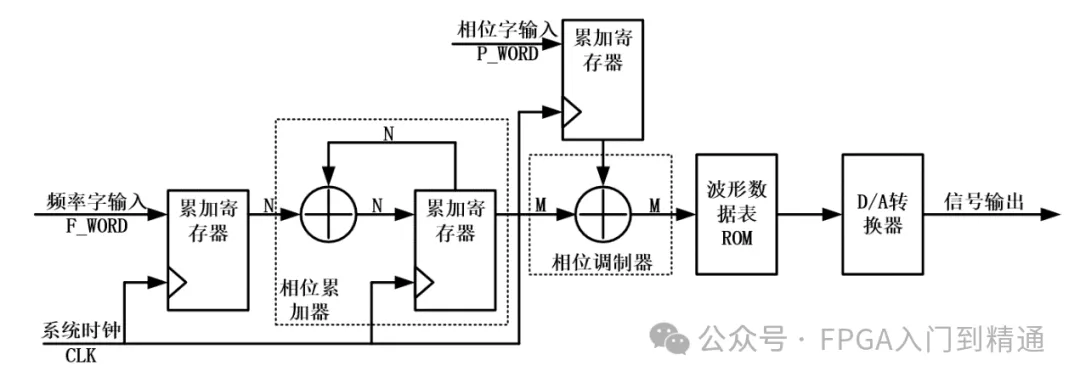

DDS基本结构主要由相位累加器、相位调制器、波形数据表ROM、D/A转换器等四大结构组成。DDS结构示意图,如下图所示。

(1)相位累加器(Phase Accumulator)

作为DDS的核心,相位累加器负责生成相位码,其输入为频率字输入,位宽通常用N表示。相位累加器的输出是连续累加的结果,用于控制信号的频率。

(2)相位调制器(Phase Modulator)

接收相位累加器的输出,并加上相位偏移值P,用于实现信号的相位调制。

(3)波形数据表ROM(Waveform ROM)

存储一个或多个周期的波形数据,如正弦波。ROM的地址由相位调制器的输出决定,从而读取相应的波形数据。

(4)数模转换器(D/A Converter)

将波形数据表ROM输出的数字信号转换为模拟信号,即最终的输出信号CLK_OUT。

3、DDS工作原理

DDS的工作原理可以概括为以下几个步骤:

(1)系统时钟CLK驱动整个DDS系统,频率为fCLK。

(2)频率字输入Fword(用K表示)控制输出信号的频率,其数值越大,输出频率越高。

频率字输入K,表示相位增量,设其位宽为N,满足等式K = 2N * fOUT / fCLK。

(3)相位字输入Pword(用P表示)控制输出信号的相位偏移,用于相位调制。

(4)相位累加器根据频率字输入K和系统时钟频率Fclk累加相位值,生成相位码。

相位累加器是DDS信号发生器的核心部分,它的作用是逐周期地累积相位。

相位累加器通常是一个N位的寄存器,其值在每个系统时钟周期CLK下累加频率控制字Fword。

相位累加的过程可以用以下公式表示:

Phase_Acc = Phase_Acc + Fword

其中,Phase_Acc是当前时钟周期的相位累加值,Fword是频率控制字,它决定了累加的步长。

相位累加寄存器通常用于存储相位累加器的当前值,以便进行相位调制或作为查找ROM的地址,记为Phase_Reg。

考虑到ROM表地址深度M的影响,相位累加寄存器取Phase_Acc高M比特,也就是

Phase_Reg = Phase_Acc >> (N - M)

(5)相位调制器根据相位字输入P调整相位累加器的输出,实现相位调制。

相位调制器接收相位寄存器的输出,并可能加上一个相位控制字Pword,用于实现信号的相位偏移或调制。

相位调制可以用以下公式表示:

Phase_Mod = Phase_Reg + Pword

Phase_Reg是相位寄存器的输出,Pword是相位控制字。

(6)波形数据表ROM根据相位调制器的输出地址Phase_Mod,读取对应的波形数据,将ROM表的地址位宽记为M。

假设波形数据ROM的地址位宽为12位,存储数据位宽为8位,即ROM有212 = 4096个存储空间,每个存储空间可存储1字节数据。

(7)D/A转换器将ROM输出的数字波形数据转换为模拟信号CLK_OUT,频率为fOUT,计算公式如下: fOUT = K * fCLK / 2N。

当K = 1时,可得DDS最小分辨率为:fOUT = fCLK / 2N,此时输出信号频率最低。

根据采样定理,K的最大值应小于2N / 2。

二、Verilog代码示例

module DDS_Module(

input clk,

input reset,

input [2:0] f_ctrl, // 频率控制字

input [9:0] p_ctrl, // 相位控制字

output [9:0] dout // 输出数据

);

// 相位累加器

reg [12:0] phase_acc;

always @(posedge clk or negedge reset) begin

if (!reset) phase_acc <= 13'd0;

else phase_acc <= phase_acc + f_ctrl; // 累加频率控制字

end

// 实时相位,结合相位控制字

reg [9:0] phase_now;

always @(posedge clk or negedge reset) begin

if (!reset) phase_now <= 10'd0;

else phase_now <= phase_acc[12:3] + p_ctrl; // 取相位累加器的高位

end

// 波形数据查询 地址深度为 10bit

DDS_ROM uut (

.clka(clk),

.addra(phase_now),

.douta(dout)

);

endmodule

三、总结

DDS并不复杂,只需要搞清楚原理,很容易快速掌握。

1、通过调节频率控制字K,可以控制相位累加器的累加速度,进而ROM读取地址的速度,这样就可以控制输出波形频率了;

2、通过调节相位控制字P,可以控制相位调制器,进而控制ROM读取地址的初值,这样就可以控制输出波形的初值;

3、通过调整ROM表中的数据,可以通过matlab、python等生成不同的波形数据,进而输出不同的波形。