文章来源:数字站

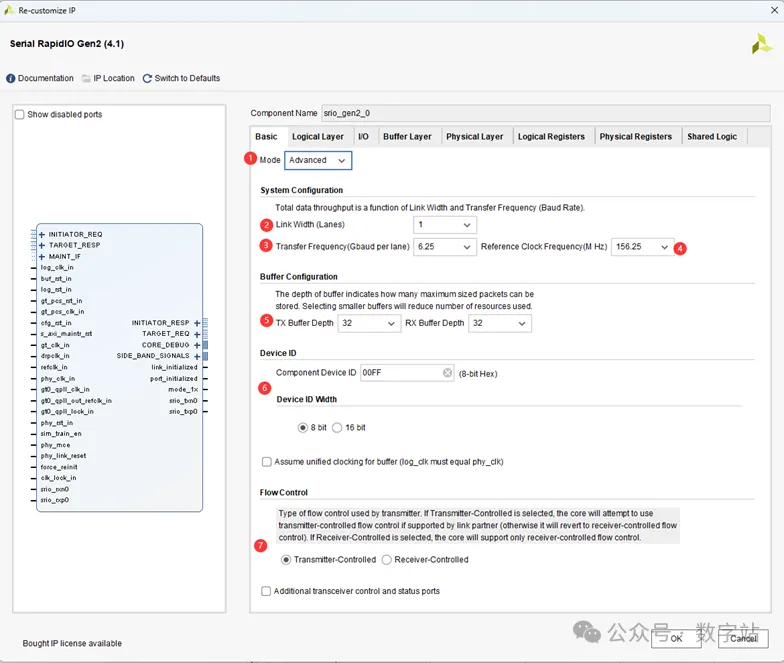

配置SRIO IP

5处需要设置发送端和接收端buffer的深度,可以设置为8、16、32,表示缓冲区能够存储的最多数据包数量。

然后配置“Logiccal Layer”界面,如下图所示,其中1和2用于配置发送端和接收端支持的数据包类型,一般默认即可,均支持写、流写、带响应的写、读、门铃、消息等事务。

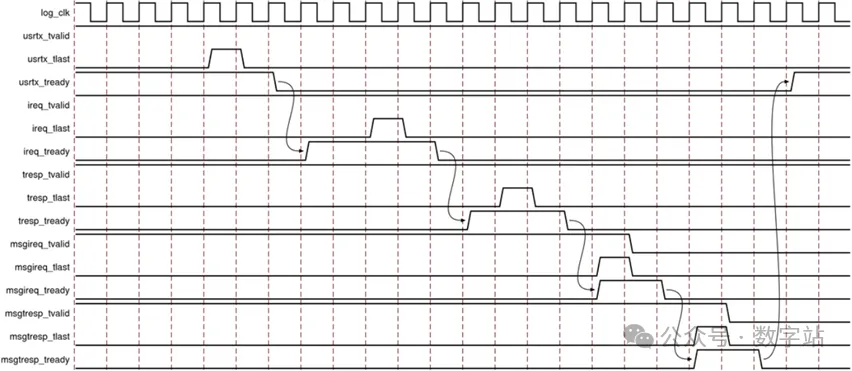

在稳定状态下,如果所有端口的tvalid信号都被拉高,如下图所示。仲裁器将按以下顺序拉高tready来响应对应的端口,实现仲裁功能。

图3 仲裁时序图

当端口设置为Initiator/Target I/O时,依次响应用户定义端口、发送方请求端口、目标响应端口、消息发送方请求端口、消息目标响应端口、维护端口。

当端口设置为Condensed I/O时,依次响应用户定义端口、精简I/O发送端口、消息发起方请求端口、消息目标响应端口、维护端口。每当一个端口赢得仲裁时,它就会移动到队列的末尾,所有其他端口都会上移一个位置。

4处始终勾选,表示核心能够发起维护请求(包括本地和远程请求)。

5处为本地配置空间基址,勾选时内核检查传入I/O事务的高位地址,如果地址匹配,则将事务路由到维护端口。LCSBA匹配仅由核心对HELLO格式的数据包执行,I/O格式必须设置为HELLO,并且必须支持事务类型,以便核心将数据包重新路由到维护端口。

默认LCSBA掩码:LCSBA CSR的复位值。一个10位掩码,与传入I/O事务的高位地址进行比较,以便它们在以此地址空间为目标时可以重新路由到配置空间。

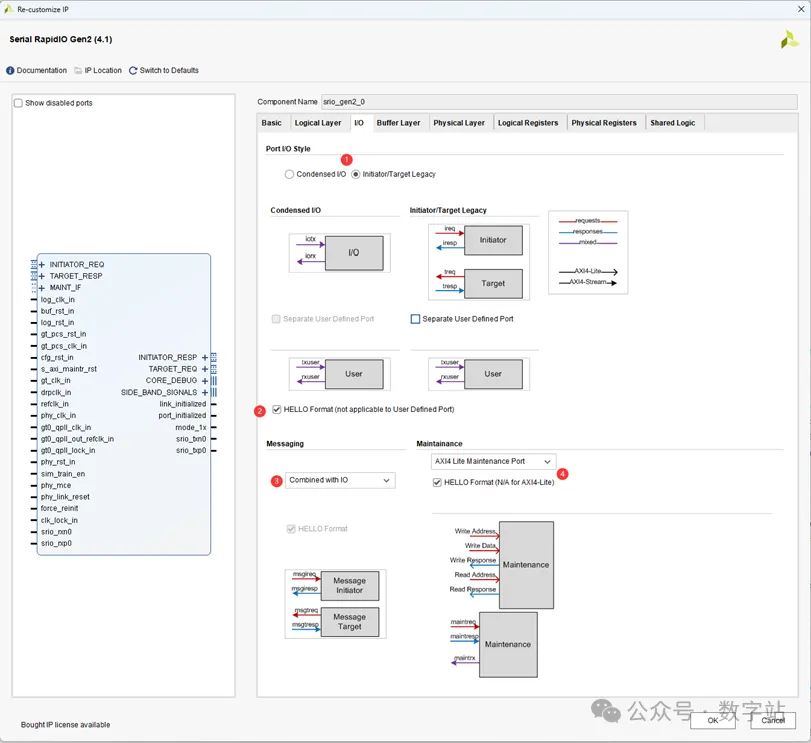

下图配置“I/O”界面,该界面用于配置逻辑层用户端口的端口形式和数据格式。

1处用于设置I/O端口使用Condensed I/O模式还是Initiator/Target I/O模式,通常使用Initiator/Target I/O。

勾选选项2将I/O端口的数据格式设置为HELLO,否则使用SRIO Stream交互数据。

3处用于选择消息传递端口的接口样式,可以与I/O端口结合,也可以将消息端口单独分离出来。默认消息端口与I/O端口结合使用。

4处用于设置维护方式,SRIO Gen2提供了AXI4-Lite维护端口选项。

下图时设置“Buffer Layer”界面,勾选1允许发送缓冲区重新排序请求包,优先级较高的请求包会在优先级较低的请求包之前发出。

图5 设置“Buffer Layer”界面

2处是流量控制选项,暂时保持默认即可。

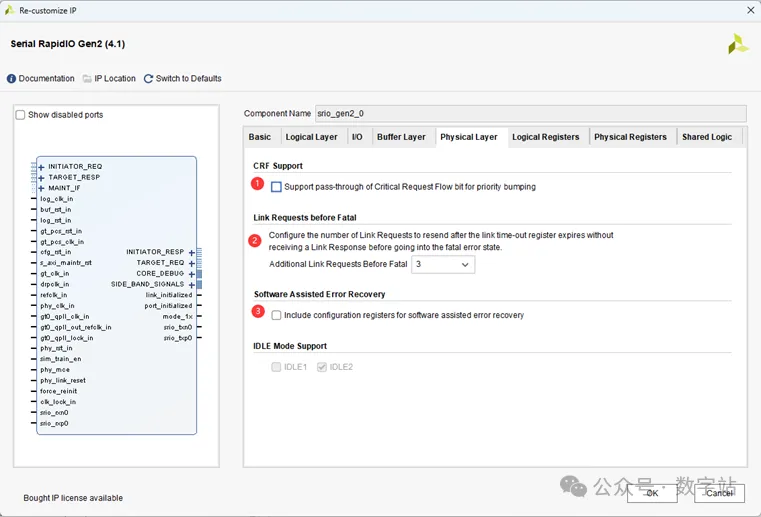

下图用于设置PHY层,1处用于指示CRF位是否用于扩展优先级映射。

2处通过下拉列表选择在转换到致命错误状态之前,在没有收到链接响应的情况下要发送的链接请求的数量,默认设置为3。

勾选3启用软件辅助错误恢复:RapidIO规范专门为软件辅助错误恢复定义了三个命令和状态寄存器。

空闲模式支持:支持的空闲模式因组件/系统生成页面上选择的传输频率而异。IDLE1仅支持线速率小于5Gbps的模式,IDLE2只支持线速率为6.25Gbps的链路设计。

设置“Logic Registers”界面如下图所示,1处是设备标识卡存储RapidIO设备的信息,不可修改。

图7 设置“Logic Registers”界面

2处Assembly Identity CAR:存储有关RapidIO设备子系统创建者的信息,可以设置寄存器的程序集标识符和程序集供应商标识符字段,以唯一地标识端点,这些值不会影响核心功能。

3 处Assembly Information CAR:存储有关RapidIO设备子系统版本的信息,不影响核心功能。

4 处 Processing Element Features CAR:选择处理元件提供的主要功能,可选设置有桥、内存、处理器、内存和桥,一般将FPGA设置为内存。

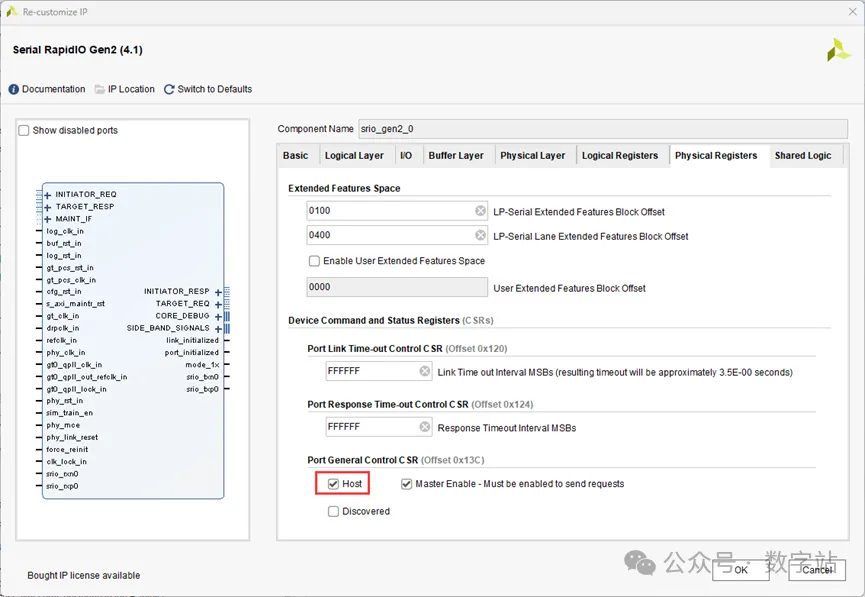

下图是设置“Physical Registers”界面,该界面只需要关注该设备是否作为主机,其余选项保持默认即可。

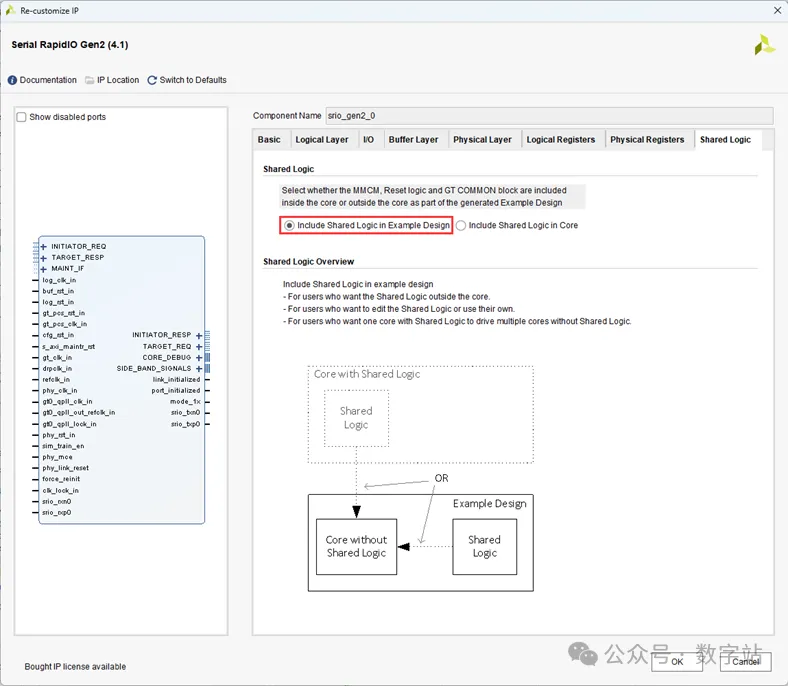

最后配置“Shared Logic”界面,如下所示,将共享逻辑放在示例工程中,便于后续扩展。

分析SRIO示例工程

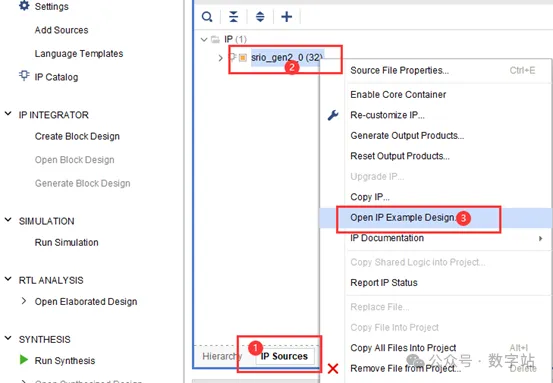

如下图所示,在IP选项卡中,鼠标右键生成的IP,然后选择Open IP Example Design…,即可打开该IP的官方示例工程(如果该选项卡是灰色的,则表示该IP还没有完全生成,Vivado右上角还有圈在旋转,在等一会即可)。

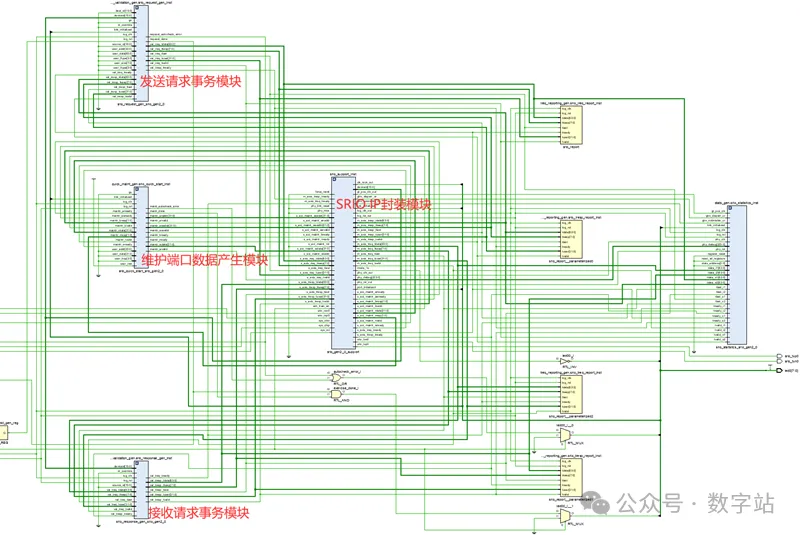

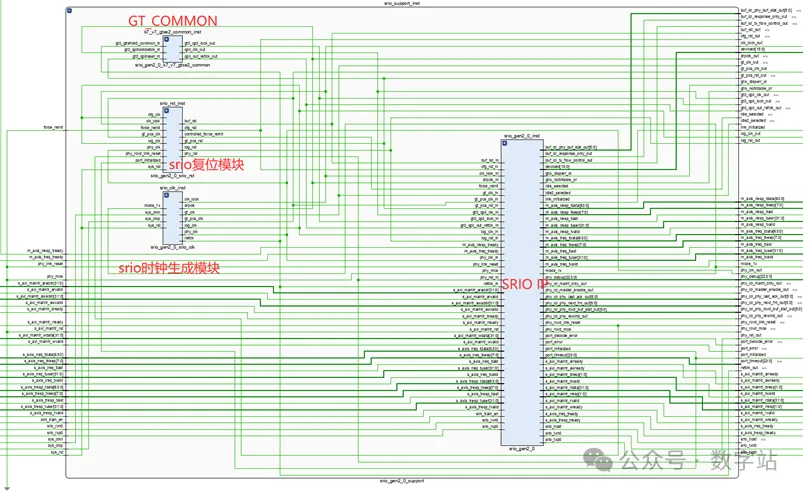

打开顶层RTL视图如下所示,中间是SRIO IP封装完的模块,左边有发送请求事务模块(ireq和iresp)、接收请求事务模块(treq和tresp)、维护事务模块。

SRIO的示例工程的顶层文件结构如下所示,包含9个文件,经常使用到的2个文件如下,1是发送数据模块,2是接收数据模块。

图13 顶层模块包含的文件

发送数据模块

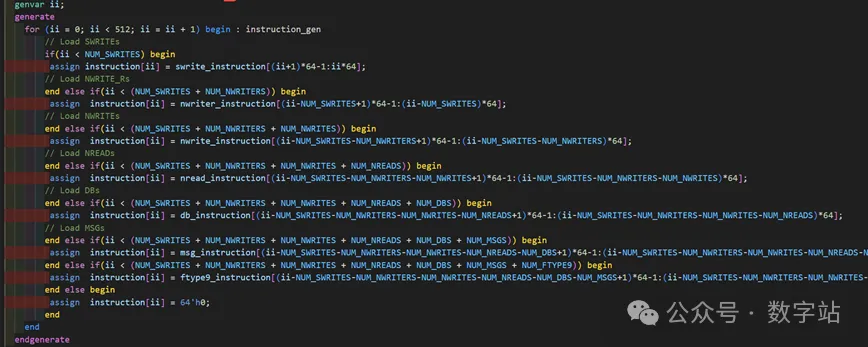

首先通过一个for循环,将存储体instruction先初始化,内部存储instruction_list.vh文件中的数据。

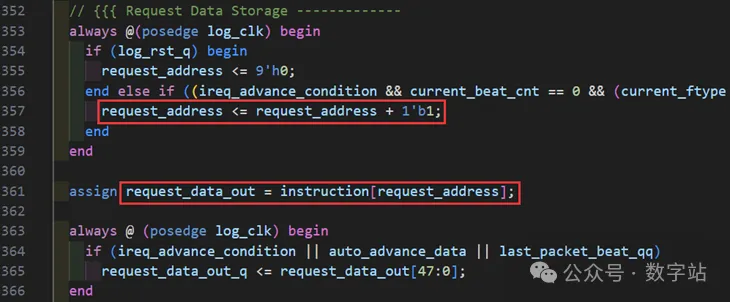

然后通过request_address来获取对应的包头数据。

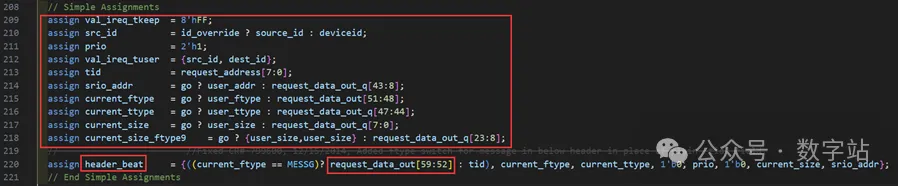

最终的包头数据如下所示。

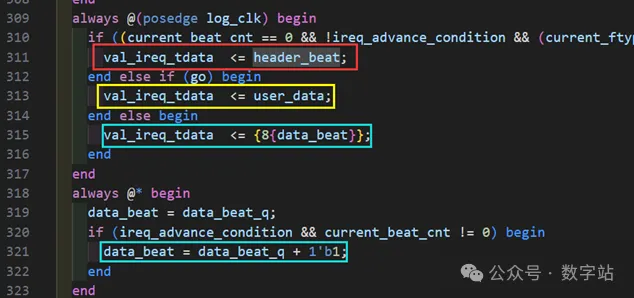

最终发送的数据如下所示,首先发送包头数据,如果有用户自己的数据(go为高电平),则发送用户数据,否则发送递增的8字节数据。

图17 发送数据

接收数据模块

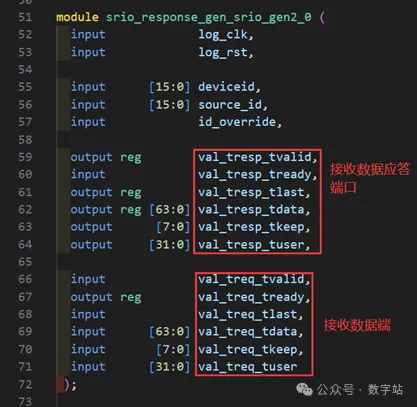

下图是接收数据模块的端口信号列表,包含接收数据请求和接收数据应答。

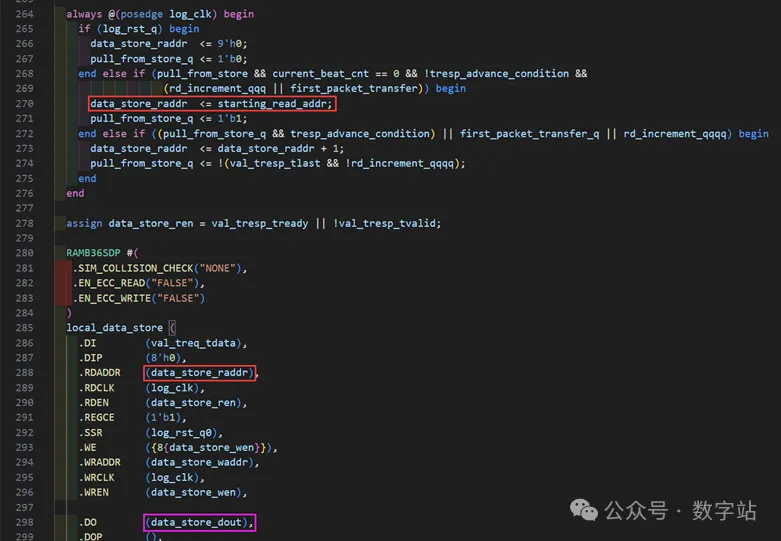

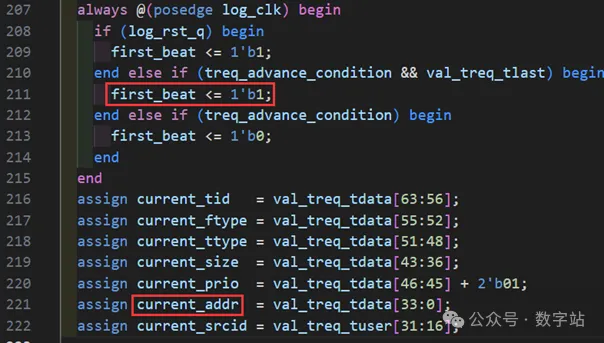

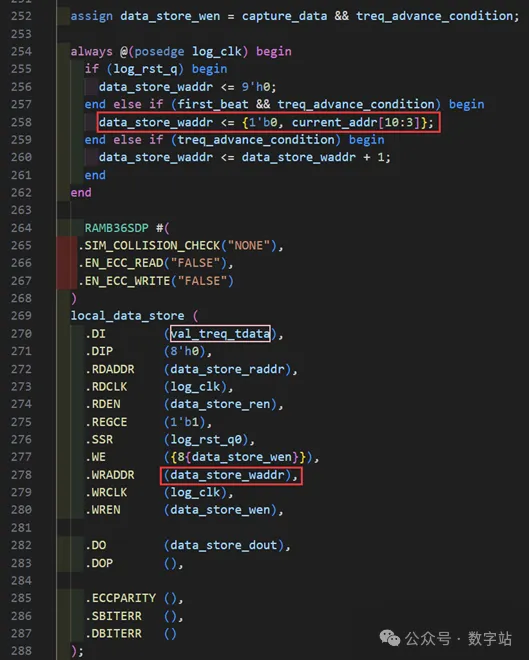

首先会从接收到的第一个数据中解析出数据包的一些控制信号,如下图所示,包含数据存储的起始地址、数据长度、ftype等信息。

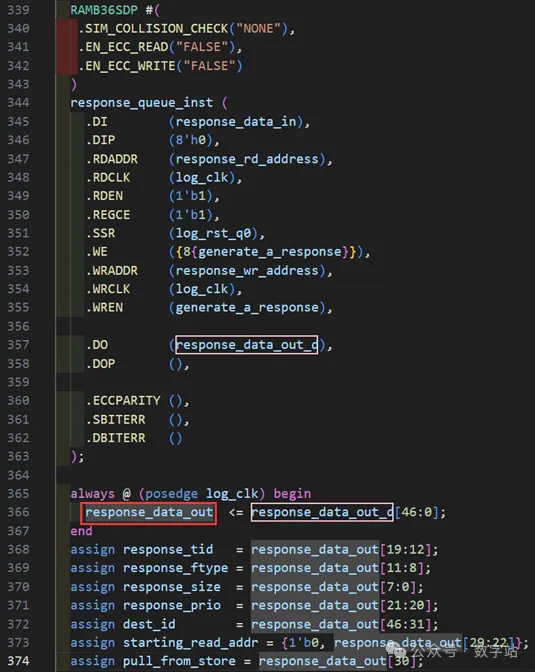

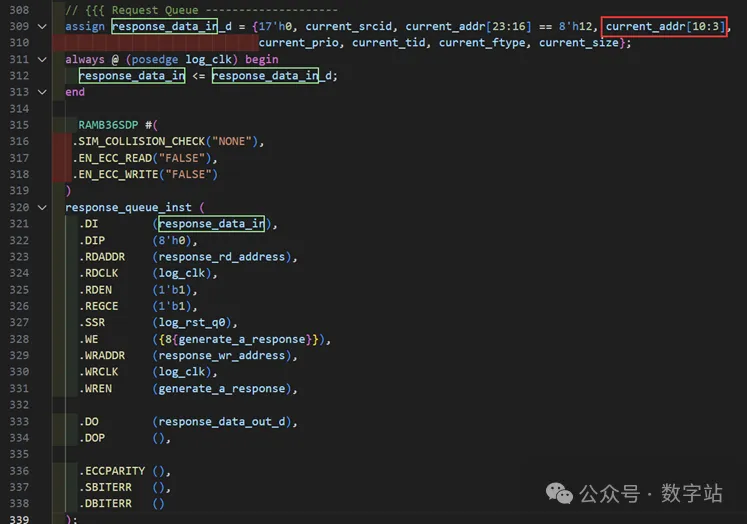

同时把解析出的数据包帧头部分存入另一个RAM中,便于后续应答时,通过地址读出对应数据包的控制信息,如下图所示。

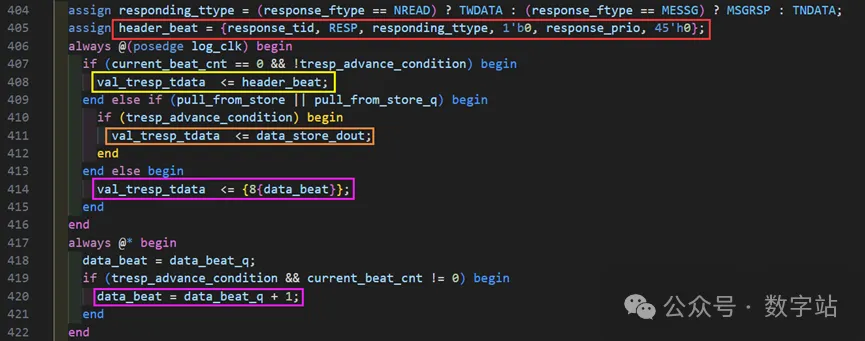

上述是接收数据并且存储数据的部分,下面就是从RAM中读出数据,并且响应请求的逻辑代码。首先从存储数据帧头的RAM中读出数据,然后将数据解析出存储数据的RAM地址、数据段大小、ftype等。