作者:数字站

如果要在Xilinx的FPGA上使用万兆以太网通信,大致有三种方法构建协议栈。第一种使用GTX等Serdes作为底层的PHY,上层通过HDL实现构建MAC和IP层,这种方式难度会比较大,底层需要完成PHY层的设计,最终我想通过这种方式实现万兆以太网的搭建。第二种是通过Xilinx提供的10G PCS PMA作为底层的PHY,用户通过HDL实现MAC层和IP层的设计。难度相比第一种会低一点,能够清晰的学习到MAC层、IP层、ARP协议、ICMP协议、UDP协议内容。第三种是使用Xilinx提供带有MAC层的IP,这种方式用户只需要阅读手册,给IP提供收发的数据即可,没有什么难度,对于学习没啥作用。目前先通过10G PCS PMA作为PHY层,熟悉MAC层以及之上的设计,整个协议跑通之后,在把底层的PHY用GTX取代,从而实现第一种设计。

概括10GBASE-R/KR

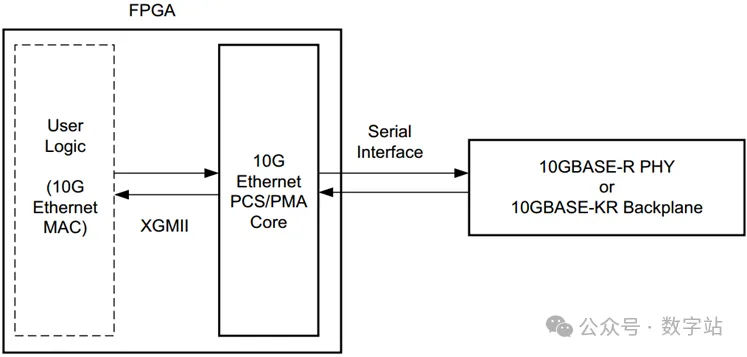

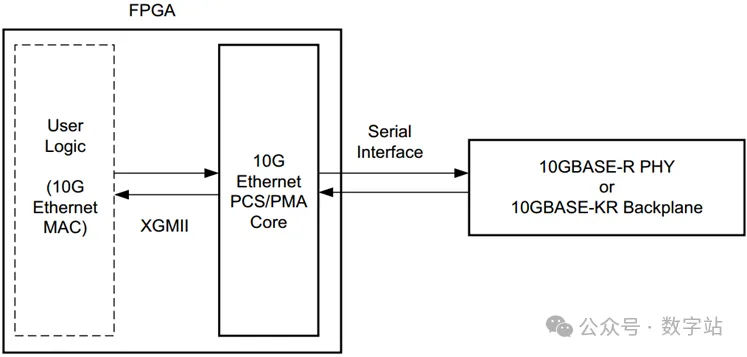

下图是10G PCS PMA的使用原理,上层通过XGMII接口与用户逻辑的MAC层交互数据(MAC层可以用户自己设计,也可以使用官方的MAC层IP),接收的用户数据经过内部PCS PMA处理后,通过Serdes接口输出到光纤,与接收端的设备进行通信。

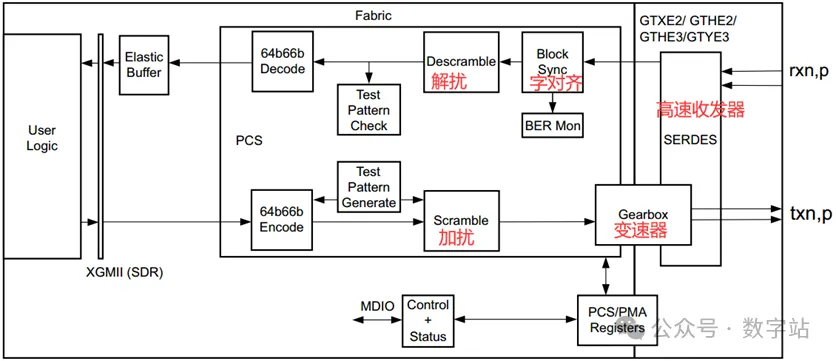

10G PCS PMA可以通过参数设置该PHY层工作在10GBASE-R还是10GBASE-KR的模式下。下图是10GBASE-R的内部框图,10G以太网使用64B66B进行编码,10GBASE-R内核其实就是在Serdes的基础上封装得到的。如果看过前文GTX自定义64B66B的PHY层协议设计的同学,关于下面的设计应该会比较熟悉。同样都包含加扰、解扰、接收端字对齐、变速器等等,这里的64B66B编码和解码模块应该是将XGMII接口协议转换为Serdes 64B66B的接口协议。

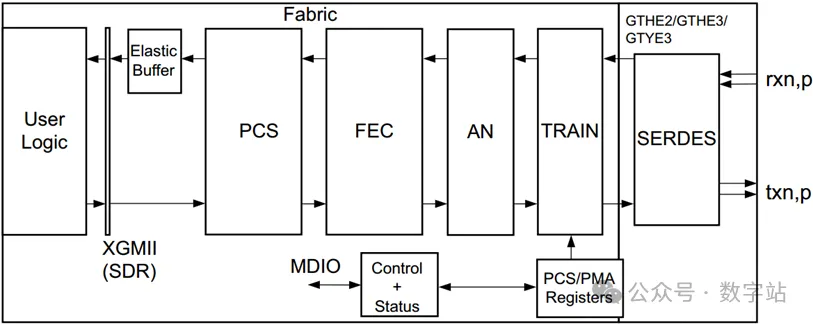

在接收端有一个弹性缓冲器(Elastic Buffer),深度为32个字(1个字包含64位数据和8位控制字符),起到时钟纠正的作用。允许在缓冲区溢出(和字被丢弃)之前最多存储64个时钟校正(CC)序列,缓冲器通常填充到一半,然后当超过一半时删除CC序列,当低于一半时插入CC序列。因此,在半满状态下,可以(保守地)接受额外的360 KB数据(以+200 ppm的速率接收),而不会丢失任何数据。10GBASE-KR内核框图如下所示,相比10GBASE-R内核增加了链路训练模块以及可选的自动协商(AN)和前向纠错(FEC)功能,以支持背板上的10 Gb/s数据流。

图3 10GBASE-KR内核框图

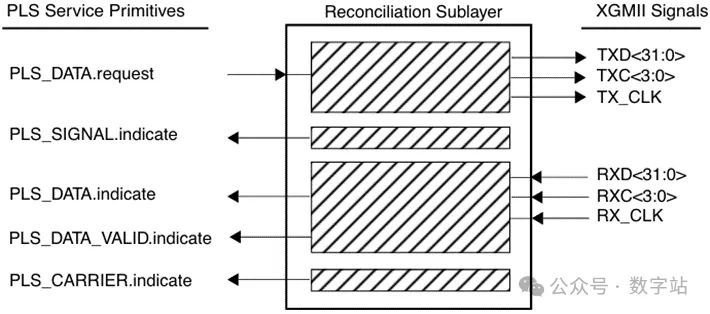

XGMII接口时序

在前文讲解过XGMII接口并不适用于芯片之间的高速通信,但是在FPGA内部是一个比较好用的接口,因为FPGA内部数据位宽大一点是没有太大关系的。前文讲解的芯片间的XGMII接口如下所示,接收端和发送端采用32位双沿传输的数据线通信。

但是FPGA内部逻辑只支持单沿传输,因此10G PCS PMA给用户提供的XGMII接口是单沿传输数据的。为了保证带宽不变,收发数据位宽有64位和32位两种可选,其中10GBASE-KR只支持64位数据位宽。

64位数据位宽

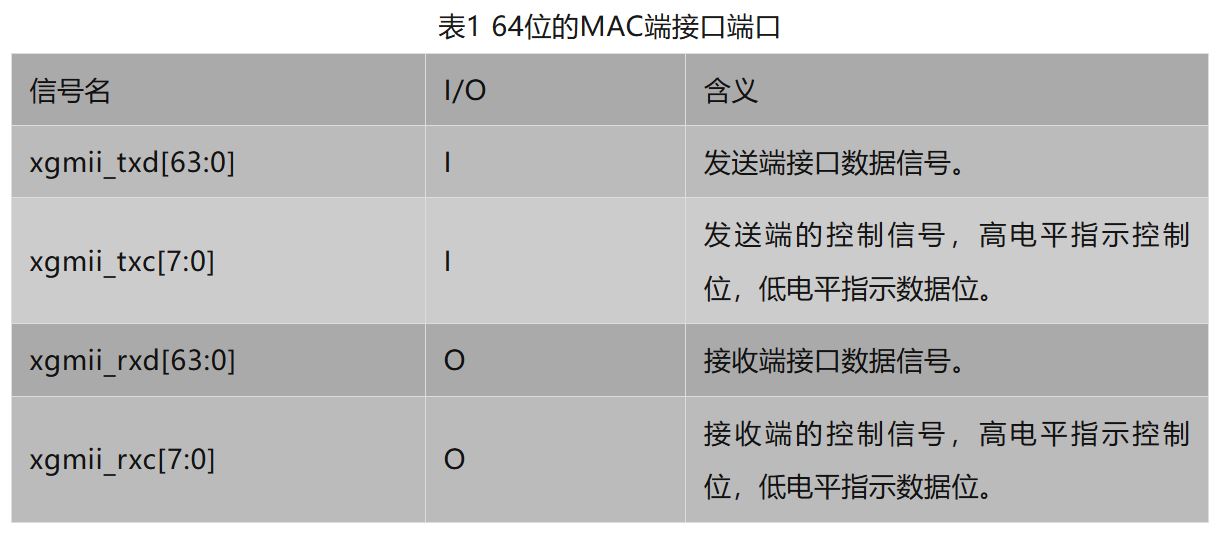

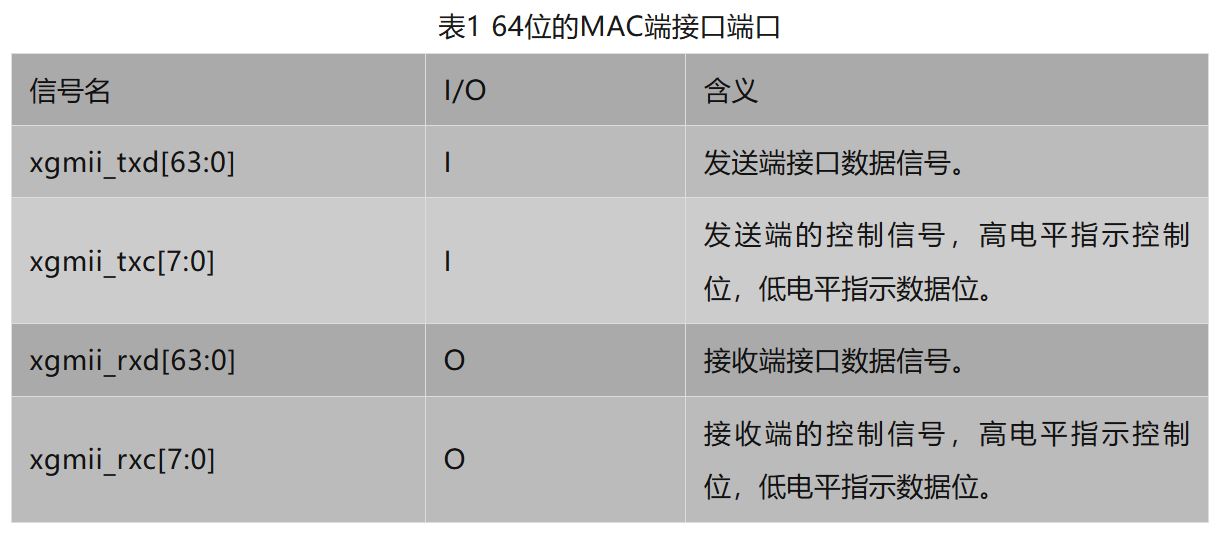

下表是64位数据位宽的XGMII端口信号,8位控制位。控制位的高电平表示数据信号对应字节为控制位,低电平表示数据信号对应字节为数据位。

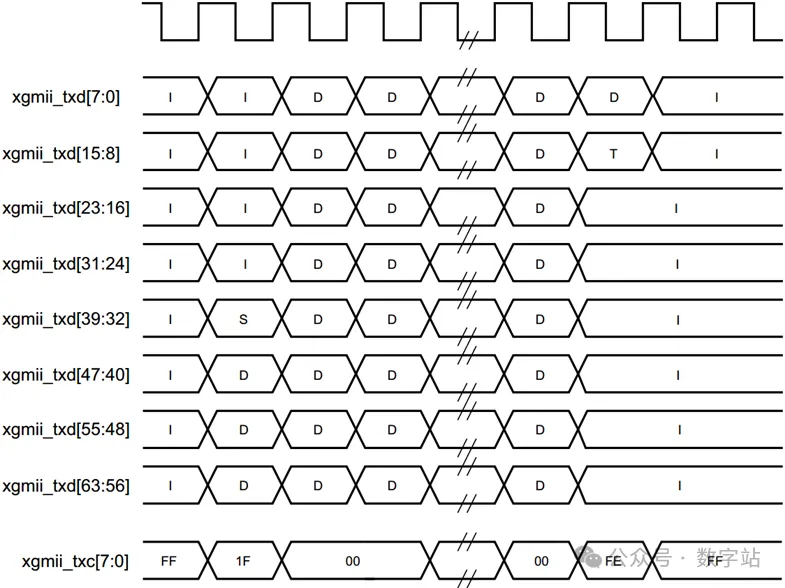

下图是通过64位接口发送数据帧的时序,数据帧的开始由起始字符(下图中通道4的/S/)表示,后面5、6和7字节发送数据字符。

万兆以太网规定起始位/S/可以位于第一字节,也可以位于第四字节。图中的I是空闲字符,注意在xgmii_txd对应字节为控制字符时,xgmii_txc对应的控制位为高电平。在xgmii_txd对应字节为数据字符时,xgmii_txc对应的控制位为低电平。由下图可知,XGMII接口先传输低字节数据,后传输高字节数据。因此起始字符所在数据的低5字节为控制字符,发送起始字节/S/后,开始传输数据,高三字节为数据,对应的xgmii_txc的值为8’h1f。

因为以太网可以传输任意字节包长的数据,停止位可以出现在任意字节的位置,上图中的/T/字符表示停止位。在数据传输过程中,还可以发送/E/表示该字段是错误数据,如下图所示,这种情况一般不会使用。

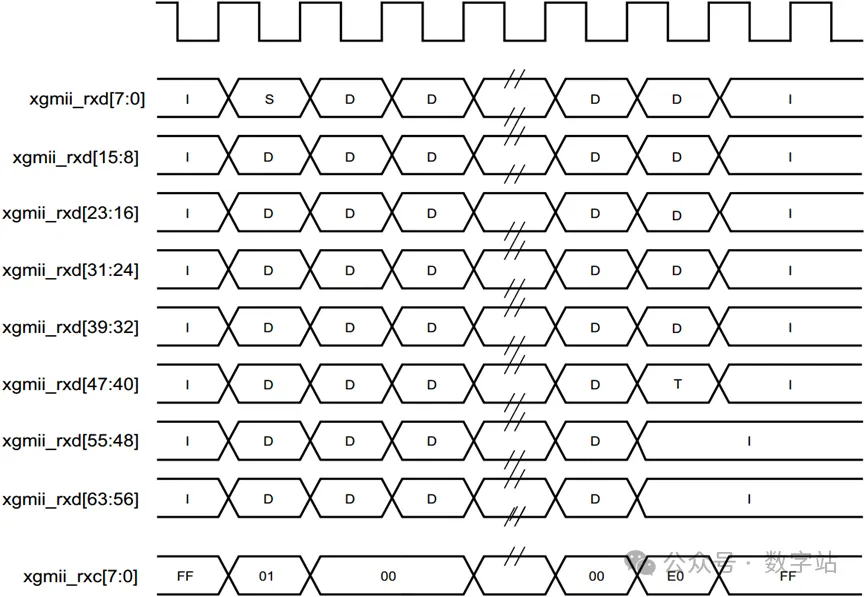

接收数据端口时序如下图所示,下图中是起始位处于第0字节的情况。

下表将上述字符对应的取值列出,其中起始位S的值为8’hfb,停止位T的值为8’hfd,空闲字符I的取值为8’h07,且都是控制字符。

手册中给出了发送通道的延时(数据从输入xgmii_txd[63:0]传输到gt_txd[31:0]消耗的时间,不包括高速收发器内部的延时)。7系列FPGA的延迟为20个txoutclk周期,使能FEC功能后延时增加到26个txoutclk周期。

接收方向的延迟(数据从gt_rxd[31:0]传输到xgmii_rxd[63:0]上的时间)主要取决于弹性缓冲器的填充水平。延迟标称值为27.75个coreclk周期,当弹性缓冲达到最大时,延时为41.26个coreclk周期,延时这部分了解即可。

32位数据位宽

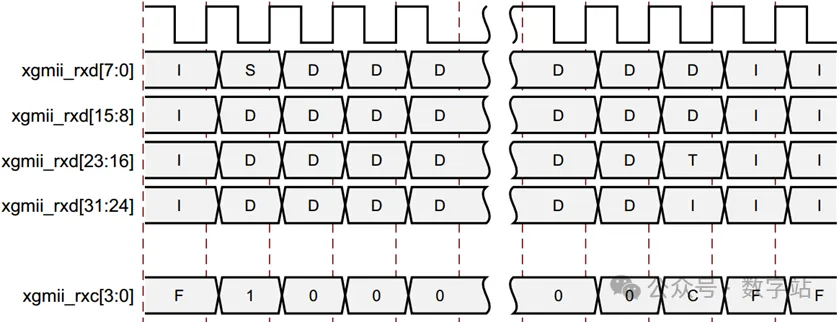

下表是32位数据位宽的XGMII接口信号,4位控制位,高电平表示数据信号对应字节为控制位,低电平表示数据信号对应字节为数据位。

下图是32位XGMII接口传输数据帧的时序,开始字符/S/只能出现在第1字节,后面的3字节为传输数据。数据传输完成后,发送停止位/T/,其余时间使用空闲字符填充。

接收端口的时序如下所示,与发送端口的时序基本一致,不过多赘述。

7系列器件发送通道上XGMII接口的延迟(数据从输入xgmii_txd[31:0]传输到gt_txd[31:0]消耗的时间)为14个txoutclk周期。而接收通道的延时范围在44.6~72个coreclk周期,具体取值取决于接收端弹性缓冲器当前的填充数据个数。64位的数据端口的时钟频率为156.25MHz,而32位数据位宽的时钟频率为312.5MHz。FPGA内部常用大位宽数据接口,降低时钟频率,获得更好的时序,因此接口数据位宽选择64位会比较好。

内核时钟分析

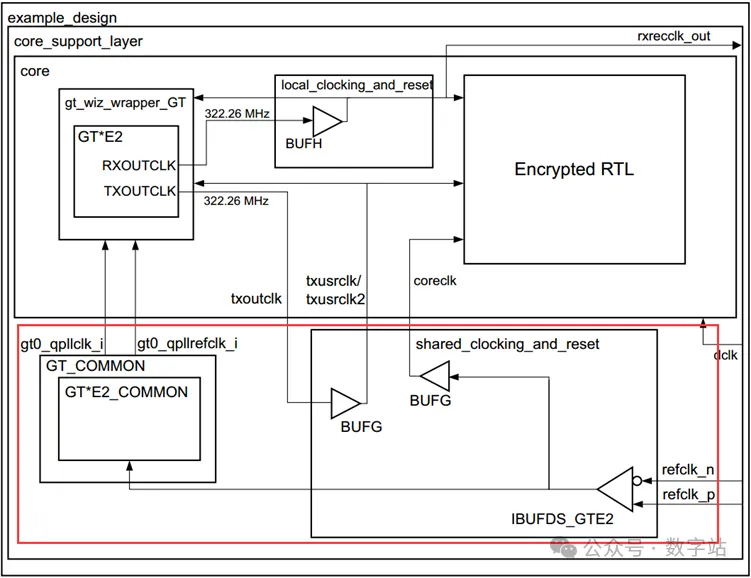

只要使用高速IP,就绕不开时钟,并且绕不开GTX的时钟,这也是前面在讲解GTX的时候,深度分析其时钟的原因。只要熟悉GTX内部各个时钟的关系,其余上层IP的时钟架构都很简单。如果XGMII的数据接口选择64位,则7系列的FPGA必须给高速收发器提供156.25MHz的差分参考时钟(refclk_p/refclk_n端口)。如果是32位数据接口,则必须提供312.5 MHz的差分参考时钟。下图是该IP的内核时钟结构,其中红框部分可以放置在示例工程中。内核时钟作为用户接口的时钟信号,就是输入的差分参考时钟信号。

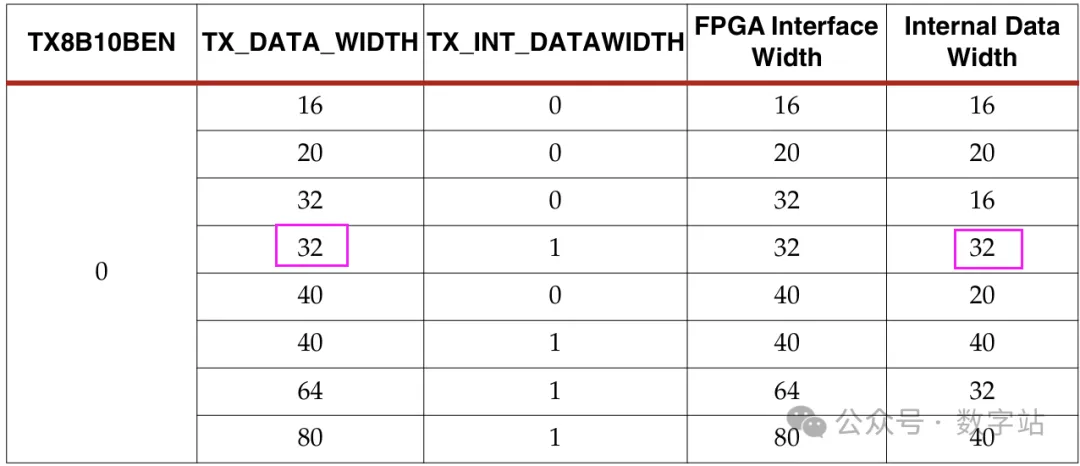

为什么上图中TXOUTCLK为322.26MHz?通过这个时钟生成uxrclk和usrclk2?首先万兆以太网的是指在进行64B66B编码前的数据传输速率为10Gbps,经过64B66B编码之后,速率变为10Gbps / (64 / 66) = 10.3125Gbps,即万兆以太网的线速率为10.3125Gbps。在前面讲解GTX的64B66B编码时,如下图所示,高速收发器的PCS内部并行数据传输的位宽为32位,即可算出usrclk的频率应该为10.3125Gbps / 32 = 322.265625 M Hz ≈ 322.26 MHz。

图11 GTX内部传输数据位宽

此处的TXOUTCLK通过BUFG之后直接作为txusrclk和txusrclk2,没有经过MMCM分频处理,还可以推测出高速收发器接收和发送的数据位宽同为32位。为什么有上述推导,原因在讲GTX的时候都详解过,10G PCS PMA也不过是在GTX上封装而来,底层的时钟关系是不会变的,吃透GTX时钟关系即可以吃透所有上层高速IP的时钟关系。现在已经讲解过Aurora、SRIO、10G PCS PMA的时钟架构都遵循GTX的时钟架构规则,后续的JESD204B依旧如此。

其余接口

10G PCS PMA作为一个PHY层设计,内部也有很多的寄存器,用户可以通过MDIO设置内部寄存器的数值。但是一般保持默认即可,因此该接口的时序不做讲解,在讲解千兆网接口时,详解过MDIO接口时序,可以参考。另外该IP可以通过DRP接口动态配置参数,如果不需要使用DRP接口,则将drp接口的所有信号与core_to_gt_drp接口对应信号相连,并将drp_req连接到drp_gnt,允许内核在需要时访问DRP,如下图所示。

图12 DRP接口连接(无需访问)

IP的功能信号与调试信号

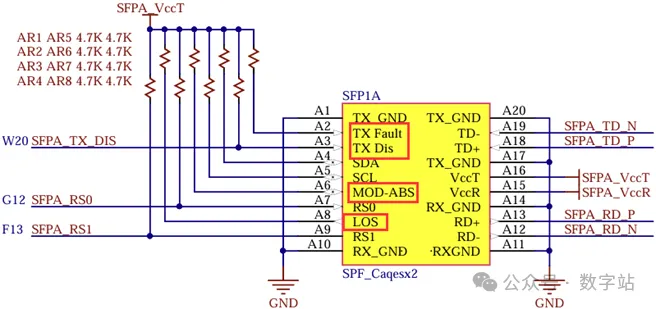

下图是一个光纤接口的原理图,其中tx_fault、MODDEF0、LOS(信号丢失)都上拉到VCC,且没有连接到FPGA的管脚。而10G PCS PMA建议将signal_detect(MODDEF0或非LOS)信号连接到VCC,tx_fault信号连接到GND。因此在调用IP时,直接把signal_detect赋值为1,tx_fault赋值为0,不与引脚相连。同时10G PCS PMA提供了一个tx_disable信号,可以直接连接到光口。

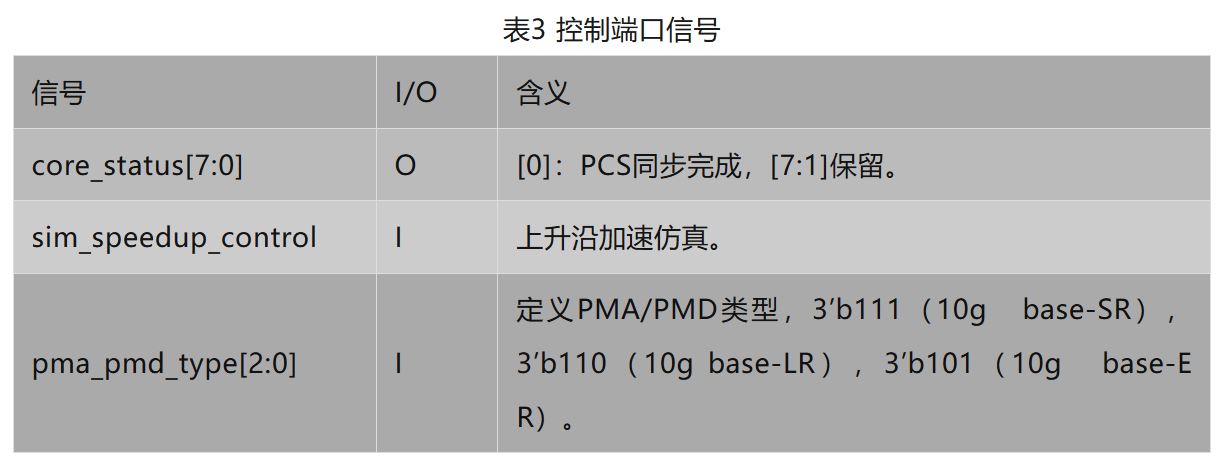

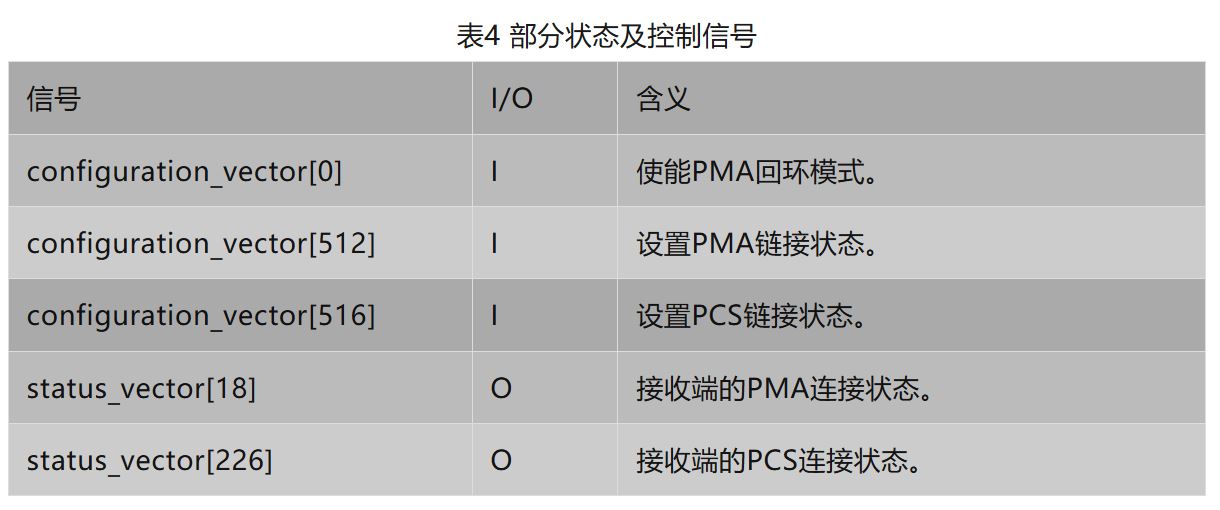

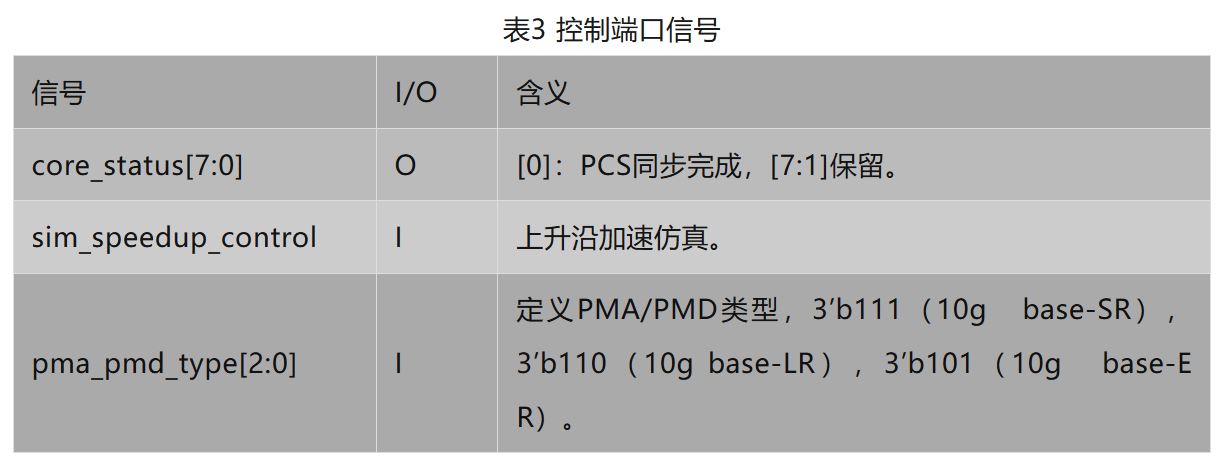

该IP的发送端和接收端都有复位完成指示信号,reset_counter_done表示配置完成后已经过了500 ns。另外还有一些10GBASE-R的控制信号和状态信号,如下表所示。特别注意仿真加速信号,在仿真开始时,必须给该信号提供一个上升沿(先拉低至少100ns后拉高),才能加速仿真,否则可能仿真半个小时也跑不出结果。

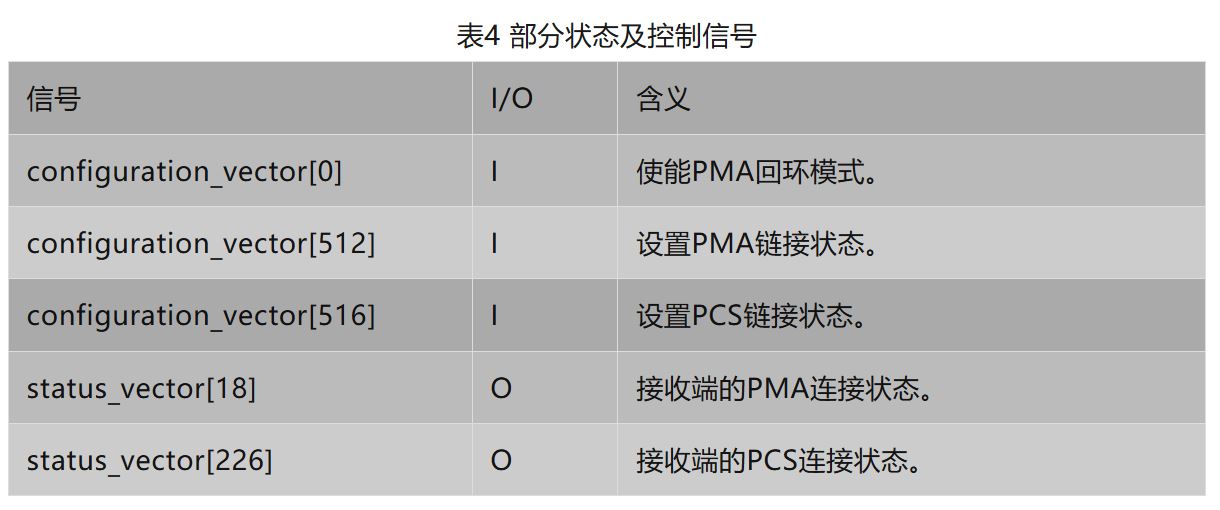

该IP还有一些控制信号configuration_vector[535:0]和状态信号status_vector[447:0]。这两个寄存器的每一位都有其特定含义,但用户只需要关注一些常用的数据位即可,其余的寄存器在使用时可以通过手册查看。

关于10G PCS PMA的讲解到此结束了,通过以上介绍,足够简单使用该IP,后文将通过该IP构建万兆以太网的PHY层。本文参考于Xilinx的Pg068手册,可以在官方获取,也可以在公众号后台回复“xilinx手册”(不含引号)获取,该文件包含我前面用到的所有xilinx相关手册。

文章来源:数字站