IBERT for GTY中两点总结

judy 在 周五, 12/03/2021 - 10:37 提交

在IBERT测试中需要注意的有以下两个要点

在IBERT测试中需要注意的有以下两个要点

Petalinux2020.01 内核DMA驱动调试过程分享

对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

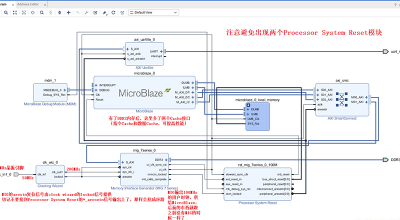

添加了DDR3内存以后,程序既可以运行在BRAM里面,也可以运行在DDR3内存里面。但如果运行在DDR3内存里面,固化起来会比较麻烦,需要借助SREC SPI Bootloader。

对FPGA进行上板调试时,使用最多的是SignalTap,但SignalTap主要用来抓取信号时序,当需要发送信号到FPGA时,Jtag Master可以发挥很好的作用,可以通过Jtag Master对FPGA进行读写测试

FPGA中乘法器是很稀缺的资源,但也是我们做算法必不可少的资源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我们可以通过调IP Core的方式或者原语的方式来进行乘法操作。在里面可以设置有符号还是无符号数乘法。

本文以浮点数Floating-point IP核将定点数转换为浮点数为例,详细讲解AXI DMA IP核的使用方法。

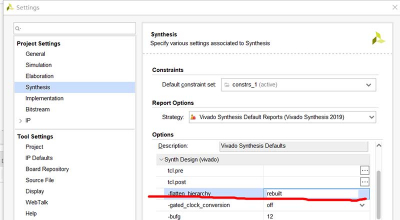

当选择为none,综合器优化的最少,当选择为full时,综合器优化的最多,选择rebuilt时,工具自动选择一个折中的方案,对当前工程做优化。如果在rebuilt的选项不希望一些信号被优化,则可以调用原语进行约束。

Xilinx Vitis 2020.1里面运行C程序时提示找不到microblaze_0

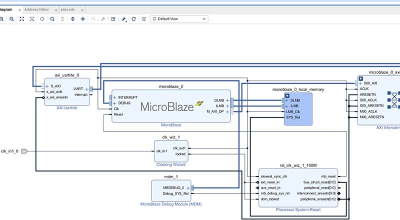

在Zynq开发时,在Vivado中新建Zynq硬件平台,加入DMA、AXI接口模块,在进行构建软件系统之前,通常需要对硬件平台进行验证,检测模块新建过程中是否存在问题。下面对这一过程进行简单介绍。