本文是该系列的第2篇,上一篇介绍了System Generator的基本知识以及软件的安装。本文将以一个简单的数字滤波器的设计为主题,介绍Sysgem Generator的完整设计流程,同时详细介绍使用到的各个block。

本设计使用到的block

1.Xilinx block:

Digital FIR Filter(->DSP):数字滤波器

Gateway In(->Basic Elements):数据输入

Gateway Out(->Basic Elements):数据输出

System Generator(->Basic Elements):系统管理

FDATool(->DSP):滤波器设计

2.其它block:

Sin Wave(Simulink->Sources):生成正弦波

Add(Simulink->Math Operations):加法器

Zero-Order Hold(Simulink->Discrete):零阶保持器

Scope(Simulink->Commonly Used Blocks):示波器

Spectrum Analyzer(DSP System Toolbox->Sinks):频谱分析仪

这里给出了设计中用到的所有block在库中的路径,后文不再提及(同一block会包含在多个库中,为了寻找方便这里只列出一个路径)。

System Generator设计流程

新建一个文件夹,启动System Generator,建立一个空的simulink模型(sysgen_filter.slx)。设置一个1MHz+9MHz的正弦叠加信号,使用FIR低通滤波器滤除9MHz频率分量,系统采样率为20MHz。

1.生成正弦信号

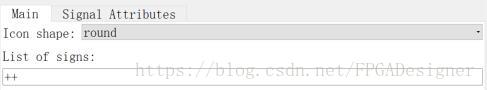

在库中找到Sine Wave,添加两个到model中,一个产生1MHz正弦波,另一个产生9MHz正弦波。

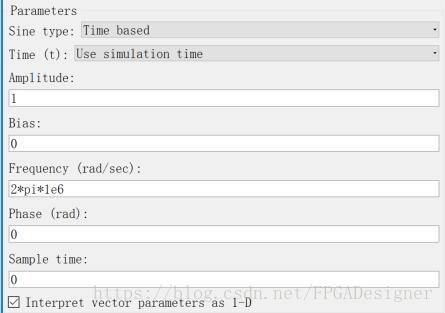

双击Sine Wave,可以设置正弦波的幅度、电平偏置、频率、初相、采样时间等信息。这里只需要将频率分别设置为1MHz(2*pi*1e6)和9MHz(2*pi*9e6)。两路信号的叠加需要使用加法器,添加一个Add到model中:

“List of signs”设置加法器的输入端口,“++”表示两个输入相加(“+-”则表示A-B)。

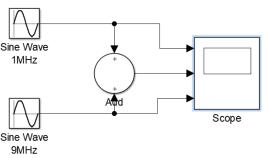

为了确保模块输出信号正确,添加一个Scope观察信号波形。双击打开示波器窗口,在View->Configuration Properties:Scope中,将Number of input ports设置为3(观察3路信号);点击Layout,选择3*1排列方式(每路信号分开显示):

此时模型的连接图如下所示:

将Simulink仿真时间设置为0.00001(时间太长会导致仿真很慢),点击运行,Simulink窗口的右小角可以观察到运行状态。运行结束后打开Scope:

第一个为1Mhz信号,第三个为9MHz信号,中间为两路信号叠加。接下来设计一个LPF滤除掉9MHz频率分量。

2.数字滤波器设计

我们知道,Simulink中的仿真模型为连续时间系统,数据格式多种多样;而FPGA中为离散时间系统,数据必须用一定的位数进行量化。两者之间必须要进行从连续到离散的转换、数据格式的转换,否则无法进行正确的FPGA设计。Xilinx Blockset中提供了相应的解决方案。

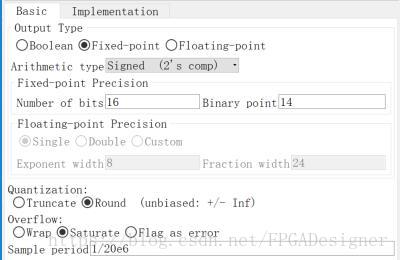

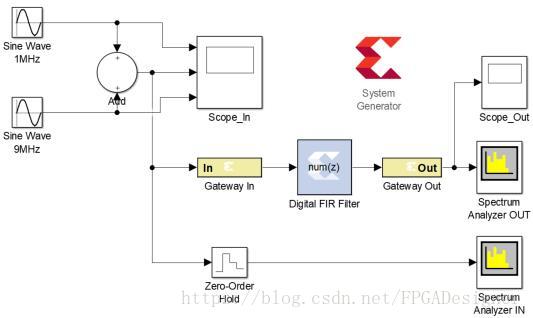

添加一个Gateway In和一个Gateway Out模块到model中,再添加一个Digital FIR Filter模块。按照加法器输出->Gateway In->Digital FIR Filter->Gateway Out的顺序依次连接。双击打开Gateway In模块的属性窗口:

这个模块可以Simulink到FPGA之间的数据转换。将Sample period设置为“1/20e6”(20MHz采样率),完成连续时间到离散时间的转换;设置Out Type完成数据格式的转换。这里保持为默认的二进制带符号数补码、定点数的设置。Quantization中可以设置量化方式为Truncate(截断)或者round(四舍五入)。

Gateway In的设置会自动传递到Gateway In和Gateway Out之间的整个系统中,因此不需要再设置其它模块的采样率与数据格式。

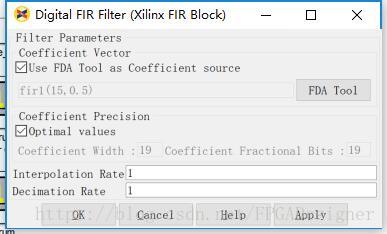

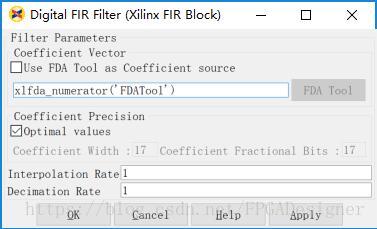

双击Digital FIR Filter:

FIR滤波器的系数可以使用fir1等MATLAB函数设计,也可以使用FDATOOL工具设计。选中“Use FDA Tool as coefficient source”,点击“FDA Tool”按钮,会弹出FDATOOL窗口,设置采样率为20Mhz,通带截止频率1.5MHz,阻带截止频率8.5Mhz,通带衰减0.01dB,阻带衰减100dB,点击“Design”设计后退出。

3.FPGA系统配置

以上仅仅是完成了数字滤波器的设计,但是仍然没有建立起模型与FPGA之间的实质联系。添加System Generator模块到model中,这个block便是配置与FPGA相关的系统参数。这个block的配置会应用到Gateway In和Gateway Out之间的所有模块中。双击打开,切换到Clock标签:

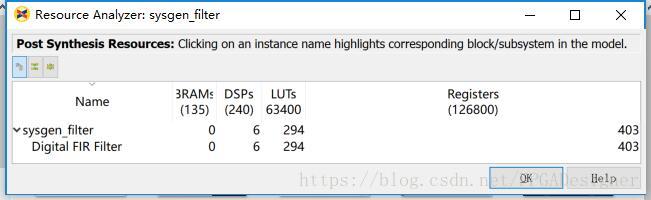

FPGA clock period设置为50ns,Simulink system period设置为1/20e6(都是20Mhz)。Perfor analysis设置为Post Sythesis,Analyzer type设置为Resource,在系统综合后会进行资源使用情况的分析。

4.系统仿真

使用Simulink完成FPGA中的DSP系统设计,最大的好处就是仿真极其方便(包括后面文章会用到的ModelSim协同仿真、硬件协同仿真等特性)。

添加一个Scope观察Gateway Out输出的波形(滤波后波形),再添加两个Spectrum Analyzer观察滤波前后的信号频谱。Spectrum Analyzer这个block必须输入离散的数据,因此在加法器输出后需要经过一个零阶保持器Zero-Order Hold,转换为离散数据后再输入到Spectrum Analyzer中。零阶保持器的采样率设置为1/20e6(20Mhz)。

系统的整体连接框图如下:

注意,虽然Gateway In转换后的数据也是离散的,但是Spectrum Analyzer不能接入到这里,否则会出现错误。Gateway In和Gateway Out之间只能连接其它Xilinx Blockset中的模块。

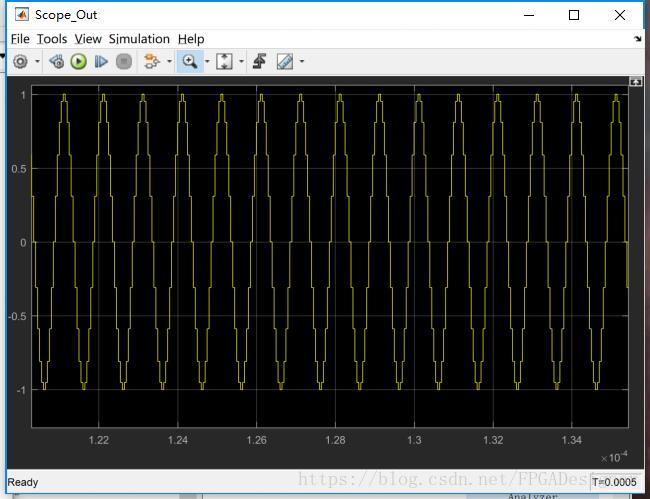

将仿真时间设置为0.0005(Spectrum Analyzer必须有足够多的采样数据才能计算出频谱),输出信号的波形如下所示:

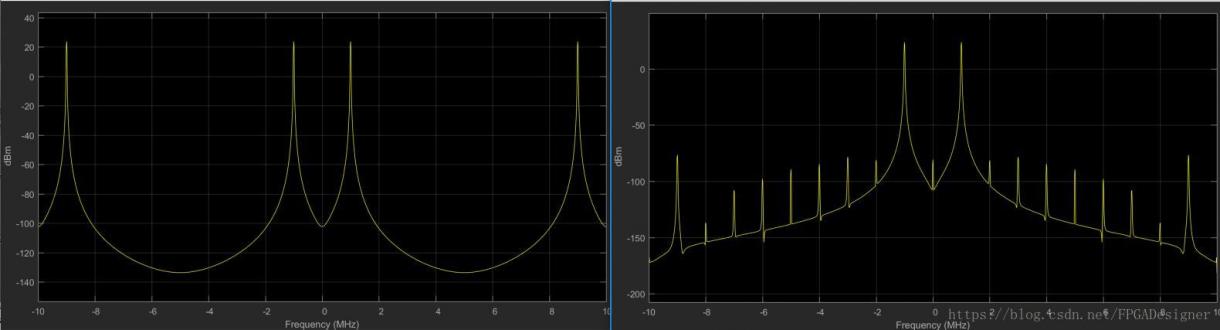

经过滤波后仅剩下1MHz的单频分量,且数据为离散值。信号滤波前后的频谱对比如下图所示:

可以看到经过滤波后,9Mhz的频率分量有大约100dB的衰减(频谱呈对称性),设计符合预期。

5.将设计导出到FPGA

仿真验证功能正确后,需要将设计导出到FPGA中,这个步骤仍然要借助System Generator这个block。双击打开,切换到Compilation标签下:

这里可以设置使用的开发板(Board,只能选择Xilinx官方开发板)、FPGA芯片(Part),也可以设置导出设计的硬件描述语言(Verilog或VHDL)。点击“Generate”,System Generator会将Gateway In和Gateway Out之间的模块导出到FPGA中。运行结束后,根据前面的设置,弹出了资源分析报告:

在slx同文件夹下,生成netlist文件夹。其中sysgen子文件夹包含了导出的Verilog或VHDL设计文件;ip子文件夹是设计导出的IP核形式;ip_catalog子文件夹包含一个调用该IP核的Vivado的示例工程。

打开Vivado示例工程

用Vivado打开ip_catalog下的工程,顶层模块代码如下:

`timescale 1 ps / 1 ps

module sysgen_filter_bd_wrapper

(clk,

gateway_in,

gateway_out);

input clk;

input [15:0]gateway_in;

output [35:0]gateway_out;

wire clk;

wire [15:0]gateway_in;

wire [35:0]gateway_out;

sysgen_filter_bd sysgen_filter_bd_i

(.clk(clk),

.gateway_in(gateway_in),

.gateway_out(gateway_out));

endmodule

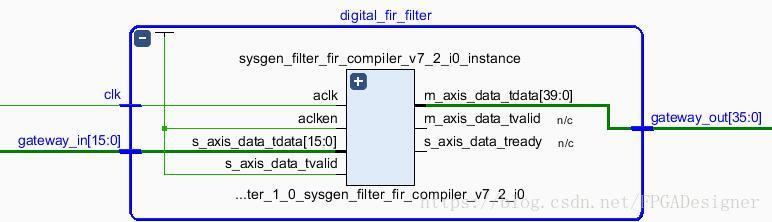

sysgen_filter_bd是调用System Generator导出的IP核的子模块。16Bits输入数据经过滤波后得到36Bits的输出结果。运行RTL ANALYSIS,打开RTL视图,找到最底层:

可以看到其本质上仍然是调用了FIR Compiler IP核来实现数字滤波,只不过我们是在Simulink中完成的设计。在其它工程中可以像示例工程一样调用这个System Generator导出的IP核,来完成特定的DSP系统功能。

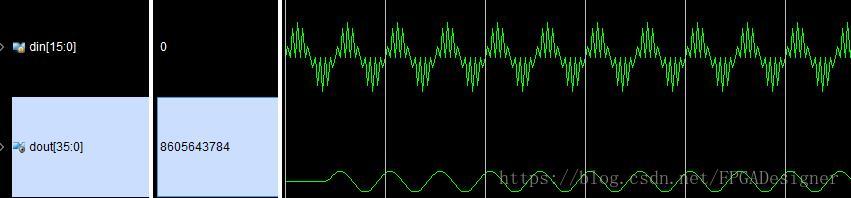

理论上经过Simulink中的仿真,已经可以确定设计的正确性。但这是使用System Generator完成的第一个实验,本文仍然在Vivado中进行一次仿真,增强使用者对System Generator设计的信心。使用MATLAB产生一个1MHz+9Mhz的正弦叠加信号,导入到TXT文件中。编写testbench读取txt文件,对信号进行滤波。Vivado中的仿真结果如下图所示:

可以看到经过滤波后,只剩下1Mhz的单频信号,与Simulink中的仿真结果完全一致。

总而言之,从这个实验出发,博主认为在System Generator中完成DSP系统设计与直接在Vivado环境下进行DSP系统设计相比,有两个优点:

1. 更强大、更方便的仿真环境;

2. 系统级设计角度,无需关心RTL设计细节以及一些IP核的具体使用方法。

在后面的文章中将记录更多、更复杂的DSP系统设计。

FDATool block的使用

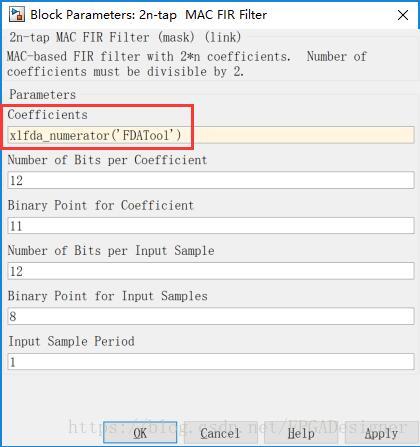

前文中我们在Digital FIR Filter block的配置界面直接调用FDATool工具完成FIR滤波器的设计。但是有一些滤波器block,如2n-tap MAC FIR Filter,并没有提供这样一个接口。Xilinx Blockset中单独提供了一个FDATool block,可以提供更广泛的使用。

添加FDATool block到model中,配置完成后点击“Design Filter”。其它模块调用这个FDATool设计的滤波器可以借助两个函数:

对于FIR滤波器而言,分母为1,只提取分子即可。如下图所示:

所有滤波器block的系数都可以用这种方式设置。

文章来源:FPGADesigner的博客

*本文由作者授权转发,如需转载请联系作者本人