作者:Kevin Zhang

在学习FPGA一段时间之后,昨天和师兄交流面试题,题目中问CLB、LUT的概念,我都是不知道这是什么?经过学习,总结如下内容:

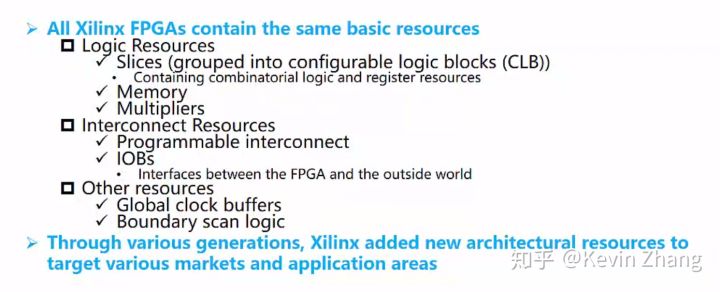

FPGA可以分为以下三种资源:

1. 逻辑资源:包含CLB,block rams,乘法器

2. 连接资源:可编程互联线、IOB

3. 其他资源:全局时钟网络;

4. 当然高端的FPGA除了以上三种资源,还有集成了其他资源:ARM核、PCIE核、MIG核等等

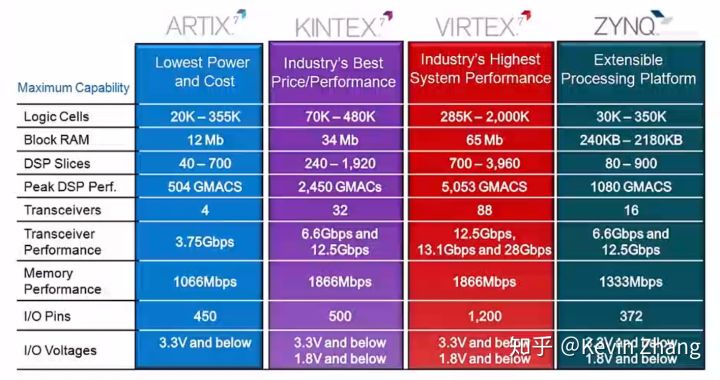

7系列FPGA的资源量介绍如下图:

基本可以认为资源量:VIRTEX > KINTEX >ARTIX

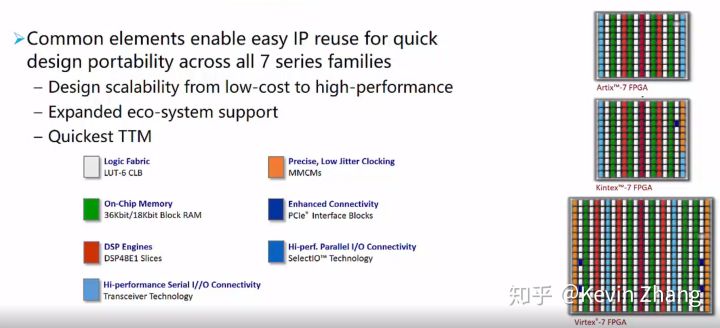

7系列中,FPGA的架构都是相同的:

这带来一个好处:IP核的使用,是一致的,不用额外修改代码,这给使用vivado的用户带来了很多福音。

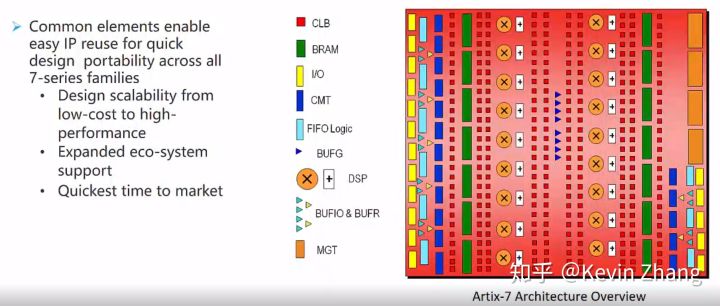

7系列FPGA资源详细解释:

CLB:逻辑配置

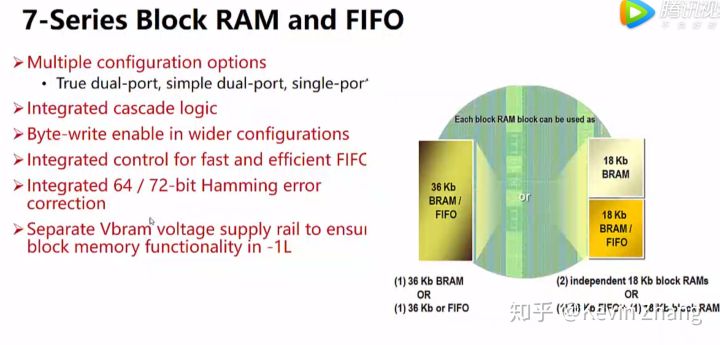

BRAM:BLOCK RAM 可以用来作为 FIFO RAM ROM

I/O:输入输出

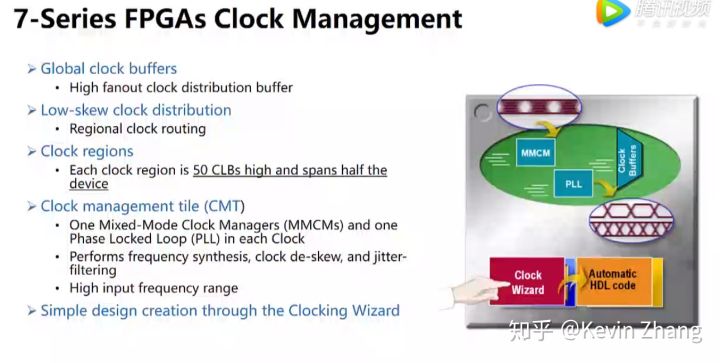

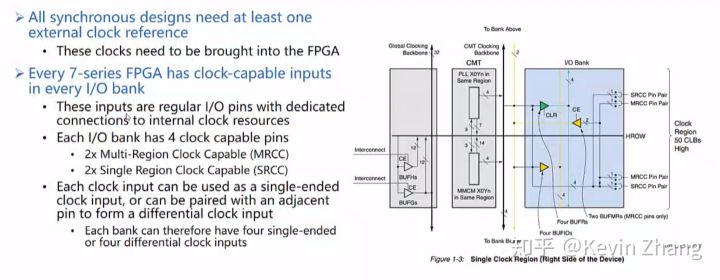

CMT:时钟管理

BUFG:全局时钟缓冲器

DSP:DSP 加法器 乘法器

BUFR:用于纵向3个BANK时钟缓冲器

BUFH:用于横向BANK时钟缓冲器

BUFIO:用于IO输入输出缓冲

MGT:高速串行收发器

补充:疑问什么有了BUFG还要使用BUFH、BUFR的必要性?

在我问了金师兄这个问题后,师兄用他深厚的工程经验告诉我,因为BUFG的资源是有限的,在FPGA中仅有12个BUFG的资源。MIG核用了3个、SATA用了几个、SRIO用了几个、全局时钟资源是不够使用的。因此要合理分配时钟资源,MIG核就可以使用BUFR或者BUFH,减少BUFG资源的浪费,师兄还告诉我,可以使用原语对资源量进行分配。在此感谢师兄的指导。

现在来看一下逻辑资源的部分:

CLB(可配置逻辑块): 一个CLB由两个Slices和开关矩阵构成。SLICE用来实现基本的组合逻辑和时序逻辑功能。

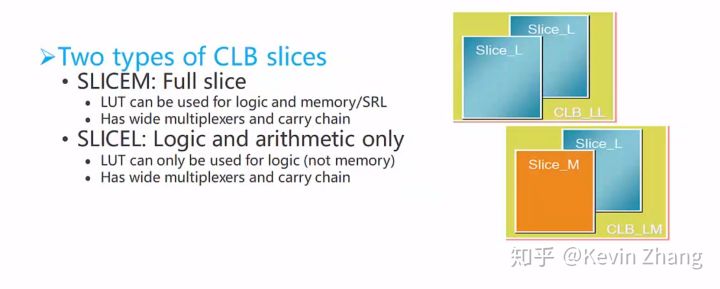

Slice可以分为两种:

SLICEM: MEMORY,可以实现组合逻辑和时序逻辑之外,还可以被用来实现存储的功能,例如分布式RAM;

SLICEL:LOGIC only,仅仅用来实现组合逻辑和时序逻辑,不能实现存储器的单元。

LUT:查找表在这里可以认为是真值表

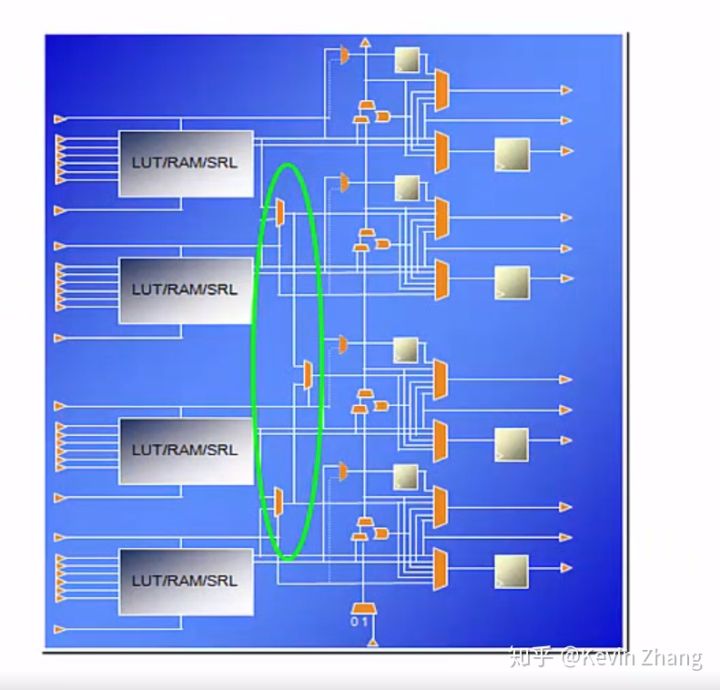

一个SLICE的构成:

1. 4路查找表;

2. 多路复用器:图中绿色框

3. 8触发器(4大4小,右侧的四个大的可以作为锁存器)

4. 进位链的逻辑;都是上行的进位链,FPGA都是自下往上的逻辑,因此逻辑电路构成都是自下向上,因此不能使用过深的计数器。如果进位链太高,会导致时序不达标。解决此问题,将大的计数器设计成多个短的计数器,通过使能信号进行级联,实现同样功能,使用同样的参考时钟。(注意不用使用进位信号做为时钟)

触发器:要尽量写同步电路,在一个slice中有8个触发器单元,他们共享时钟、复位、使能信号,因此他们只能有一个相同的时钟。如果不同,他们不能放进同一个SLICE。尽量使用相同的相同的控制信号和时钟信号,可以降低资源利用率。

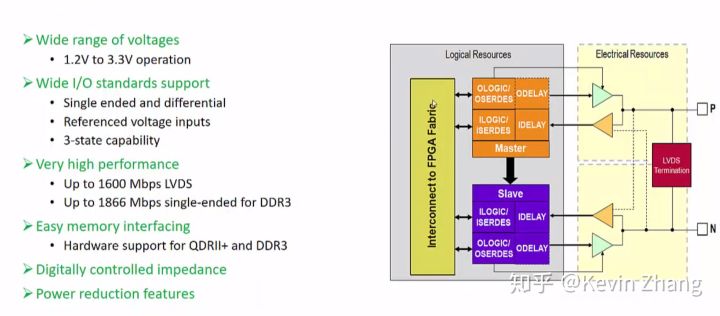

1. 电气部分:1.2V~3.3V 差分

2. 逻辑部分:Idelay Odelay sedes

3. HR BANK:可以支持到3.3V

4. HP BANK:高速设计,最高电压1.8V

这里补充一下,金师兄对我另一个指导:

1. IDELAY ODELAY IODELAY的作用? 师兄举了小SAR板子的一个例子,因为高速ADC的数据速率很快,但是因为是并行的传输,因为PCB走线、工艺的影响,会产生数据与时钟无法对齐的问题,因此使用IDELAY 将数据与时钟对齐,就可以解决这个问题。在这里师兄又展示了他超凡的智慧:调节时钟的IDELAY与数据的IDELAY有什么不同?这个问题确实很有意思,因为调节时钟的delay,工作量小一点,但是可能因为数据的偏移可能过大,导致无法解决数据的对齐问题。如果调节数据的IDELAY,对于每个数据都要调节,工作量大一些,但是是一定可以调节出来的。

2. BUFIO的作用?因为整个FPGA内部逻辑使用的电压是VCC_INT,但是VCCIO使用的电压肯能是3V3、1V8,这个BUF可以用来用来转换电压等作用。就像是BUFG其实也是转换了时钟的区域。

DSP资源

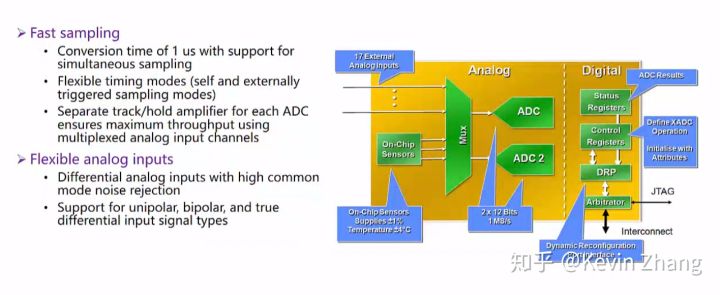

XADC

时钟资源

FPGA底层的内容还有很多,不知道的内容还有很多,还需要很多的研究。