第一章 FPGA基础及电路设计

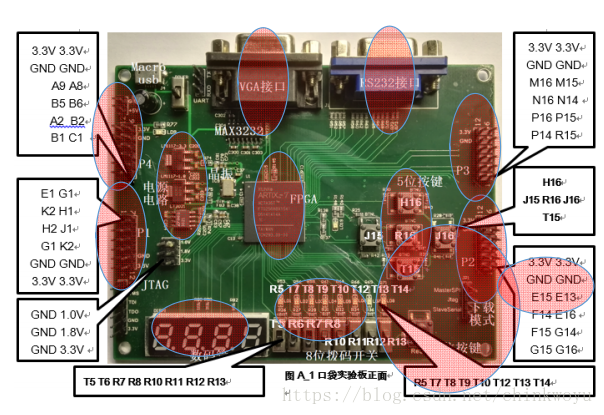

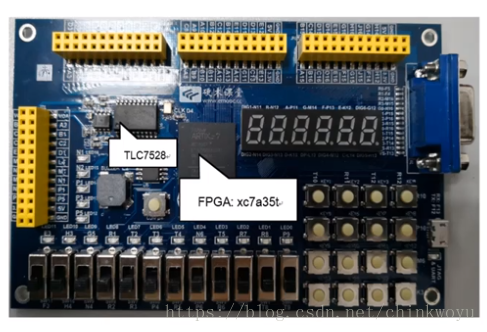

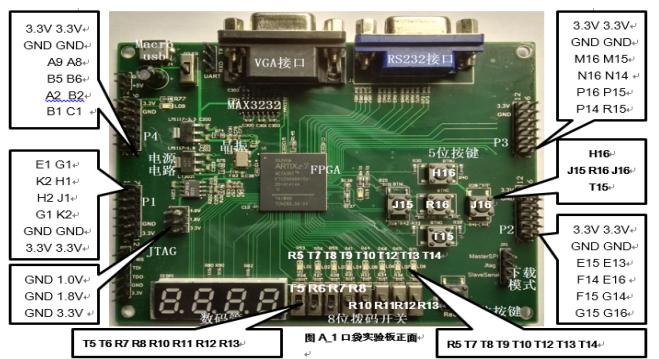

FPGA基础及电路设计包含两个方面的内容,一个是FPGA基础及7系列FPGA基本原理,另外就是FPGA电路设计,FPG广泛应用于军事、医疗、工业、通信等领域,下面是两款实验板:

FPGA基础及7系列FPGA基本原理

FPGA概述

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA的应用面非常广泛,这里主要介绍Xilinx Artix-7系列芯片:

Xilinx Artix-7 系列器件以28纳米高性能低功耗 ,尤其适合于可满足航空电子和通信等领域的尺寸、重量、功耗和成本敏感型市场需求。提供大量的可供开发者直接使用的IP核,是市场的主流。

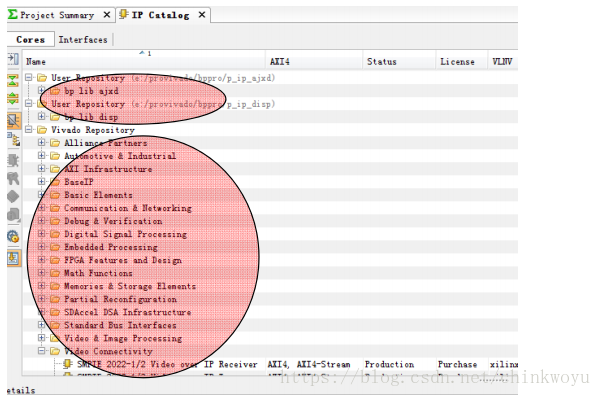

下图是开发软件VIVADO的截图,可以看到一些IP核,用户也可以自己设计IP核

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。

一个出厂后的成品FPGA的逻辑块和连接可以按照设计者的设计而改变,所以FPGA可以完成所需要的逻辑功能。

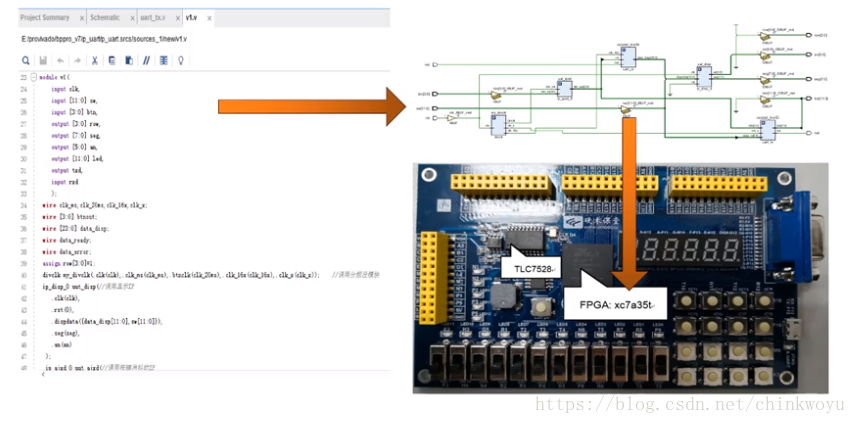

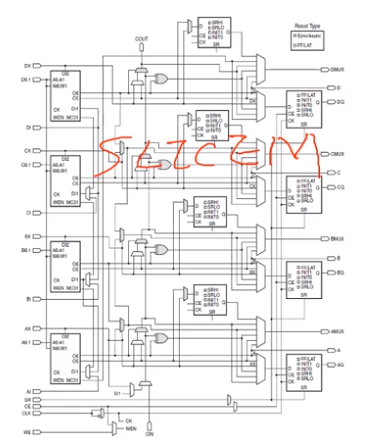

下图是一个Verilog HDL语言的一个实例,Verilog HDL语言就是对电路功能的一个描述,通过具体分析可以看到具体实现的电路,就可以将这个电路下载到FPGA里面,让FPGA实现我们描述的功能

FPGA基本逻辑结构

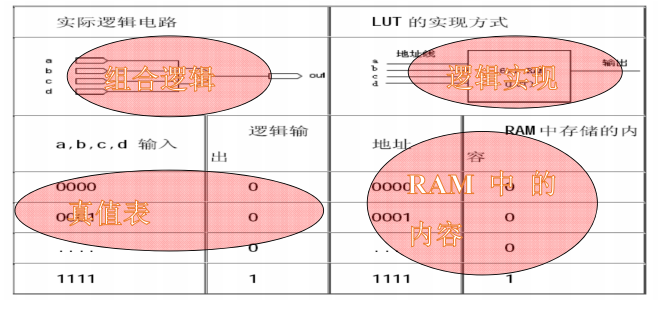

现场可编程门阵列FPGA是可编程器件,与传统可编程器件如PAL、GAL、CPLD等相比,FPGA有不同的结构,FPGA是利用小型查找表、小的RAM来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或IO,由此构成即可实现组合逻辑功能和时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线连接或连接到IO输入输出模块,通过向内部静态存储单元加载编程数据,就可以实现组合逻辑,再通过与触发器配合,就可以实现时序逻辑,这些都是可编程的,最终决定了FPGA的所有功能实现。对FPGA的配置信息被保存在配置存储器中,并在上电和复位的瞬间对FPGA进行配置。

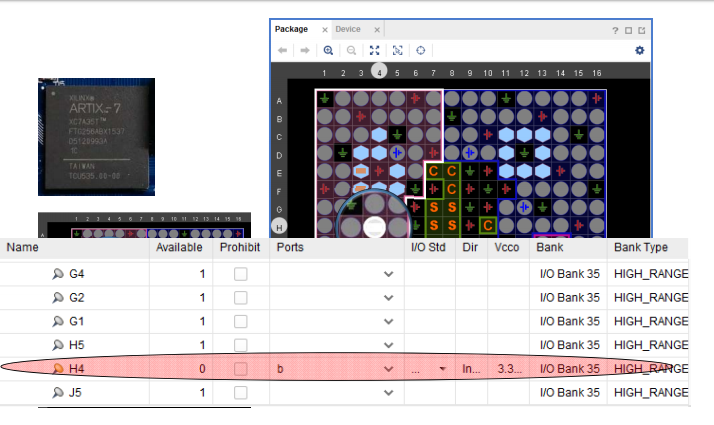

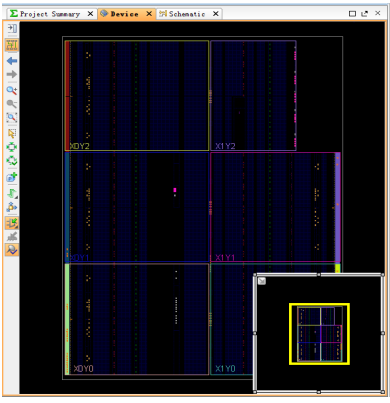

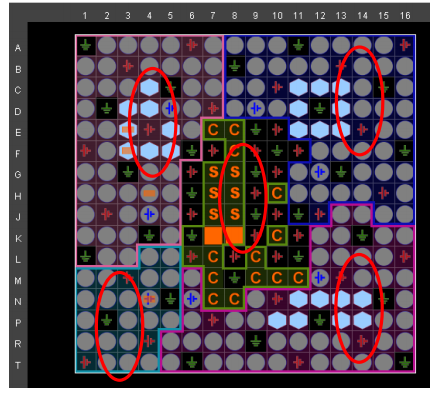

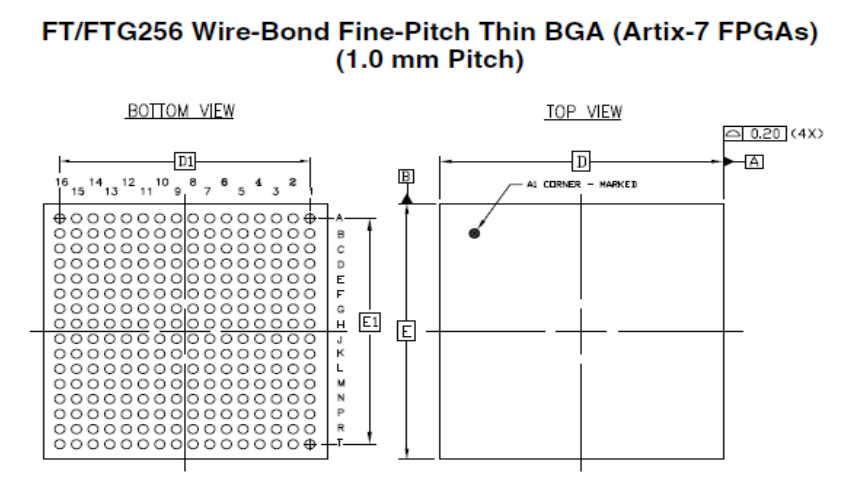

下面是一款Xilinx Artix-7 xc7a35t的芯片,封装型号为ftg256,在VIVADO下可以看到他的封装是16*16的256个管脚

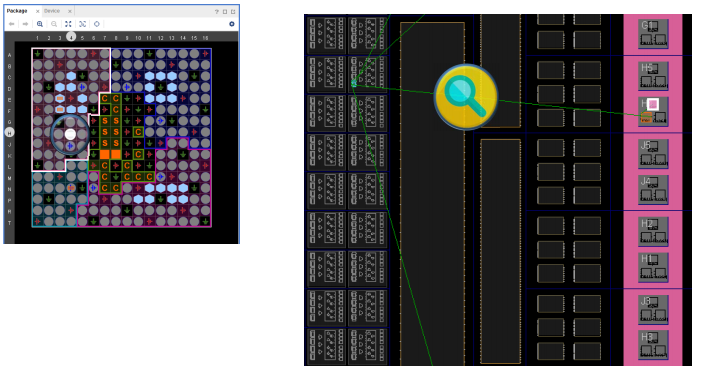

放大之后可以看到逻辑单元和相应的管脚信息

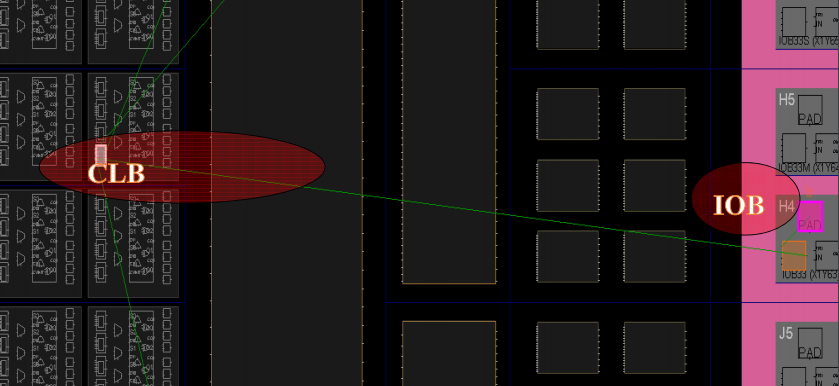

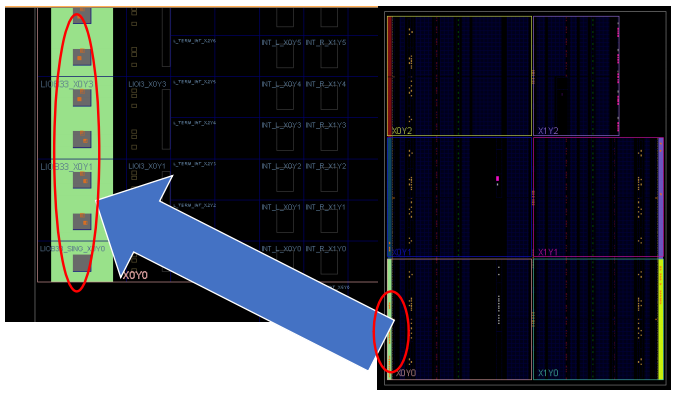

每个CLB由两个Slice组成,Xilinx FPGA采用了阵列逻辑单元LCA(Logic Cell Array)概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

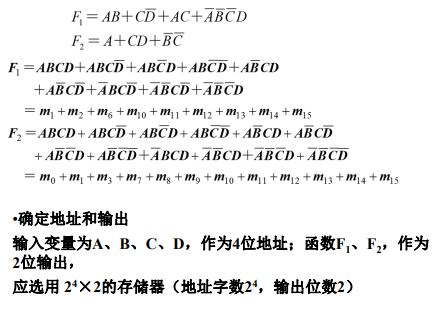

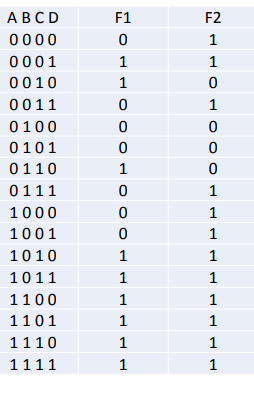

要掌握FPGA基本逻辑结构,就要掌握LUT是如何实现的,FPGA是通过查找表LUT实现逻辑函数的

例1:用一个LUT实现如下函数

于是可以构建出如图所示的真值表

7系列FPGA CLB

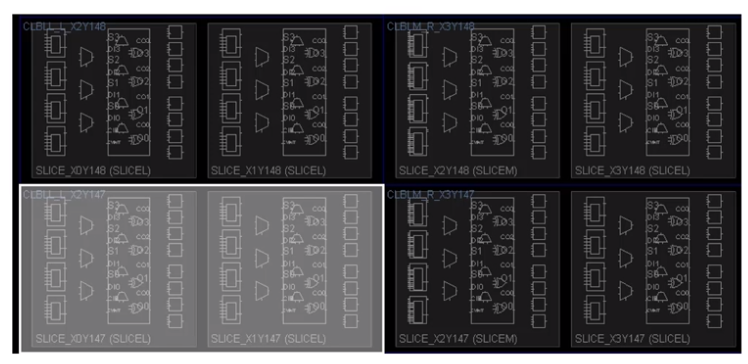

Artix-7系列的FPGA,型号为xc7a35t,在Artix-7中处于中端。它包含 5200个SLICE,其中3600个SLICEL,1600个SLICEM。每个SLICE包含4个6输入查找表LUT,共有20800个查找表。Artix-7A35T可以分配400Kb的分布式RAM,200Kb的移位寄存器,41,600个触发器。

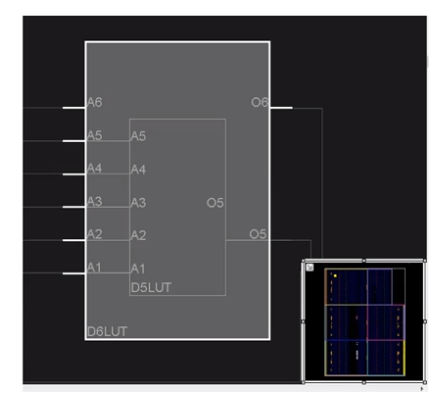

通过查找表LUT实现逻辑函数,7系列的FPGA,每个查找表LUT都有6输入和两个独立输出。

当实现6输入逻辑函数时,A1-A6为输入,O6为输出 ,当实现两个小于等于5输入的逻辑函数时,A1-A5为输入,O6为输出,A6拉高。

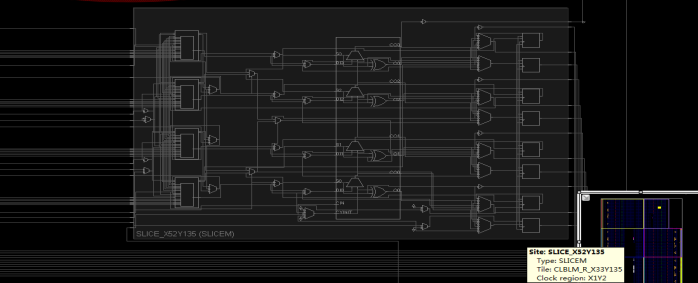

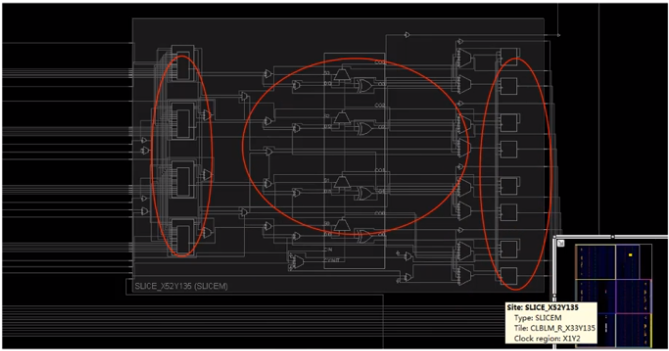

在图中我们可以看到,每个CB由两个SLICE组成

每个SLICE包含4个LUT及8个存储元件及其他组合逻辑

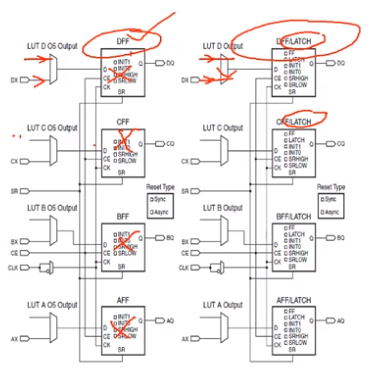

每一个SLICE具有8个存储元件,右边的4个可以配置为锁存器或触发器,左边的4个只能配置为触发器。其中右侧的4个存储元件的输入通过多路开关选择,可以使用对应的查找表输出,或者外部的输入。

另外的四个之鞥呢配置为D触发器。这4个D触发器的输入可以是查找表LUT的输出,也可以是外部的输入。

额外的规定是,当右边的存储元件被配置为锁存器,这4个触发器不能被使用

SLICE在FPGA 7系列体系结构分为两类:能够实现补码运算、移位寄存器、存储器功能的SLICE,成为SLICEM。它的功能相对较为复杂

而查找表只能实现基本逻辑函数的,成为SLICEL,逻辑结构相对比较简单

通常采用全功能SLICEM结合简单功能的SLICEL配合使用,使芯片在保持能力和性能的同时,实现低功耗和低成本。

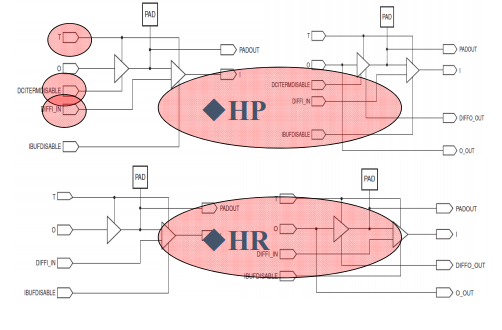

7系列FPGA IOB

CLB能够实现FPGA的功能,但是要和外界进行数据传输,就必须要有和外界电平兼容的IO接口IOB(Input Output Block),IOB的数量主要取决于芯片引脚的数量,通常对IOB的配置可以配置FPGA引脚的电气特性,甚至可以配置上拉和下拉模式,可以达到与大多数电平的兼容。

7系列FPGA具有多个IOBANK(可以理解为IO的分组),每个BANK具有50个IOB, 具体的 BANK的数量取决于FPGA的尺寸和封装。

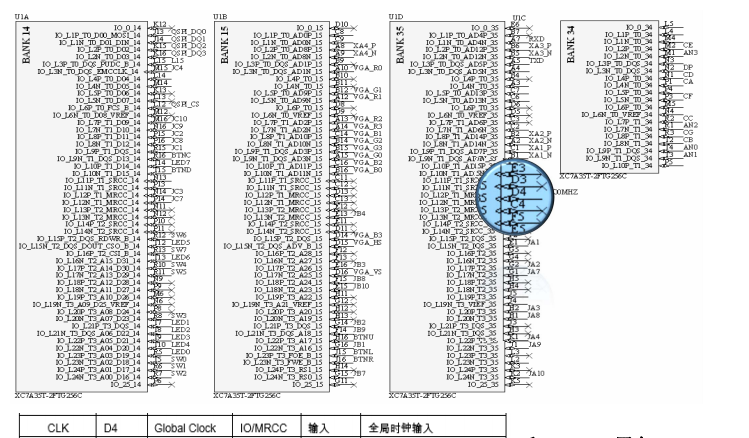

XC7K325T具有10个I/O BANK,xc7a35tftg256-1因为有256个管脚,具有4个IO BANK。分别是BANK14、BANK15、BANK34和BANK35,其中BANK34只有部分管脚是可用的。

在下入中我们可以看到IOB的具体信息

IO管脚可以配置多种输入输出标准,当配置为单端模式,例如按键输入、LED驱动等,可以设置为LVCMOS,、LVTTL、HSTL、 PCI、 SSTL电平标准。

当选择差分输入输出模式(2个IO管脚差分输入或输出),可以设置为LVD,、Mini_LVDS、 RSDS、PPDS、BLVDS,以及差分 HSTL和 SSTL标准。

7系列的FPGA管脚还分为高效管脚HP(high-performance)和宽范围HR(high-range)管脚

T信号用于控制输入输出三态DCITERMDISABLE设置DCI功能无效DIFFI_IN用于设置是否采用差分模式。在大多数的7系列FPGA器件中,在每一个BANK的最后两个管脚是仅单端模式的,其他的管脚都可以配置为单端或差分模式。

7系列FPGA及7a35tftg256-1特性

速度等级

Artix-7 FPGA可选- 3、- 2、- 1、- 1l,和-2l速度等级,其中-3等级具有最高的性能。

Artix-7 FPGA主要操作在1.0V内核电压,器件xc7a35tftg256-1具有-1的速度等级。

电压

7a35tftg256的内核电压VCCINT电压最大1.1V,通常工作在1.0V。

FPGA电路设计

基于Xilinx xc7a35tftg256-1的电路板为配合FPGA学习使用, 加上一台笔记本电脑就可以完成口袋实验室的搭建。掌握FPGA的基本电路设计,对于FPGA的功能设计与实现是必须的。例如进行约束时需要对应到管脚,要点亮LED就必须知道并在工程中描述接口关系。

某宝上也有大量的实验开发板可以选择,根据个人喜好可以进行选择,这里不做推荐,避免广告嫌疑。

xc7a35tftg256-1分为BANK14,BANK15,BANK35和BANK34四个BANK。不同的开发板对应不同的管脚,在开发板配套资料中会有相应的原理图,通过查看原理图可以找到相应的管脚

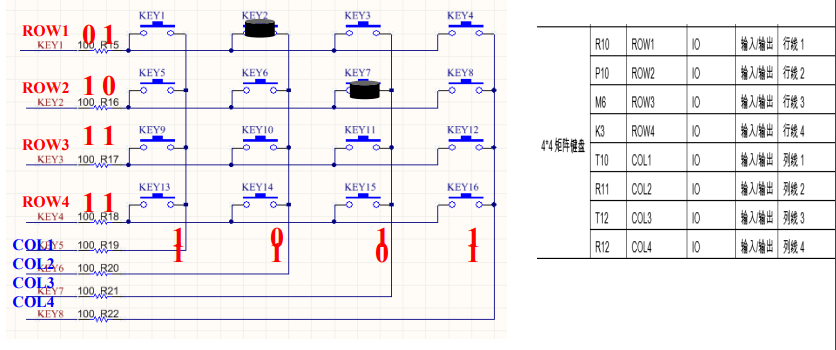

下面列出一些开发板上比较常见的资源管脚分配:

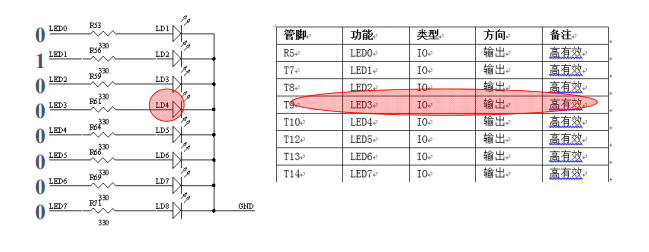

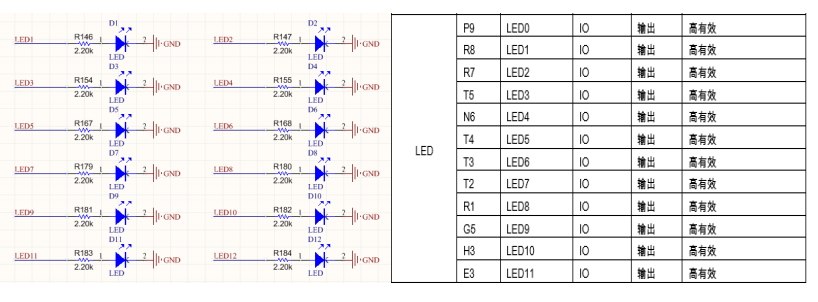

- LED

LED驱动电路非常简单,FPGA的输出I/O口的驱动能力足够驱动LED点亮

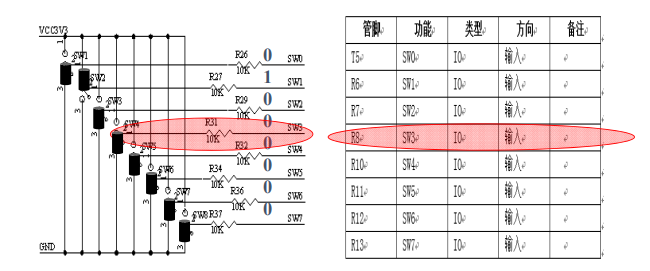

- 拨码开关

拨码开关(也叫DIP开关,拨动开关)是用来操作控制的地址开关

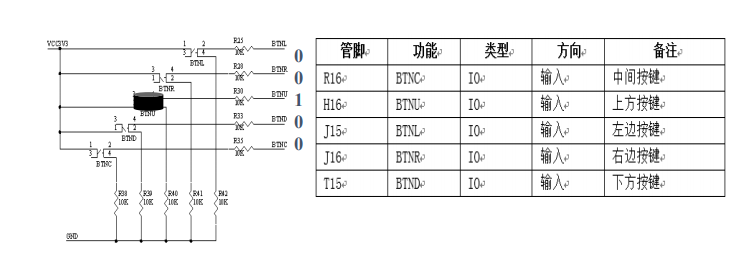

- 按键

按键是开发板必不可少的元件,不同的按键有不同的电气特性,根据电路图,当按键缺省状态时(未按下),对应管脚通过两个串联的10K欧姆电阻接地,获得低电平输入。当按键按下时,通过10K电阻接到电源,这时将得到高电平输入。

- 数码管

数码管的选择分为连体数码管和分布数码管,共阳极和共阴极的区别,驱动的方式也分为含有3-8译码器和不含3-8译码器的区别,使用3-8译码器可以节省芯片管脚资源

下面是电路板七段数码管驱动电路及管脚分配图

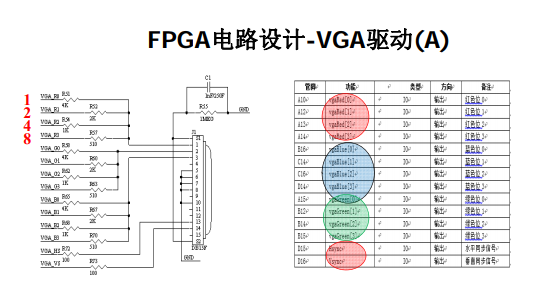

VGA驱动

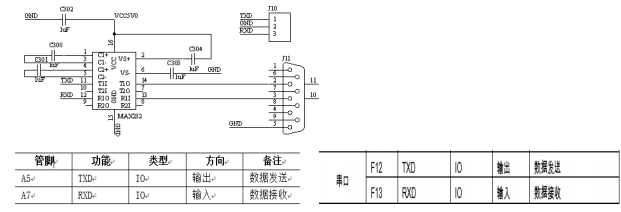

串口驱动

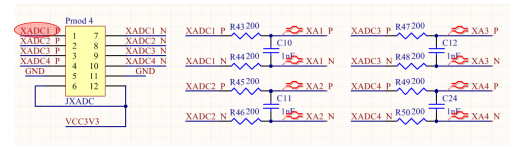

XADC

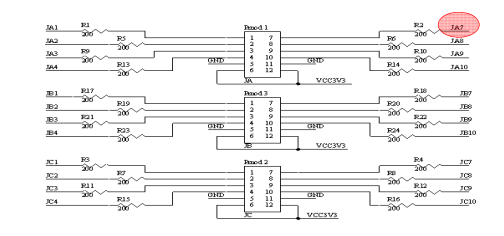

其他接口

文章来源:chinkwoyu