Silexica的FAE工程师周雋铠在上月结束的Xilinx Develper Forum展会上为大家展示了如何利用SLX工具充分发挥FPGA的优势,发现并行化机会,从而提高系统性能。想知道SLX到底如何运行的,请戳下面视频:

雋铠工程师表示,SLX软件工具的优势在于能够分析客户的软件,找出客户效能的Bottleneck(瓶颈),提供并行化的优化建议。

简单来说,SLX tool在分析用户的代码之后,会判别出哪个部分适合在FPGA上面运行,哪个部分适合在ARM上面运行。适合在FPGA上运行的话,会产生可以被赛灵思tool上辨识的HLS(High-Level Synthesis)代码,我们的工具产生的代码可以再通过赛灵思的tool去做实际上FPGA的Synthesize(合成)。在利用赛灵思的工具对FPGA做完性能分析之后,我们会通过SLX进行软件优化。

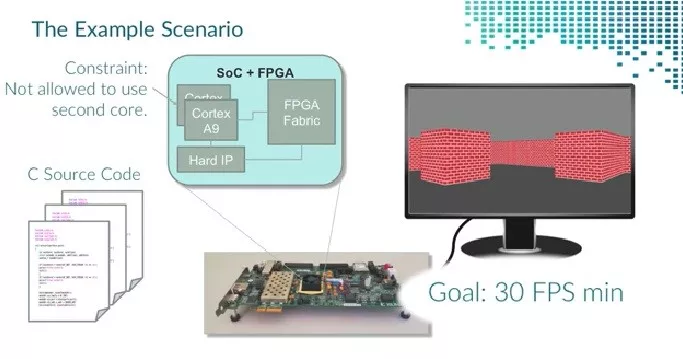

雋铠工程师在现场以一个的3D渲染小程序及Demo为例,具体演示了SLX是如何利用赛灵思的工具对客户软件做一些FPGA的分析的。用户在输入时是一个完全的C code代码,假设客户的目标是30 fps。

第一步:分析

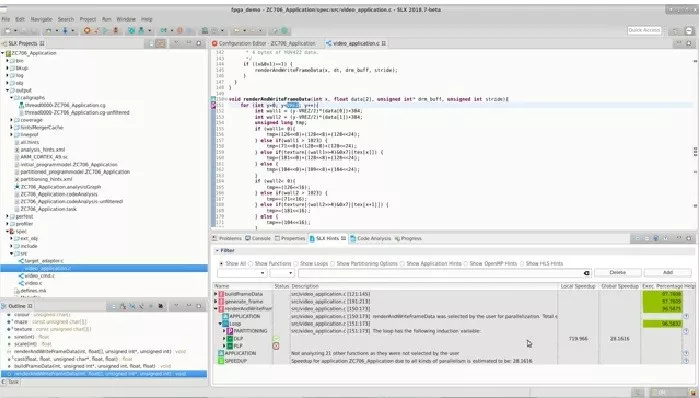

他说道,第一步,我们要知道软件的执行时间主要花在了哪些部分上,这就是所谓的Bottleneck(瓶颈)。这时我们可以利用slx工具来为程序的代码做分析。我们先在执行代码的加一个option,这个过程中我们可以看到每个function函数的调用关系是如何,比如从main()函数开始的调用关系。最关键的是找到软件执行的Bottleneck(瓶颈)。SLX的工具在显示这个调用关系图的时候,SLX的每一个方块代表一个function,每一个方块的颜色就代表了执行时间的比重,颜色越深代表执行时间所占比例越长。从视图里我们可以看出,不出意外地,在3D成像渲染部分所花费的时间是最长的。

刚才我们在代码的执行有加一个option,使得程序执行过程只是做一个frame帧的运算。我们可以看出,整个total cost是90ms毫秒左右。90ms算一个frame,那么整个fps大约在11fps左右(frame per second,每秒帧数)。

值得注意的是,虽然我们整套分析软件是在pc上运行的,但我们的效能数据是模拟的程序在FPGA主板运行上所能得到的效率。我们看到11fbs这个数值距离30fbs还有一段比较长的距离。这时我们考虑,是否可以通过板子上的FPGA来做系统的加速及优化。

第二部:优化

如果我们想要把一个function在硬件上做优化,其关键是它的并行程度。这时我们可以通过SLX的并行度分析工具,来分析出它的function内部有哪些部分适合来做并行化。运行完成以后我们可以看到SLX会针对我们刚刚看到的函数关系调用图当中的一些瓶颈function函数去做深度的分析。

最后我们来看build Freame Data()这个function函数。里面有个loop(循环),里面虽然有可能有一些并行化的机会,但通过SLX我们可以分析出这个循环中存在有一些的dependency依赖,如果不修改代码的话,这个循环是没有办法做并行化的。所以需要改code的话,然后来进行并行化。

想要观看SLX for FPGA的完全展示版,请点击"阅读原文",Silexica的FAE工程师Robert将为你展示更为详细具体的使用过程。