本篇主要介绍PCIe总线的复位方式。

PCIe总线规定了两个复位方式:Conventional Reset和FLR(Function Level Reset),而Conventional Reset又可以进一步分为两大类:Fundamental Reset和Non-Fundamental Reset。Fundamental Reset方式包括Cold和Warm Reset方式,可以将PCIe将设备中的绝大多数内部寄存器和内部状态都恢复成初始值;而Non-FundamentalReset方式为Hot Reset方式。

1、传统复位方式(Conventional)

传统的复位方式分为Cold、Warm和Hot Reset。PCIe设备可以根据当前的设备的运行状态选择合适的复位方式,PCIe总线提供多种复位方式的主要原因是减小PCIe设备的复位延时。其中传统复位方式的延时大于FLR方式。使用传统复位方式时,Cold Reset使用的时间最长,而Hot Reset使用的时间最短。

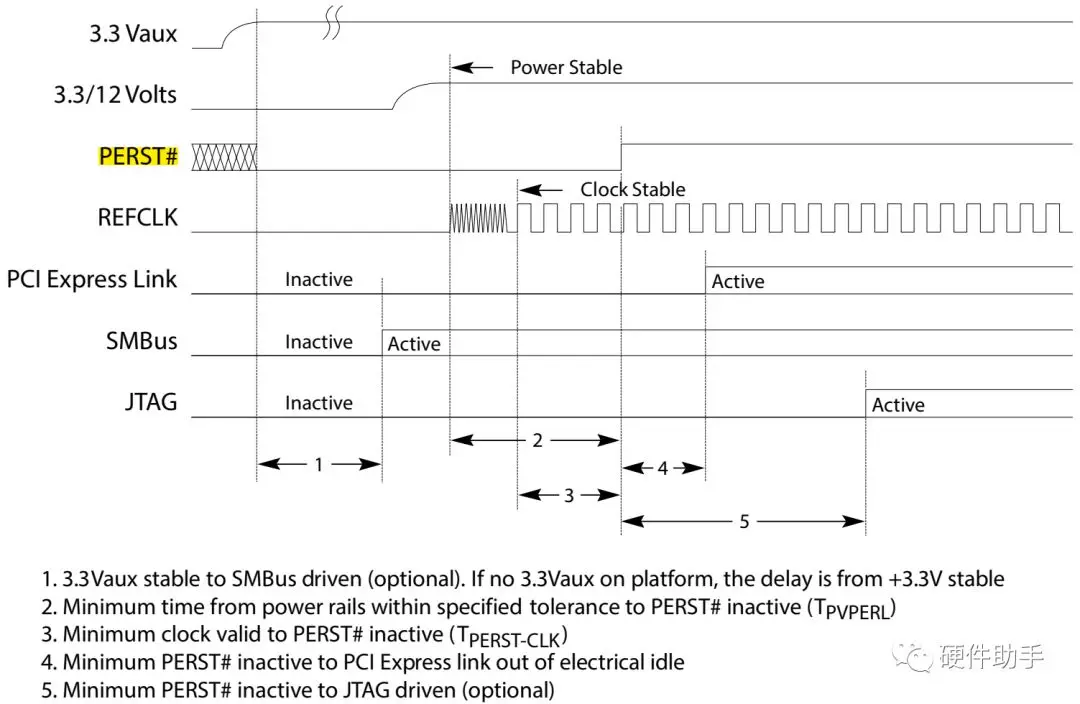

1.1、Cold Reset

当一个PCIe设备的Vcc电源上电后,处理器系统将置该设备的PERST#信号为有效,此时将引发PCIe设备的复位方式,这种方式属于Fundamental Reset。PCIe设备进行Clod Reset时,所有使用Vcc进行供电的寄存器和PCIe端口逻辑将无条件进入初始状态。但是使用这种方式依然无法复位使用Vaux(备用电源)供电的寄存器和逻辑,这些寄存器和逻辑只能在处理器完全掉电时彻底复位。

1.2、Warm Reset

在PCIe的设备完成上电后,也可能重新进行Fundamental Reset,这种复位方式也被称为Warm Reset。PCIe并没有定义Warm Reset的具体实现方式。

1.3、Hot Reset

当PCIe设备出现某种异常时,可以使用软件手段对该设备进行复位。如系统软件将Bridge Control Register 的Secondary Bus Reset位置为1,该桥片将secondary总线上的PCIe设备进行Hot Reset。PCIe总线将通过TS1和TS2序列对下游设备进行Hot Reset。

在TS1和TS2序列中包含一个Hot Reset位。当下游设备收到一个TS1和TS2序列,而且Hot Reset位为1时,下游设备将使用Hot Reset方式进行复位操作。

Hot Reset方式并不属于Fundamental Reset。PCIe设备进行Hot Reset方式时,也可以将PCIe设备的多数寄存器和状态恢复为初始值。

同时,在PCIe总线中,如果需要对链路的Link Width进行改变时,也将会用到Hot Reset。具体的流程如下:

Ensure the Link is in the L0LTSSM state.

Program the 6-bit “Link ModeEnable” field of the “Port LinkControl Register” on page 732. This isused bythe LTSSM in DETECT.

Programthe 9-bit “PredeterminedNumber of Lanes” field of the “Gen2 Control Register” on page 771. Thisindicatesto the LTSSM, the number of lanes to check for exiting from L2.IDLE orPOLLING.ACTIVE.

Trigger a Hot Reset, by settingthe Secondary Bus Reset bit in the RC Bridge ControlRegister (of the Type 1 PCIConfiguration Space Header) to 1.

Wait for 2 mS. The core’s LTSSMwill transition from L0 -> RCVRY -> HOTRESET.

Clear theSecondary Bus Resetbit. The core’s LTSSM will transition from HOTRESET -> DETECT.

2、FLR(Function Level Reset)

除了传统的复位方式之外,PCIe总线还提供了FLR方式。系统软件通过填写某些寄存器,如synosys的PCIe的IP是可以通过配置PCI ExpressCapability的DeviceControl Register的第16bit完成FLR。支持FLR方式的PCIe设备需要在其BAR空间中提供一个寄存器,当系统软件对该寄存器的Function LevelReset位写1时,PCIe设备将使用FLR方式复位PCIe设备的内部逻辑。FLR方式对PCIe设备是可选的。

在一个大规模的并行处理系统中,系统软件使用分区的概念管理所有硬件资源,包括处理器资源和所有IO资源,这些IO资源中通常会包含PCIe设备。在这种处理器系统中,任务在指定的分区中运行,当这个任务执行完毕后,系统软件需要调整硬件资源的分区。此时受到影响的PCIe设备需要使用FLR方式复位内部的逻辑,以免造成对新的分区的资源污染,并保护之前任务的结果。

当PCIe设备使用FLR方式进行复位时,有些与PCIe链路相关的状态和寄存器并不会被复位:

文章转载自:硬件助手