作者:OpenS_Lee

1 背景知识

在2010年4月硅谷举行的嵌入式系统大会上,赛灵思发布了可扩展处理平台的架构详情,这款基于无处不在的ARM处理器的SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力要求。赛灵思可扩展处理平台芯片硬件的核心本质就是将通用基础双ARM Cortex-A9 MP Core处理器系统作为“主系统”,结合低功耗28nm工艺技术,以实现高度的灵活性、强大的配置功能和高性能。由于该新型器件的可编程逻辑部分基于赛灵思28nm 7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的一致性,同时也方便日后本系列新产品的命名。

1.1 什么是SOC

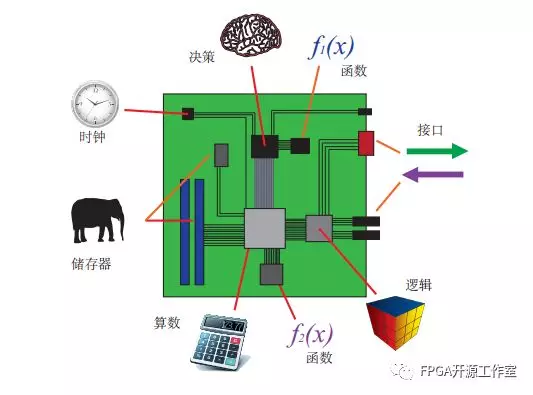

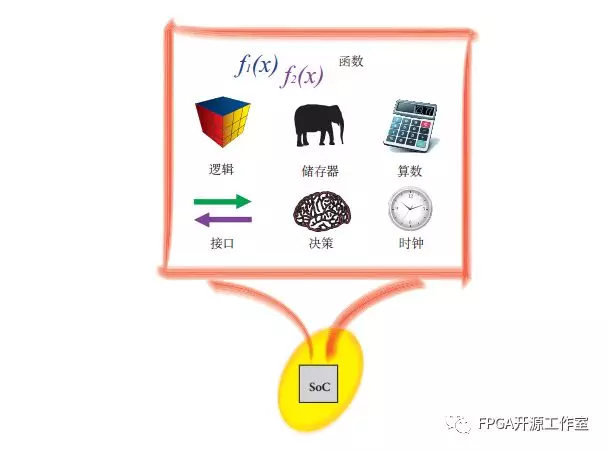

SoC这个术语常用于指专用集成电路(Application Specific Integrated Circuit,ASIC),它上面可以有数字的、模拟的和射频的元件,和混合信号模块组合起来来实现模拟 - 数字转换和数字 - 模拟转换(ADC 和 DAC)。单就数字部分而言,一块 SoC 可以组合上数字系统所有的功能:处理、高速逻辑、接口、存储器等等。所有这些功能也可以用物理上分立的器件来实现,然后在印刷电路板 (PCB)的层面上组合起来。SoC 的解决方案成本更低,能在不同的系统单元之间实现更快更安全的数据传输,具有更高的整体系统速度、更低的功耗、更小的物理尺寸和更好的可靠性。事实上有一大堆无可辩驳的理由来说明 SoC 比等价的分立元件系统要强!可以看一下图1和图2,这是关于板上系统和片上系统的简单图形化比较。

图1 板上系统

图2 片上系统

1.2 嵌入式 SoC 的简单剖析

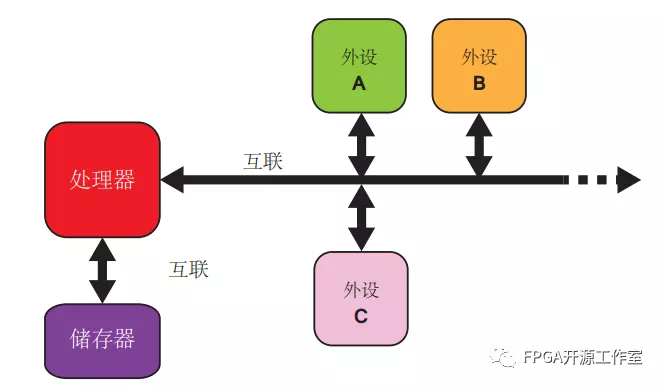

处理器可以被看作是硬件系统的中央单元。软件系统 (软件 “ 栈 ”)是运行在处理器上的,由应用程序 (通常是基于操作系统的)和一个更低的与硬件系统打交道的软件功能层组成的。系统单元之间的通信是通过互联进行的。这种互联可能是直接的、点对点链接,也可能是服务于多个单元的总线。如果是后者,就需要协议来管理总线访问。注意的是,尽管图 3 所示是有外设连接着的单一总线,但是一个处理器可以具有多个总线连接。

图3 嵌入式 SoC 的硬件系统架构

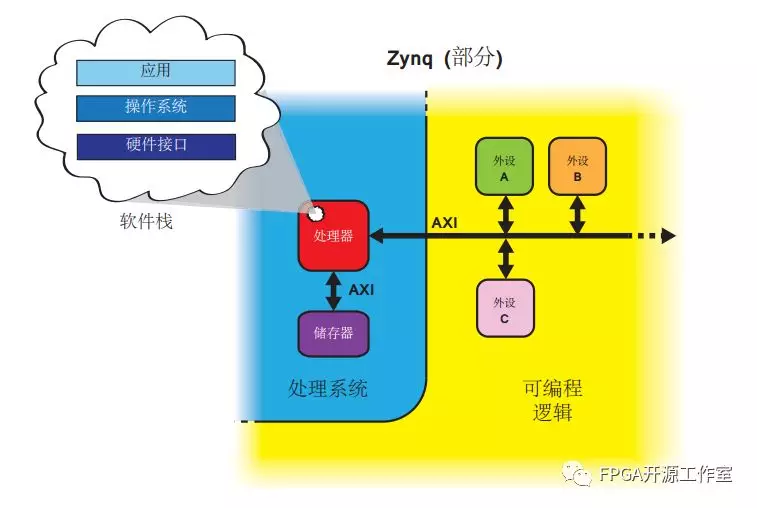

图 4 给出了把图 3 所示的硬件系统映射到图 2 所描绘的 Zynq 芯片上的样子两者的架构都被大大地简化了, 因为目前我们的目标只是从高层阐述嵌入式SoC是如何映射在 Zynq 芯片上的。PS 具有固定的架构,承载了处理器和系统存储区,而 PL 完全是灵活的,给了设计者一面 “ 空白画布 ” 来创建定制的外设,或重用标准外设。互联是通过连接了 PS 和 PL 的 AXI 接口来实现的。

图4 软件系统、硬件系统和 Zynq 架构之间的关系

2 硬件介绍

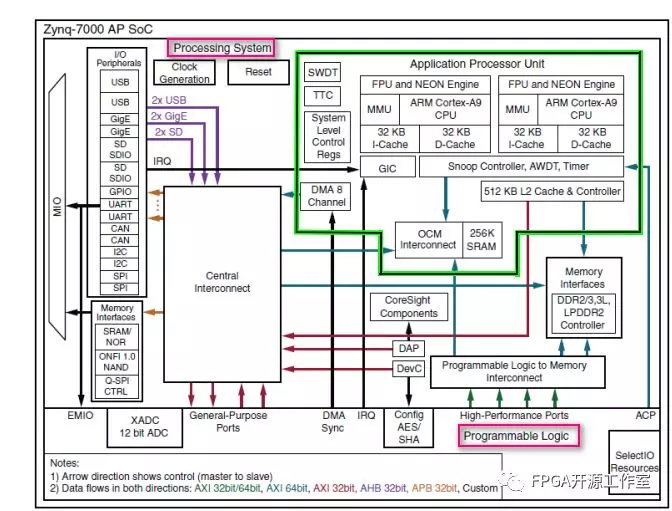

图5 Zynq 处理器系统

如图5所示,所有的 Zynq 芯片都有相同的基本架构。主要由两大部分组成PS(Processing System)和PL(Programmable Logic)组成。

2.1 PS端

作为处理器系统的基础,所有的芯片都包含了一颗双核 ARM Cortex-A9 处理器。 这是一颗 “ 硬 ” 处理器 —— 它是芯片上专用而且优化过的硅片元件。PS由APU(Application Processing Unit,APU )、扩展外设接口、存储器接口、互联接口、时钟发生电路、以及cache 存储器等电路组成。这里重点介绍一下APU。

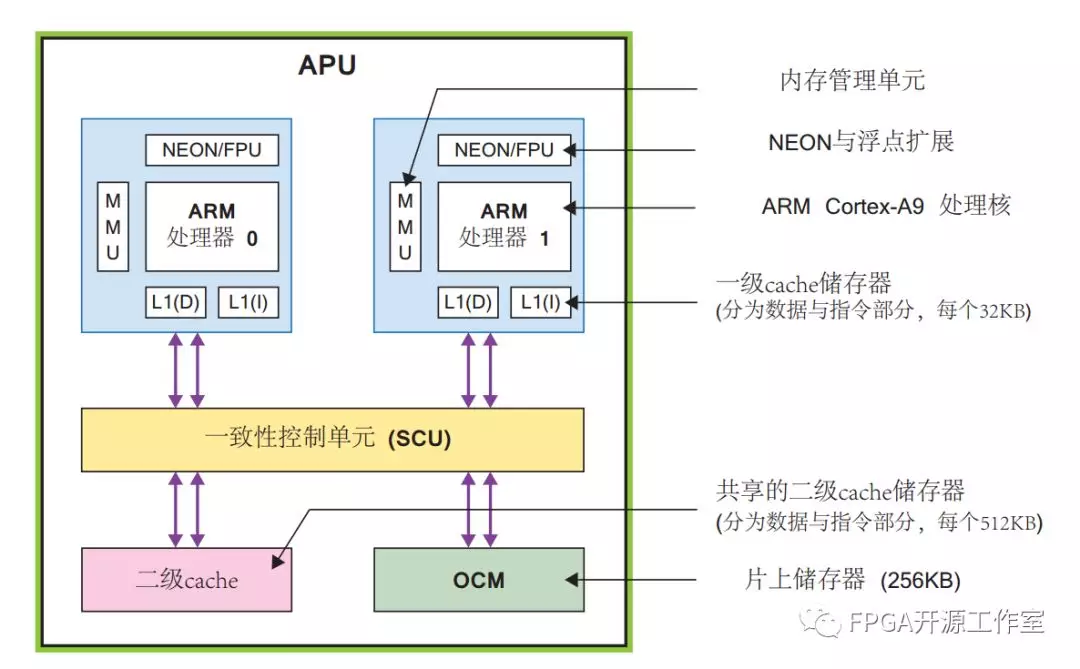

图6 应用处理器单元(APU)的框图

如图6所示,APU(应用处理器单元 ) 主要是由两个 ARM 处理核组成的,每个都关联了一些可计算的单元:一个 NEONTM 媒体处理引擎(Media Processing Engine,MPE)和浮点单元 (Floating Point Unit,FPU);一个内存管理单元(Memory Management Unit,MMU);和一个一级 cache 存储器(分为指令和数据两个部分)。APU 里还有一个二级 cache 存储器,再往下还有片上存储器 (On Chip Memory,OCM)。最后,由一个一致性控制单元(Snoop Control Unit,SCU)在 ARM 核和二级 cache 及 OCM 存储器之间形成了桥连接,这个单元还部分负责与 PL 对接,图中没有标出这个接口。

2.2 PL端

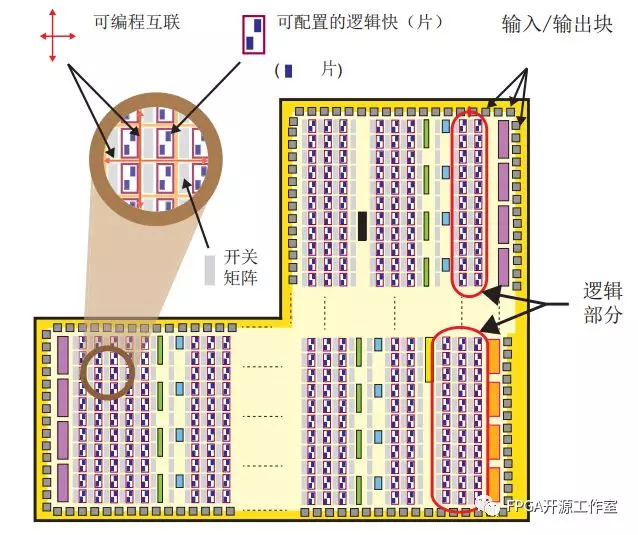

Zynq 架构的第二个主要部分是可编程逻辑。这是基于 Artix®-7和Kintex®-7的 FPGA 组件的 。图7 描绘了 Zynq 芯片的 PL 部分,其中几个功能被高亮了出来。PL 主要是由通用FPGA 逻辑部分组成的,这个FPGA 是由逻辑片和可配置逻辑块 (ConfigurableLogic Block,CLB)组成的,另外还有用于接口的输入 / 输出块(Input/ OutputBlock,IOB)(注意这些都是 Xilinx 专有的术语) 。

图7 逻辑部分及其组成单元

• 可配置逻辑块 (CLB) — CLB 是逻辑单元的小规模、普通编组,在 PL 中排列为一个二维阵列,通过可编程互联连接到其他类似的资源。每个 CLB 里包含两个逻辑片,并且紧邻一个开关矩阵。

• 片 (Slice) — CLB 里的一个子单元,里面有实现组合和时序逻辑电路的资源。Zynq 的片是由 4 个查找表、8 个触发器和其他一些逻辑所组成的。

• 查找表 (Lookup Table,LUT) — 一个灵活的资源,可以实现 (一)至多 6个输入的逻辑函数; (二)一小片只读存储器 (ROM); (三)一小片随机访问存储器 (RAM);或 (四)一个移位寄存器。LUT 可以按需组合起来形成更大的逻辑函数、存储器或移位寄存器。

• 触发器(Flip-flop,FF) — 一个实现 1 位寄存的时序电路,带有复位功能。FF 的一种用处是实现锁存。

• 开关矩阵 (Switch Matrix) — 每个 CLB 旁都有一个开关矩阵,实现灵活的布线功能来(一)连接 CLB 内的单元;或(二)把一个 CLB 与 PL 内的其他资源连接起来。

• 进位逻辑 (Carry Logic) — 算术电路需要在相邻的片之间传递信号,这就是通过进位逻辑来实现的。进位逻辑把布线和复用器组成链条来连接一个垂直列上的片。

• 输入 / 输出块 (Input/Output Blocks,IOB) — IOB 实现了 PL 逻辑资源之间的对接,并且提供物理设备 “ 焊盘 ” 来连接外部电路。每个 IOB 可以处理一位的输入或输出信号。IOB 通常位于芯片的周边。

3 设计流程

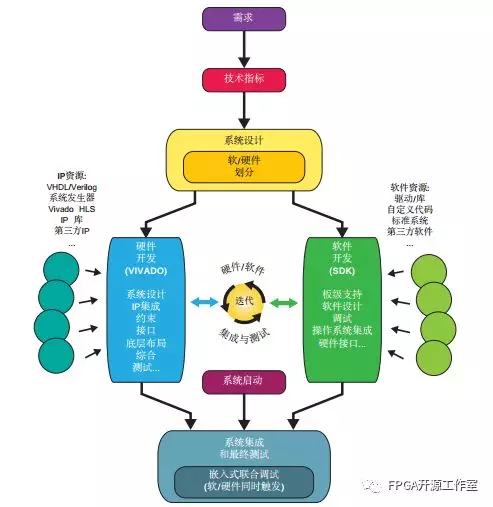

图8 Zynq-7000的基本设计流程框图

如图8所示,Xilinx Zynq-7000系列的基本设计流程从需求和技术指标开始,进入系统设计后首先进行软硬件划分,硬件部分通过vivado软件进行设计,包括Zynq-7000系统的搭建、综合、布局布线、约束生成bit文件等步骤。软件部分通过SDK来设计。最后嵌入式系统联合调试。

文章转载自:FPGA开源工作室