本篇主要介绍Xilinx FPGA PL侧的IO资源,目前主要包括HP、HR、HD三种类型,不同架构、不同封装的FPGA,包含的IO资源种类和数量均不一样,在连接外设时一定要注意,比如3.3V逻辑电平就不能直接连接到HP bank上,其VCCO的电源电压也不能直接接3.3V。

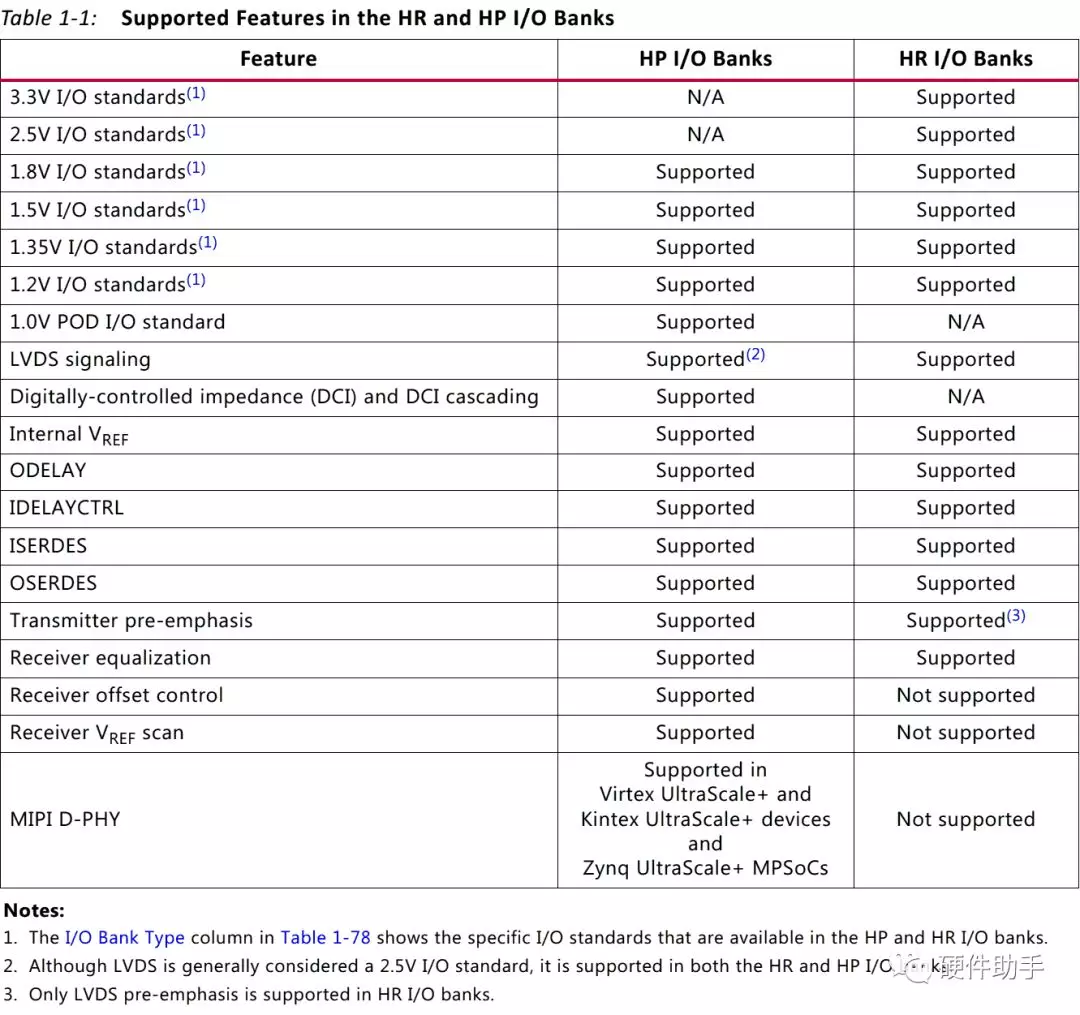

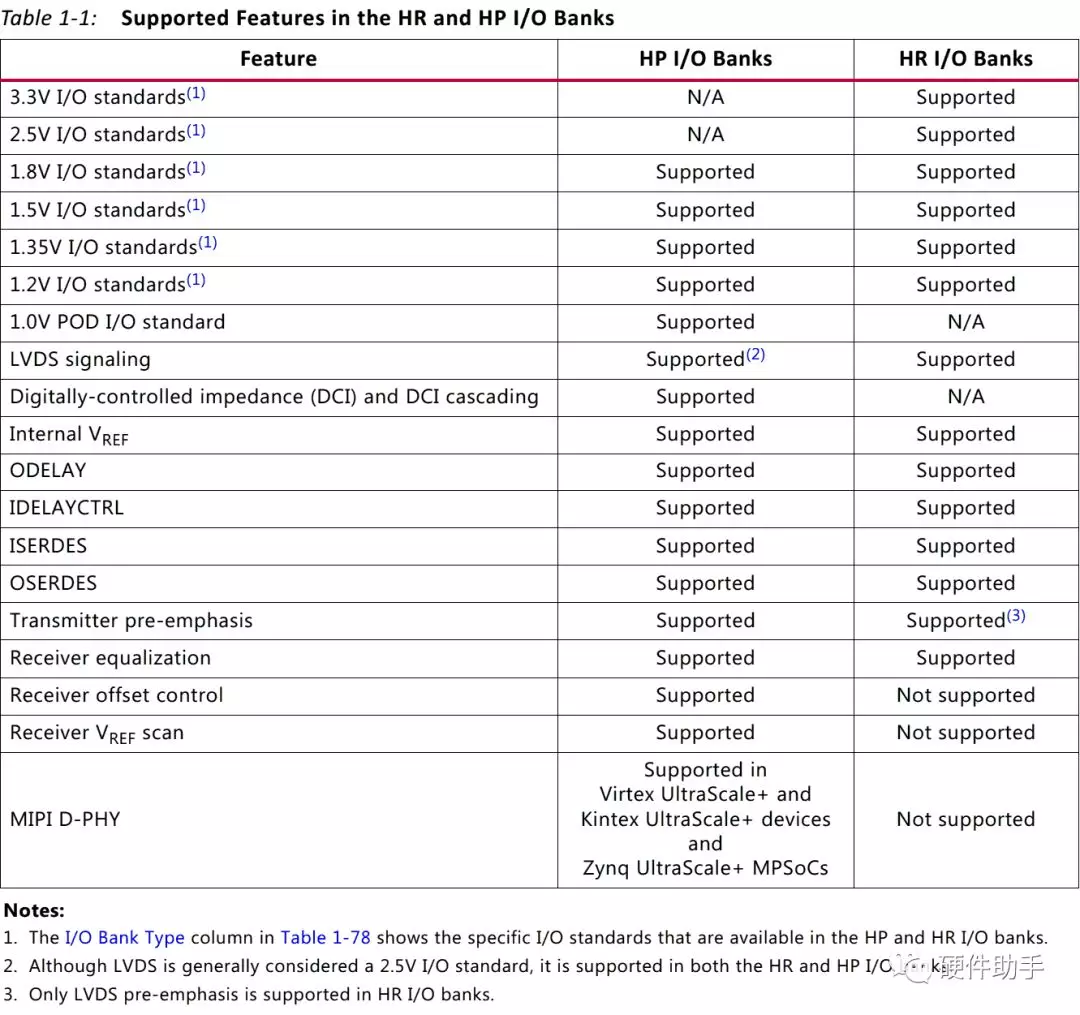

UltraScale architecture-based devices provide various I/O offerings: High-performance(HP), high-density (HD),and high-range (HR) I/Obanks.Generation Form Factor

The HR I/O banks are designed to support a wider range of I/O standards with voltages up to 3.3V.

The HP I/O banks are designed to meet the performance requirements of high-speed memory and other chip-to-chip interfaceswith voltages up to 1.8V.

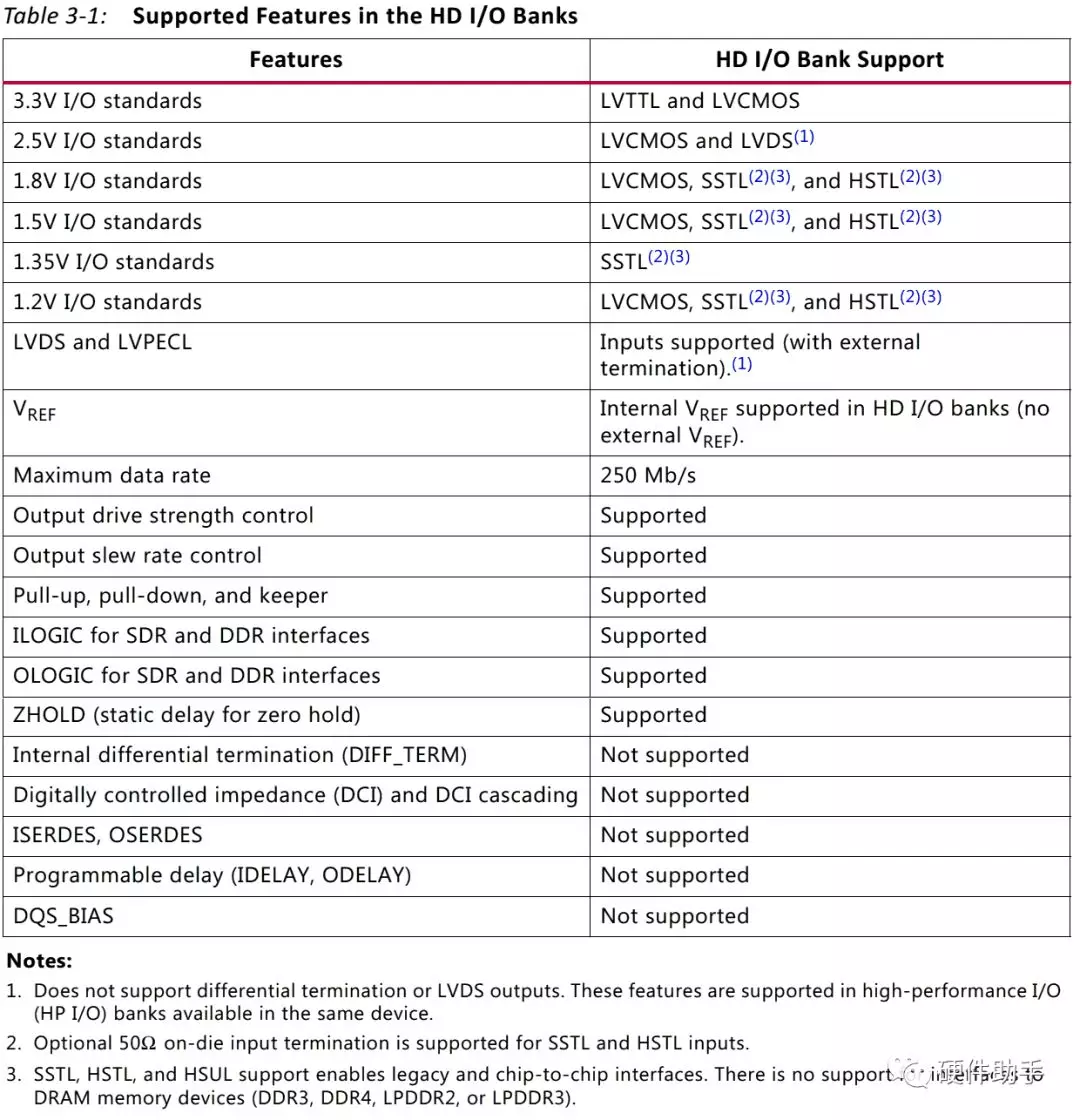

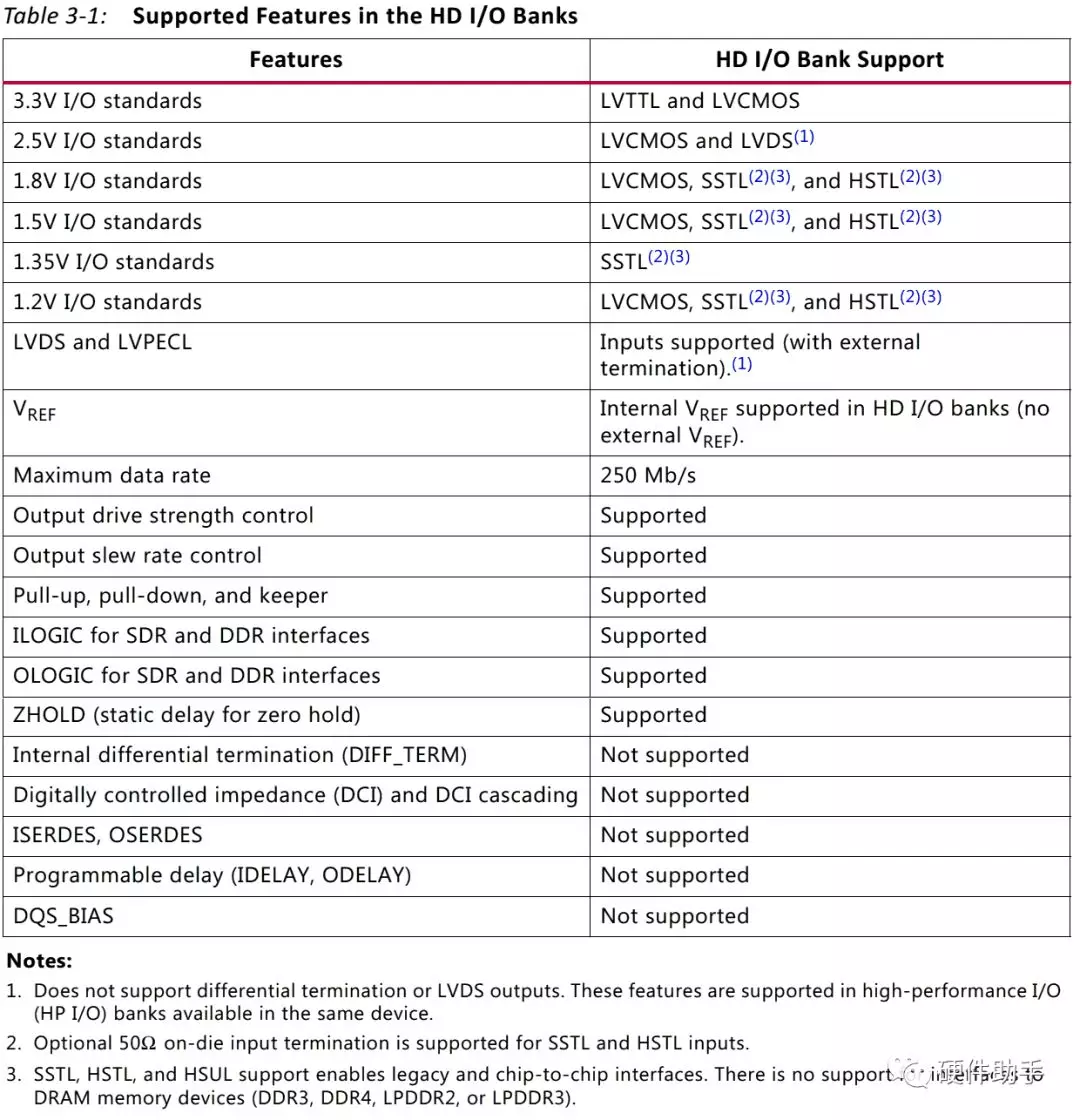

The HD I/O banks are designed to support low-speed interfaces.

The 7 series FPGAs offer both high-performance (HP) and high-range (HR) I/O banks.

Kintex UltraScale and Virtex UltraScale families have high-performance I/O banks (HP I/Os) and high-range I/O banks (HR I/Os) with corresponding logic resources.

The Virtex UltraScale+ family only has high-performance I/O banks (HP I/Os) with the corresponding logic resources. These I/O banks also have enhanced MIPI D-PHY support capabilities.

The Zynq UltraScale+ MPSoC and Kintex UltraScale+ FPGA families have high-performance I/O banks (HP I/Os) with enhanced MIPI D-PHY abilities and the corresponding logic resources. They also have high-density I/Os (HD I/Os) with corresponding logic resources.

1、HP/HR

UltraScale devices support many of the same features supported in 7 series devices. However, there are some useful new features, along with changes to severalexisting features. These new features and changes include:

Each I/O bank contains 52 SelectIO interface pins. In some devices, there are some HR I/O mini-bankscontaining 26 SelectIO pins, each with their own independent power supply andVREF pin.(HR bank支持只有26个IO的mini-bank)

Support forpseudo-open-drain logic standards (POD).(支持DDR4的POD逻辑,但只有HP bank支持)

Series outputtermination control is available in HP I/O banks for improved signal integrityand ease of board design.(HP bank有串联端接)

Internal VREF level scan(HP I/O banks only). One dedicated external VREF pin per bank.(每个HP bank有一个VREF)

Pre-emphasis isavailable for the DDR4 standard in HP I/O banks and the LVDS TX standard inHP/HR I/O banks. Pre-emphasis reduces inter-symbol interference and minimizesthe effects of transmission line losses.(HP bank的POD和HP/HR bank的LVDS TX有预加重功能)

Linear equalization onVREF-based receivers (in HP I/O banks) and differential receivers (in both HPand HR I/O banks) is available to overcome high-frequency losses through thetransmission channel.(有线性校准功能)

Receiver offset cancellation is available for some I/O standards to compensate for processvariations (HP I/O banks only).

Digitally controlled impedance (DCI) is only available in HP I/O banks. DCI uses only one reference resistor per bank, 240Ω to GND on the VRP pin. The values of the driver orinput termination are determined by the OUTPUT_IMPEDANCE and on-die termination(ODT) attributes, respectively.

VCCAUX_IO only supports a nominal voltage level of 1.8V.

A SLEW value of MEDIUM is supported in HP I/O banks.

The DCITERMDISABLE port can control both DCI and non-DCI on-die input termination features in HP I/Obanks.

Where applicable, asserting IBUFDISABLE causes the input to the interconnect logic to be a 0.This is different from the resulting 1 after asserting IBUFDISABLE in 7 series devices.

The bit slice is effectively a physical layer (PHY) block that replaces and enhances thefunctionality of the Component mode primitives. This PHY block gives tightercontrol over timing and provides new features enabling higher data rate reception in UltraScale devices.

MIPI D-PHY transmitter and receiver functions are supported in the HP I/Os specific to the VirtexUltraScale+ devices, Kintex UltraScale+ devices, and Zynq UltraScale+ MPSoCs.

2、HD

High-density (HD) I/O banks are SelectIO resources designed to support a wide range of I/O standards with voltages ranging from 1.2V to 3.3V. HD I/Os are optimized for single-ended, voltage-referenced, and pseudo-differential I/O standards operating at data rates of up to 250 Mb/s. Limited support for true differential inputs (with external termination) is also available to support LVDS and LVPECL clock inputs. HD I/Os also contain interface logic including registers and static delay lines to support asynchronous, system synchronous, and clock-based source synchronous interfaces.

Every HD I/O bank contains 24 I/O pins. When defined as single-ended standards, HD I/O pins support input, output, and bidirectional operating modes. Paired I/O pins can be used to support differential standard functionality. For pseudo-differential standards, like DIFF_SSTL15, input, output, and bidirectional support is available. True differential standards, like LVDS_25, can only function as an input buffer.

详细可参考不同系列的IO资源User Guide,具体如下:

UG471: 7 Series FPGAs SelectIO Resources User Guide

UG571: UltraScale Architecture SelectIO Resources User Guide

以及各个器件的Data Sheet。

文章转载自:硬件助手

评论

it's OK now.

加油,2016!