作者:OpenSLee

在《基于FPGA的多级CIC滤波器实现四倍抽取一》和《基于FPGA的多级CIC滤波器实现四倍抽取二》中我们先来了解滑动平均滤波器、微分器、积分器以及梳状滤波器原理以及它们的幅频响应。在三中我们将用verilog实现基于FPGA的多级CIC滤波器实现四倍抽取。

1 CIC滤波器的基本概述

CIC(积分梳状)滤波器是无线通信中的常用模块,一般用于数字下变频(DDC)和数字上变频(DUC)系统。CIC滤波器结构简单,只有加法器、积分器和寄存器,适合于工作在搞采样率条件下,而且CIC滤波器是一种基于零点相消的FIR滤波器,已经被证明是在高速抽取或插值系统中非常有效的单元。

2 matlab实现CIC滤波器的四倍抽取

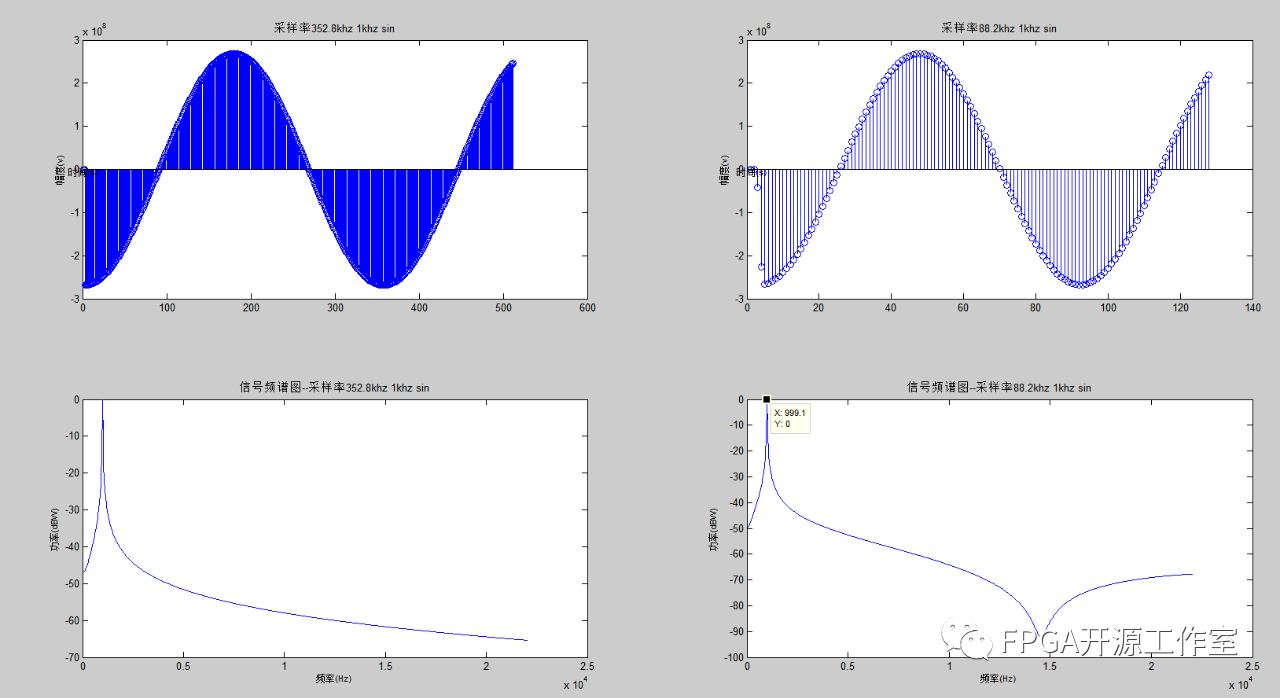

设计目标:将载波频率352.8khz的1khz sine降采样率到88.2khz。

close all

clear all

clc

%set system parameter

fs = 1000; %The frequency of the local oscillator signal

Fs = 352800; %sampling frequency

Fs1 = 88200;

N = 24; %Quantitative bits

L = 81920;

%Generating an input signal

t =0:1/Fs:(1/Fs)*(L-1); %Generating the time series of sampling frequencies

sc1 =sin(2*pi*fs*t); %a sinusoidal input signal that produces a random starting phase

sc2 =sin(2*pi*Fs*t); %a sinusoidal input signal that produces a random starting phase

sc = sc1 +sc2;

%滑动平均滤波器

b =[1,-1];%comb

a =[1,-1];%integerator

i1 =filter(1,a,sc);

i2 =filter(1,a,i1);

i3 =filter(1,a,i2);

y = downsample(i3,4);%decimate

c1=filter(b,1,y);

c2=filter(b,1,c1);

c3=filter(b,1,c2);

sf = c3./64;

f_osc =fft(sc,L);

f_osc=20*log(abs(f_osc))/log(10); %换算成dBW单位

ft1=[0:(Fs/L):Fs/16]; %转换横坐标以Hz为单位

f_osc=f_osc(1:length(ft1));

f_o =fft(sf,L);

f_o=20*log(abs(f_o))/log(10); %换算成dBW单位

ft2=[0:(Fs1/L):Fs1/4]; %转换横坐标以Hz为单位

f_o=f_o(1:length(ft2));

figure(1),

subplot(211),stem(t(1:512),sc(1:512));

xlabel('时间(t)','fontsize',8);

ylabel('幅度(dB)','fontsize',8);

title('sin_osc','fontsize',8);

subplot(212),stem(t(1:128),sf(1:128));

xlabel('时间(t)','fontsize',8);

ylabel('幅度(dB)','fontsize',8);

title('sf','fontsize',8);

figure(2),

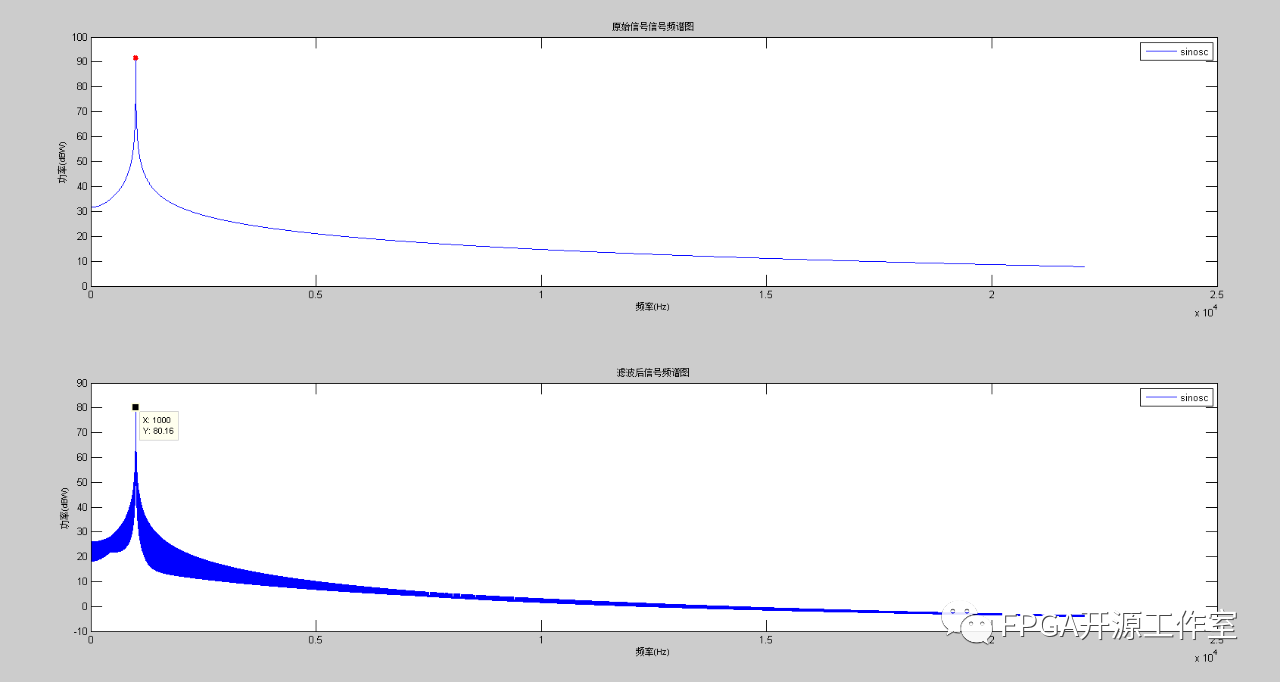

subplot(211),plot(ft1,f_osc);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('原始信号信号频谱图','fontsize',8);legend('sinosc');

subplot(212),plot(ft2,f_o);

xlabel('频率(Hz)','fontsize',8); ylabel('功率(dBW)','fontsize',8);

title('滤波后信号频谱图','fontsize',8);legend('sinosc');

3 FPGA实现CIC滤波器的四倍抽取

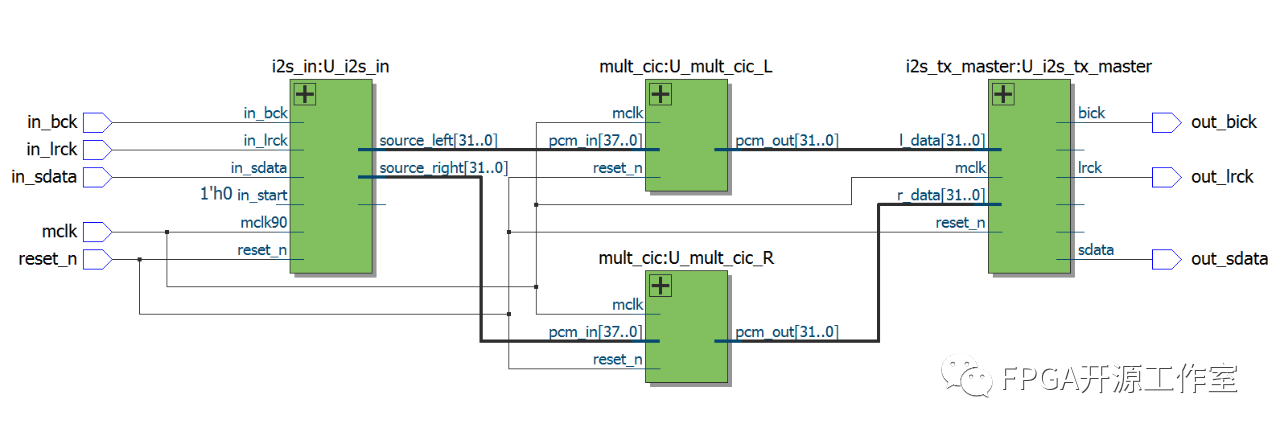

FPGA设计:FPGA由i2s输入352.8khz的1khz sine(当然也可以是歌曲352.8khz采样率),经过i2s串转并后经过mult_cic模块进行采样率下降处理(变成88.2khz 1khz sine或者歌曲),再通过i2s_tx_master并转串送到DAC 。

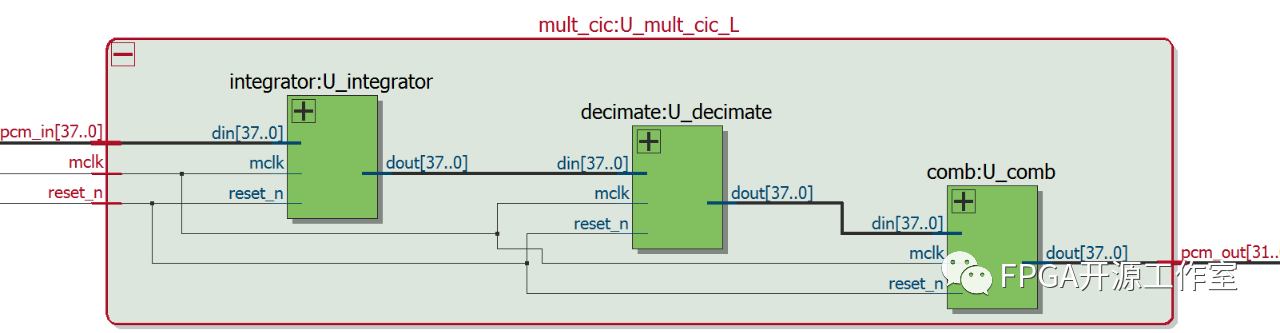

多级CIC滤波器的结构主要由积分器+抽值+梳状滤波器构成。

FPGA代码:

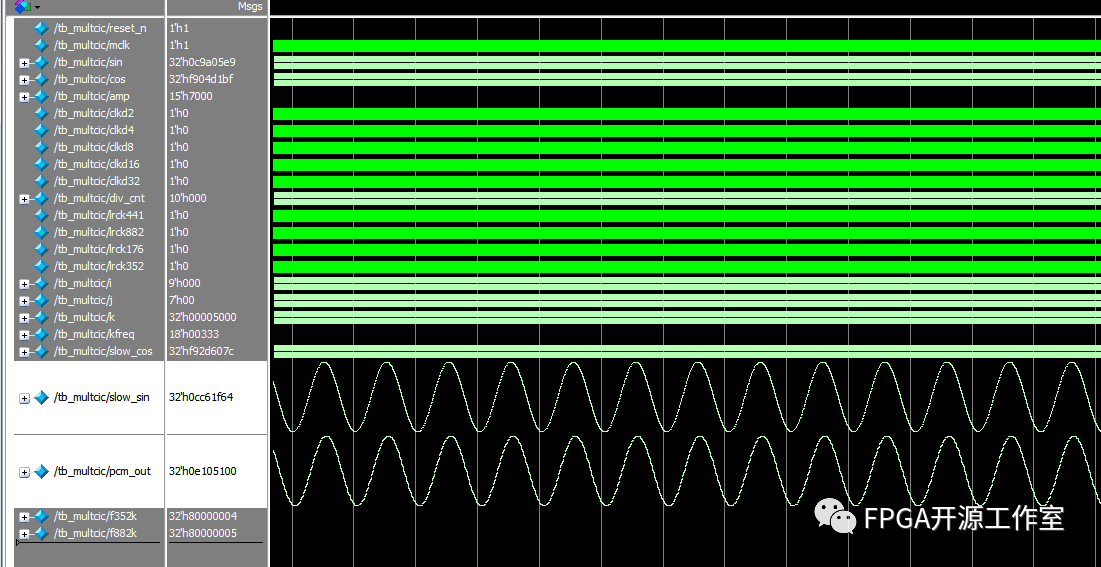

FPGA仿真:

仿真输入1khz sine输出依然为1khz sine,设计成功。

文章转载自: FPGA开源工作室(leezym0317)

*本文由作者授权转发,如需转载请联系作者本人