AXI协议是基于burst的,主机只给出突发传输的第一个字节的地址,从机必须计算突发传输后续的地址。突发传输不能跨4KB边界(防止突发跨越两个从机的边界,也限制了从机所需支持的地址自增数)。

1)突发长度

ARLEN[7:0]决定读传输的突发长度,AWLEN[7:0]决定写传输的突发长度。AXI3只支持1~16次的突发传输(Burst_length=AxLEN[3:0]+1),AXI4扩展突发长度支持INCR突发类型为1~256次传输,对于其他的传输类型依然保持1~16次突发传输(Burst_Length=AxLEN[7:0]+1)。

burst传输具有如下规则:

wraping burst ,burst长度必须是2,4,8,16

burst不能跨4KB边界

不支持提前终止burst传输

所有的组件都不能提前终止一次突发传输。然而,主机可以通过解断言所有的写的strobes来使非所有的写字节来减少写传输的数量。读burst中,主机可以忽略后续的读数据来减少读个数。也就是说,不管怎样,都必须完成所有的burst传输。

ARSIZE[2:0],读突发传输;

AWSIZE[2:0],写突发传输。

AxSIZE[2:0] bytes in transfer

'b000 1

'b001 2

'b010 4

'b011 8

'b100 16

'b101 32

'b110 64

'b111 128

突发类型

FIXED:突发传输过程中地址固定,用于FIFO访问

INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

WRAP:回环突发,和增量突发类似,但会在特定高地址的边界处回到低地址处。回环突发的长度只能是2,4,8,16次传输,传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。回环边界等于(AxSIZE*AxLEN)。

AxBURST[1:0] burst type

'b00 FIXED

'b01 INCR

'b10 WRAP

'b11 Reserved

Start_Address=AxADDR

Number_Bytes=2^AxSIZE

Burst_Length=AxLEN+1

Aligned_Addr=(INT(Start_Address/Number_Bytes))xNumber_Bytes。//INT表示向下取整。

对于INCR突发和WRAP突发但没有到达回环边界,地址由下述方程决定:

Address_N=Aligned_Address+(N-1)xNumber_Bytes

WRAP突发,突发边界:

Wrap_Boundary=(INT(Start_Address/(Number_Bytes x Burst_Length)))x(Number_Bytes x Burst_Length)

WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值,WVALID为高时,WSTRB为高的字节线必须指示有效的数据。

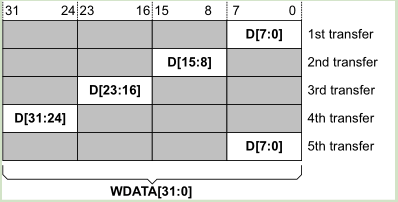

下图给出了5次突发传输,起始地址为0,每次传输为8bit,数据总线为32bit,突发类型为INCR。

下图给出3次突发,起始地址为4,每次传输32bit,数据总线为64bit。

读写响应结构

读传输的响应信息是附加在读数据通道上的,写传输的响应在写响应通道。

RRESP[1:0],读传输

BRESP[1:0],写传输

OKAY('b00):正常访问成功

EXOKAY('b01):Exclusive 访问成功

SLVERR('b10):从机错误。表明访问已经成功到了从机,但从机希望返回一个错误的情况给主机。

DECERR('b11):译码错误。一般由互联组件给出,表明没有对应的从机地址。

本文转自: 瓜大三哥(微信号:xiguazai_tortoise),作者:米果不回来,转载此文目的在于传递更多信息,版权归原作者所有。