作者:王欢,来源: FPGA技术联盟

本系列文章主要针对FPGA初学者编写,包括FPGA的模块书写、基础语法、状态机、RAM、UART、SPI、VGA、以及功能验证等。将每一个知识点作为一个章节进行讲解,旨在更快速的提升初学者在FPGA开发方面的能力,每一个章节中都有针对性的代码书写以及代码的讲解,可作为读者参考。

第一章:模块书写

Verilog HDL 语言的基本语法与 C语言相似,因此与 VHDL 相比较更容易上手。本章将会在实际小项目的基础上,以 Verilog HDL 语言为主, 教读者怎么更方便、更高效的学习 FPGA。

Verilog HDL 中的 HDL 指的是硬件描述语言(Hardware Description Language), 顾名思义,Verilog HDL 可以描述对应的硬件电路,下面以一个小例子说明。

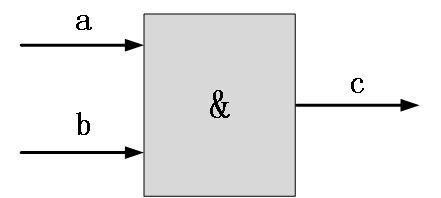

如图1所示为电路示意图, 首先分析一下该电路:

①两个输入端口即 a 和 b,为了更好地让读者理解该变量为一个输入端口,输入端口可加上方向pi(port input)表示输入。面对大量的代码,一个比较好的命名风格,更方便我们后续的验证, 希望前期就可以养成比较好的命名风格。

②一个输出端口即 c,同理 po 即为 port output。

功能:该电路实现 a 和 b 相与,结果为 c。

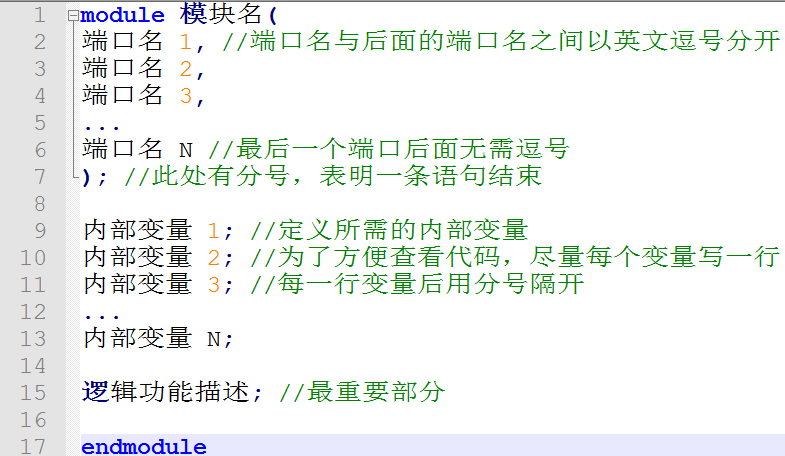

在用 Verilog HDL 描述一个电路时,必须要对该电路命名,此处我们对该电路命名为 a_and_b。在用 Verilog HDL 描述一个电路时, 模块的开始都是以 module 开始,endmodule 结束, module 后面写该模块的模块名,模块名的后面有一个小括号,所有该模块的端口都需要在此小括号内声明,小括号以分号结束(半角分号,同c 语言一样, Verilog HDL 中每一条语句也是以分号结束)。

在 module 与 endmodule 之间,可以定义必要的内部变量,以及我们所有描述的逻辑功能。具体如图2所示:

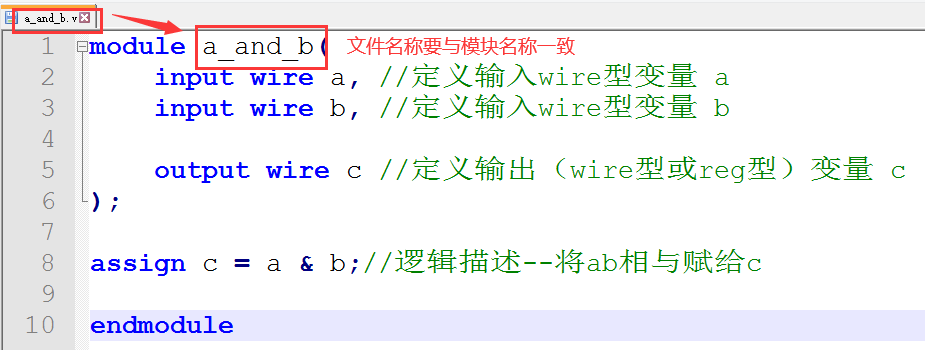

建议安装专门编辑程序的一些软件,例如Notepad++软件界面及功能都比较齐全。用 Notepad++打开我们新建的 V 文件, 按照模板书写模块a_and_b的 Verilog HDL 代码, 如下所示:

代码解析:

①模块以 module 作为开头, endmodule 作为结尾, 需要注意模块名与 V 文件名要一致;

②小括号内描述端口, Verilog HDL 中输入端口的关键字为 input,输出端口的关键字为 output。wire(线) 为端口的变量类型, input 端口的变量均为 wire型, Verilog HDL 中另一种常用的变量类型为 reg(寄存器),将在后面的章节详细介绍;

③代码第 8 行, 描述了具体的逻辑功能, assign 为 Verilog HDL 中的关键字,assign 可以描述组合逻辑,每一个 assign 后面只能跟一条语句。Verilog HDL 中另一个常用的关键字为 always, 后续会详细讲解。该语句表达的意思为 a&b赋值给 c, 其中=为赋值号, 将右边的结果赋值为左边的变量, &为按位与,即变量的对应位相与, 将在基础语法部分详细讲解。

这样我们就已经将图中电路描述清楚了,代码只需要按照给出的模板填写对应的内容即可。

第二章节我们将会讲解在ISE中如何验证代码是否有语法错误,以及将对应的代码转变成 RTL 电路。

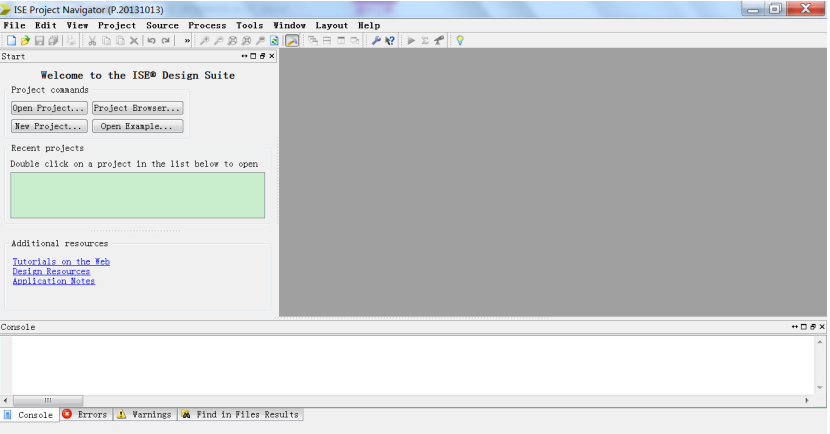

第二章:电路综合

第一章中已经将 a & b = c 对应的 Verilog HDL 程序写出, 但是我们无法得知我们所写的代码是否有语法错误,也不知道代码是否能够按照我们的意思生成对应的电路。本章中我们将会使用 xilinx 公司的 ISE 软件对所写的程序进行综合,从中可以得知代码是否有语法错误,以及生成对应的 RTL 电路。为了方便管理,我们在与 design 文件夹同路径下新建一个文件夹,取名为ise_prj(基于 ISE 的 project)。打开 ISE,会看到如图 1 所示的界面。点击右上角的 File,选择 New Project…新建一个工程。

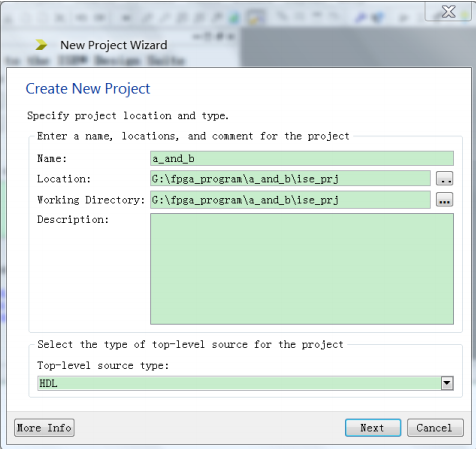

弹出如图 2 所示的界面,在 Name 处填写工程名字(尽量保证与顶层文件名一致即a_and_b), Location 处选择工程存放的路径, Working Direction 默认路径与 Location一致, Top-level source type 处按照所需选择,此处我们选择 HDL。

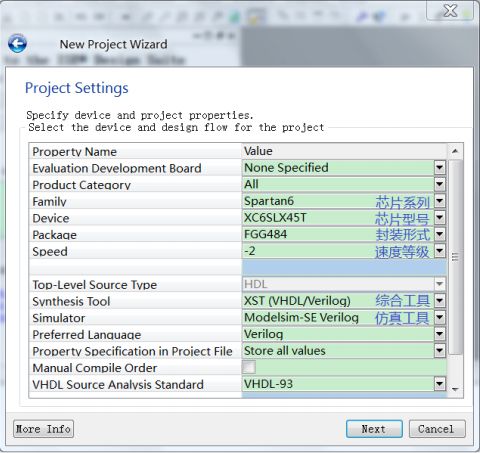

点击 Next,弹出如下图 3的界面,按照板卡芯片选择对应的选项,若是只想看看生成的 RTL 电路(不下板调试),则不需要选择,或者随便选择一个芯片即可。

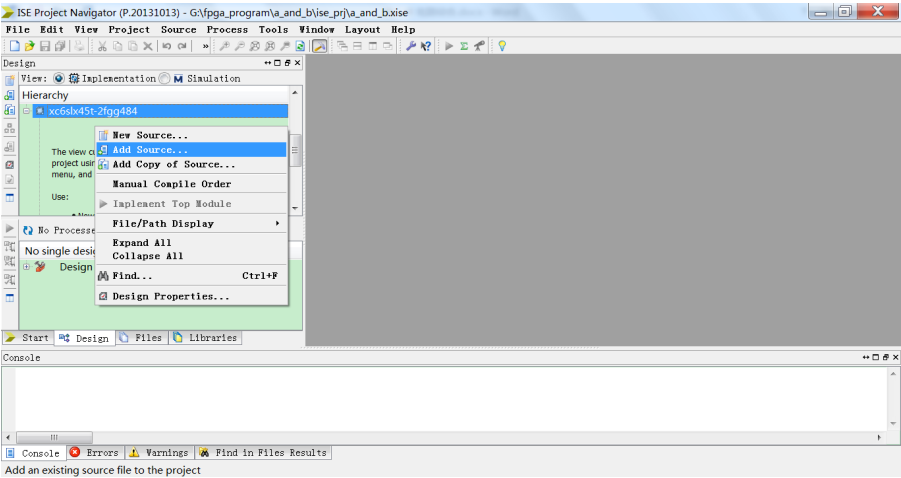

点击 Next,再点击 Finish 完成工程的创建。按照图4所示,右键点击芯片型号,选择 Add Source…添加已经存在的文件(a_and_b.v)。找到 design 文件夹中a_and_b.v 文件所在的路径,选中该文件,点击 OK。

添加文件后的工程界面如图 5 所示。

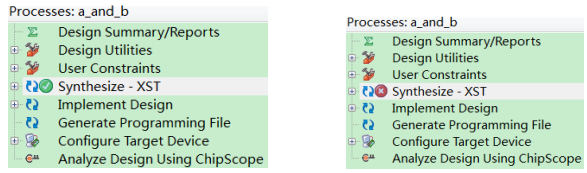

选中 a_and_b,双击 Synthesize 选项进行对我们的程序进行综合。若是没有语法错误则会出现图6左所示的界面,如果有语法错误则会出现图6右所示的界面,则需要查看错误报告将错误的地方改正并重新综合,直至编译通过为止。

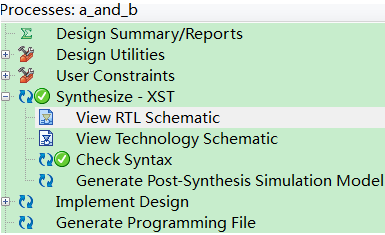

在综合正确的情况下,点击 Synthesize 选项前面的加号,如图 7 所示。

双击 View RTL Schematic 选项,出现如图8所示的界面。

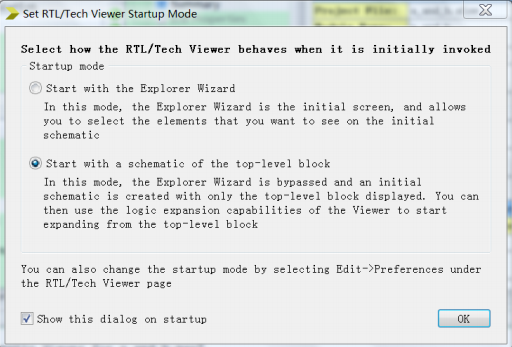

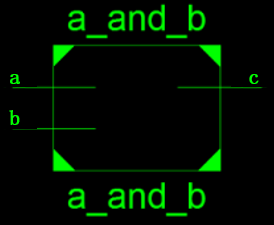

选择 Start with a schematic of the top-level block,点击 OK 选项,生成如下图 9 所示界面。

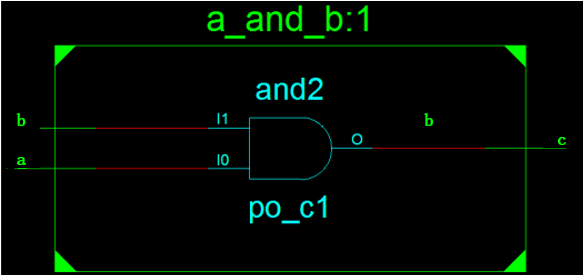

可以双击图 9 所示的模块的模型,则可以看到模块内部的 RTL 电路,如图 10 所示。

从图 10 中我们可以看到生成的电路是我们用 Verilog HDL 语言描述的电路结构。代码的语法及电路验证都是正确的,但是具体的功能是否满足我们的要求呢, 这就需要我们通过仿真来验证了。

在第三章中,我们会针对该代码书写对应的测试文件,并且通过 Modelsim 软件来验证我们的a_and_b 模块功能是否正确。

未完待续......