为处理海量数据、复杂算法、超低延时的应用提供数字化加速驱动力是赛灵思一直的目标。

为此,赛灵思研发 Bootgen 工具支持将二进制文件缝合在一起并生成器件启动镜像定义了多个属性和参数作为创建启动镜像时的输入。

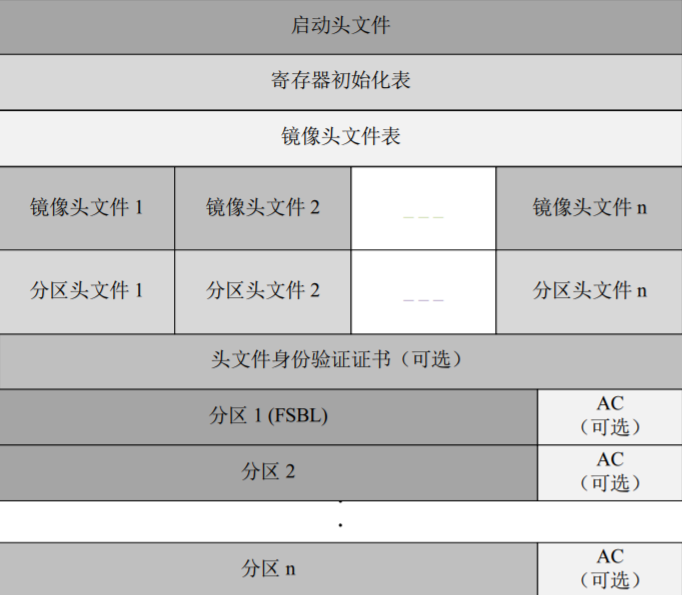

Zynq-7000 SoC 启动镜像布局

Zynq-7000 SoC 上的 bootROM 作为应用处理器单元 (APU) 中运行的首个软件,可在安全环境内以加密 FSBL 来执行。受支持的启动模式包括:

• JTAG 模式主要用于开发和调试

• NAND、并行 NOR、串行 NOR (QSPI) 和安全数字 (SD) 闪存用于启动器件。

可包含在 Zynq®-7000 SoC 启动镜像内的组件图示如下

启动头文件

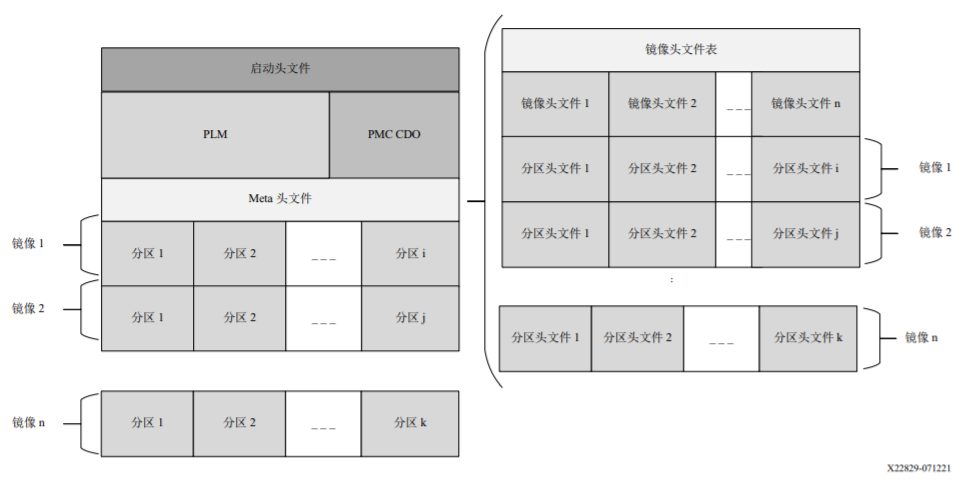

Versal ACAP 启动镜像格式

Versal ACAP 中的平台管理控制器 (PMC) 负责 Versal ACAP 的平台管理。由 2 个 PMC MicroBlaze 处理器、ROM 代码单元 (RCU) 和平台处理单元 (PPU) 所处理的启动镜像格式:

• RCU:ROM 代码单元包含三重冗余 MicroBlaze 处理器和只读存储器 (ROM),其中包含可执行 bootROM

• PPU:平台处理单元包含三重冗余 MicroBlaze 处理器和 384 KB 的专用 PPU RAM

Versal ACAP 启动镜像模块框图

创建启动镜像

Bootgen 定义了多个属性用于生成启动镜像,并根据文件中传递的内容来解释和生成启动镜像。由于有多条命令和多个属性可用,Bootgen 定义了启动镜像格式 (BIF) 来包含这些输入。BIF 包含:

• 配置属性,用于创建安全/非安全启动镜像

• 启动加载程序,适用于 Zynq® 器件和 Zynq® UltraScale+™ MPSoC 的第一阶段启动加载程序 (FSBL);适用于 Versal™ ACAP 的 Platform Loader and Manager (PLM)

• 一个或多个分区镜像

扫码获取完整用户指南了解 Bootgen 如何生成启动镜像