作者:Hope Peng,本文转载自: Ingdan FPGA微信公众号

1 、Xilinx器件SelectIO性能描述

FPGA是电子器件中的万能芯片,Xilinx FPGA处于行业龙头地位更是非常灵活。FPGA管脚兼容性强,能跟绝大部分电子元器件直接对接。

Xilinx SelectIO支持电平标准多,除MIPI C-PHY电平(三电平标准)外,IO能直接对接3.3V以及3.3V以下基本所有电平标准,初步统计支持72种不同电平标准。

Xilinx SelectIO速度快,比如16nm器件LVDS最高支持1600Mbps,MIPI D-PHY最高支持2500Mbps,DDR4 control POD12_DCI最高支持2666Mbps。

2、Xilinx器件Bank

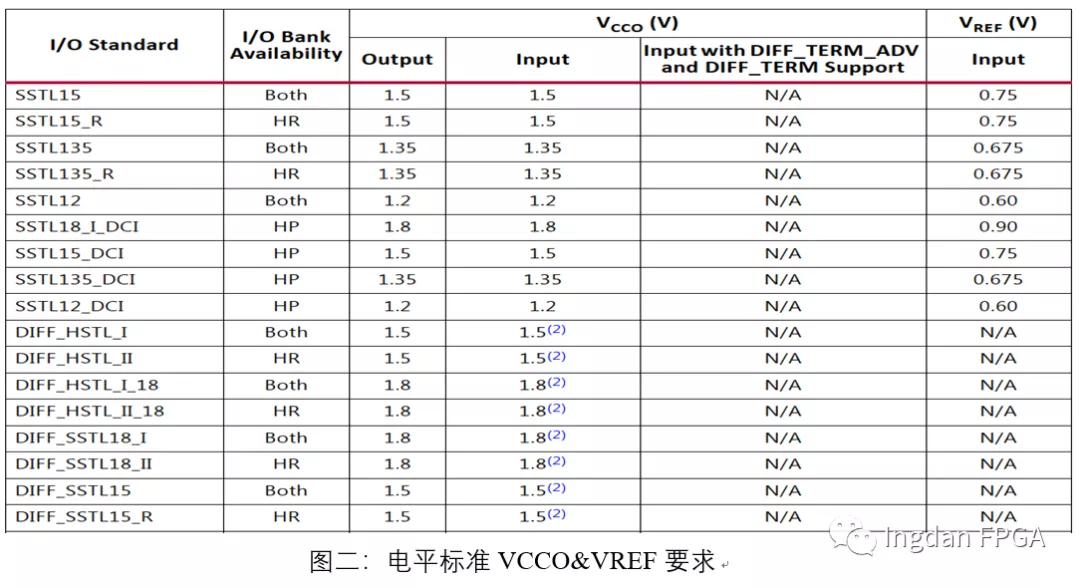

Ultrascale器件支持HR Bank & HP Bank,HR Bank最高支持3.3V电平,用于低速接口比如SPI,I2C等低速接口控制,HP Bank最高支持1.8V电平,用于LVDS,DDR4等高速接口。比如A1156封装包括2个HR Bank与8个HP Bank,一个Bank只能提供一种VCCO。硬件设计时把Bank VCCO电压相同的管脚可以放在同一个Bank,比如SSTL15 & DIFF_SSTL15电压要求相同Bank VCCO=1.5V,可以放在同一个Bank。参考图二:SSTL15电平HR&HP Bank都支持,要求Bank VCCO=1.5V,VREF=0.75V。

3、Xilinx器件Byte Group

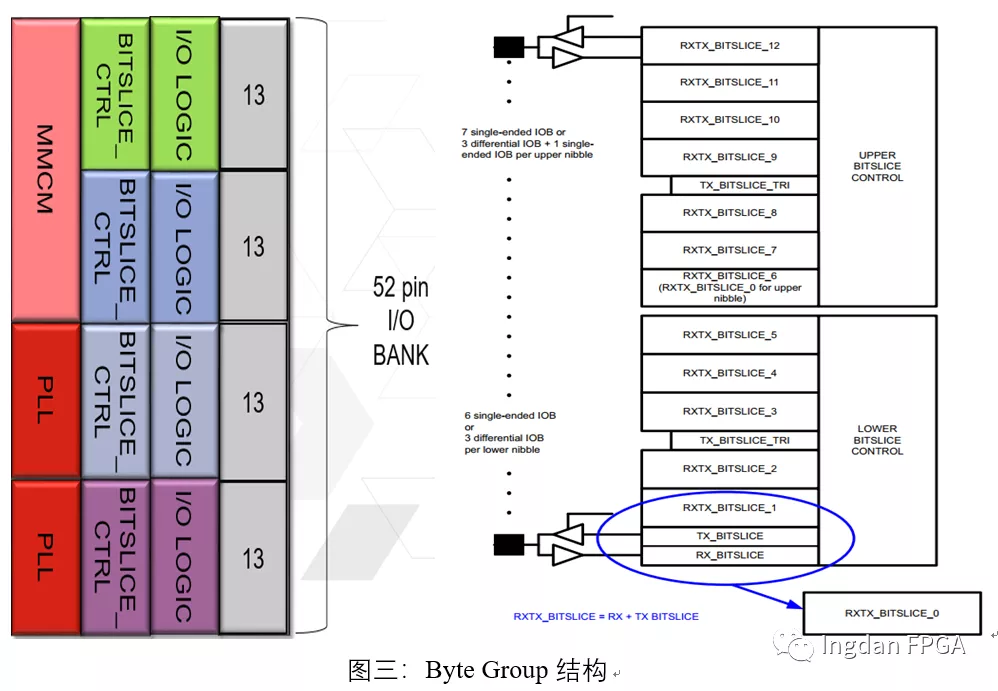

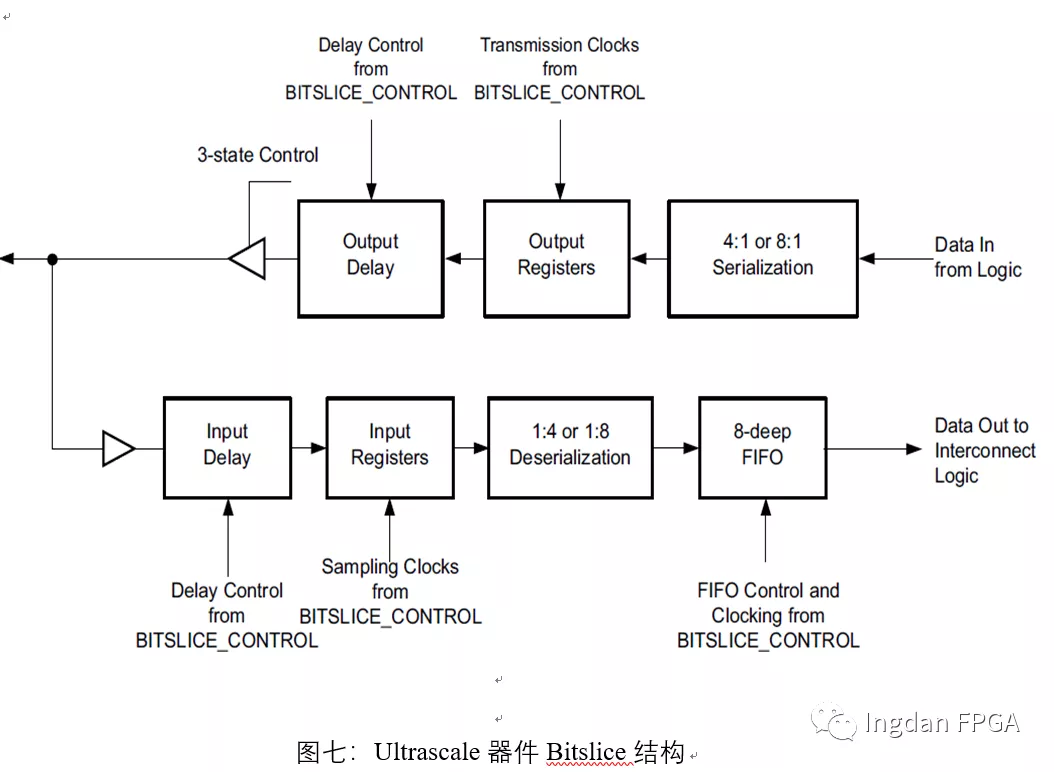

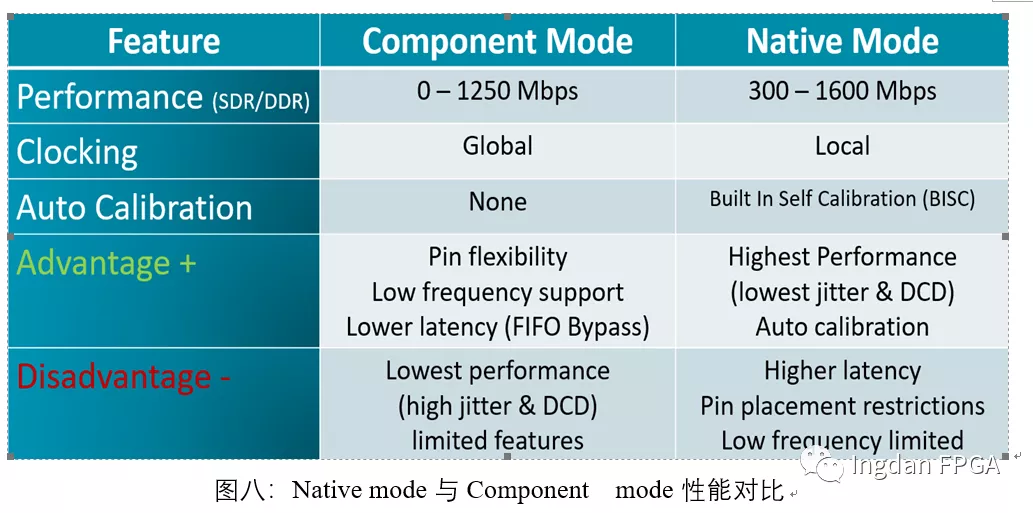

Ultrascale器件一个HP Bank包含4个Byte Group,每个Byte Group由13个管脚组成。Byte Group中除bitslice12外,其他12个管脚都可以作为单端或差分信号使用。Bitslice可以配置为Component primitives 或者Native PHYprimitives两种模式。

HP Bank包含一个MMCM与两个PLL,global clock (GC)时钟管脚可直接作为MMCM或者PLL 外部输入时钟。MMCM与PLL有专用的高速时钟布线资源控制本Bank的Bitslice,同时还能通过BUFG输出全局时钟驱动整个用户逻辑。Global clock (GC)时钟管脚只分布在中间两个ByteGroup,quad Byte clock (QBC)也是只分布在中间两个Byte Group。Global clock(GC)是全局时钟输入管脚作为PLL&MMCM输入时钟源,QBC是Byte Group的采样时钟。global clock (GC)作用域为整个芯片,QBC作用域为本Bank。Dedicated Byteclock (DBC)分布在最上与最下两个ByteGroup,用于采样本Byte Group数据,作用域为本Byte Group。

4、 Xilinx 器件SelectIO结构

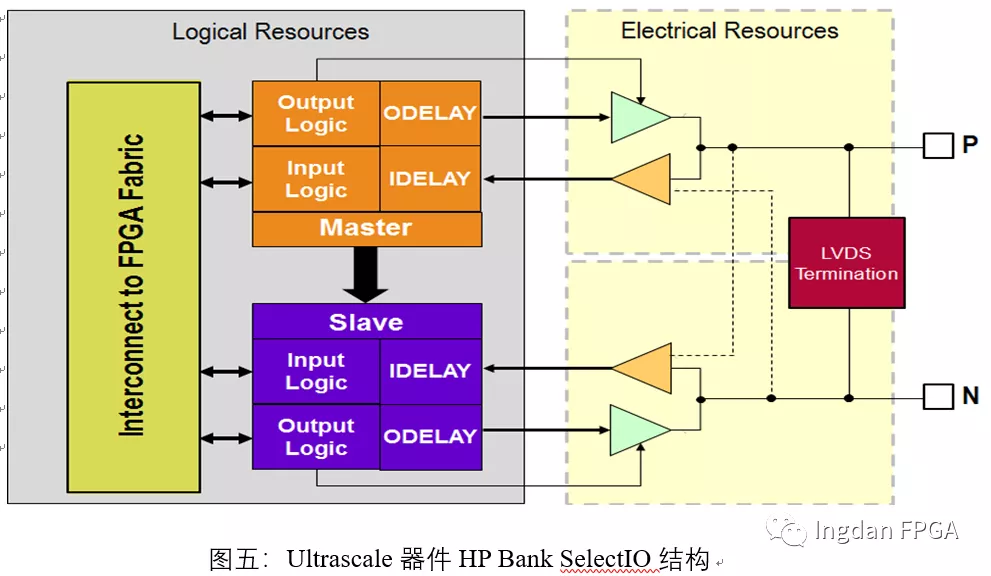

FPGA管脚支持电平标准多,速度跨度大,那是因为Xilinx有灵活巧妙的器件结构设计。不同系统器件SelectIO性能不同,同一款芯片HP Bank与HR Bank性能同样不同,原因都是因为不同类型Bank SelectIO结构复杂度不同。下面20nm Ultrascale器件SelectIO举例说明。

Ultrascale器件一个HP Bank 52个UserIO,其中4组每组12个管脚共48个管脚支持差分电平,管脚命名IO_LxxP支持差分电平正电平,管脚命名IO_LxxN支持差分电平负电平。

如果Bank VCCO=1.8V或者VCCO=2.5V,Bank支持LVDS电平,LVDS termination100欧姆终端电阻有效,LVDS接收端外部硬件电路不需要另外增加100欧姆终端电阻。

关于LVDS电平对接问题可以参考下面链接 https://www.xilinx.com/support/answers/43989.html 。

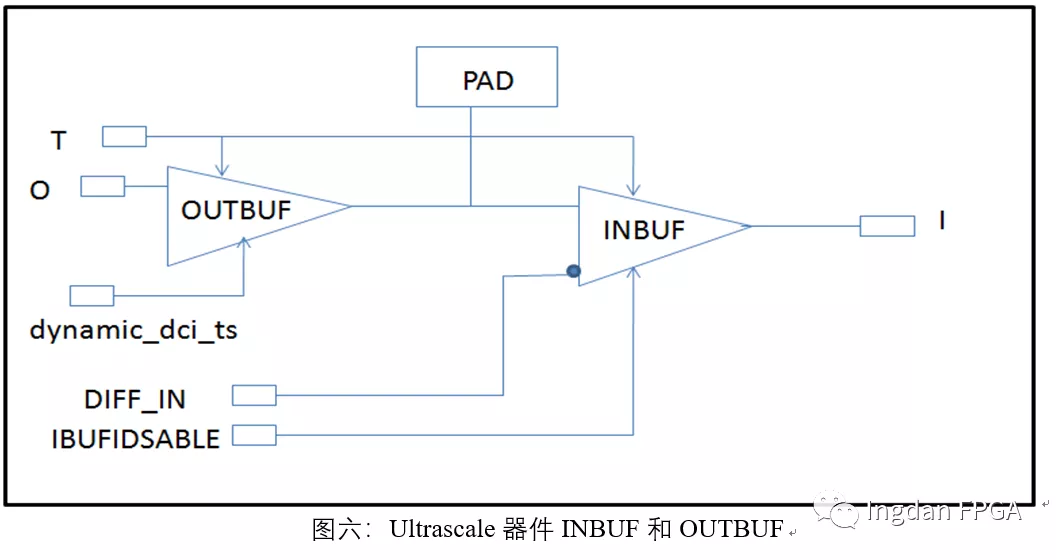

Ultrascale器件UserIO以IO_xx前缀命名,表示所有UserIO支持输入或者输出或者双向管脚,通过控制T状态PAD实现Input或者Output功能。Vivado工具默认配置会对input 管脚添加INBUF,output管脚添加OUTBUF。

硬件电路设计时候很难做到时钟与多路数据(比如一个时钟采样8位数据位宽)严格意义等长,在1Gbps速率情况,要求八根数据线PCB走线ps级别等长难度非常大,SelectIO内部有Input Delay Component ,精度能到2.5ps一个tap,最多支持512个tap。Component mode通过Input Delay补偿PCB走线不完成等长实现接口高速传输,Ultrascale器件LVDS Component mode能达到1250 Mbps速率。每个管脚都有Input Delay器件,要求时钟数据在同一个Bank,8位数据可以分别做不同Input Delay延迟,时钟能正确采样到正确的数据。

中间传输过程时钟频率不能过高,过高容易产生时钟抖动(Clock Jitter)和时钟偏斜(Clock Skew),最好不要超过500Mhz。比如数据频率为1200Mbps,时钟频率为150MHz,LVDS接收时把1200Mhz数据通过1:8 deserialization 降低到150M Hz时钟域。Ultrascale器件deserialization系数只支持1:2 & 1:4 & 1:8,如果需要支持1:7 deserialization系数,中间需要经过一个变速箱gearbox,请参考xapp1315。

Native mode是基于Component mode还使用后级一个8-deep深度FIFO,通过FIFO延迟不同补偿各个数据位走线延迟,Native Mode LVDS最高能支持1600M bps。时钟数据管脚必须在同一个Byte Group才能实现Native Mode,比如DDR4 DQS DQ, MIPI D-PHY 时钟数据必须在同一个Byte Group。

5、参考资料来源于UG571以及Xilinx专家Antony Gu的培训。

如果您在SelectIO方面有问题,欢迎联系:

simonyang@comtech.com.cn

charlesxu@comtech.com.cn