BittWare的Loopback例子演示了几件事。

功能性

Loopback的功能不是这个例子的主要重点。我们的重点是演示上面列出的所有项目。然而,环回功能是有价值的。当连接到第三方设备如网卡和交换机时,BittWare用它来验证DAC电缆的设置。

Loopback包含一个L2过滤器,选择要处理的帧。如果这些帧包含IPv4数据包,环回将在MAC和IP层交换源地址和目标地址。Loopback可以响应ARP数据包。增加这个功能是为了消除对第三方设备的专门配置要求。

Loopback在一个QSFP笼子上运行,将数据包从输入端循环到输出端。任何额外的QSFP笼子都不使用。

硬件设施

该环回是在一块含有Xilinx VU9P芯片的BittWare XUP-P3R板上设计和测试的,速度等级为2。该Loopback不使用任何外部存储器,应该可以移植到任何含有CMAC的BittWare Xilinx UltraScale+芯片上。

FPGA位流概述

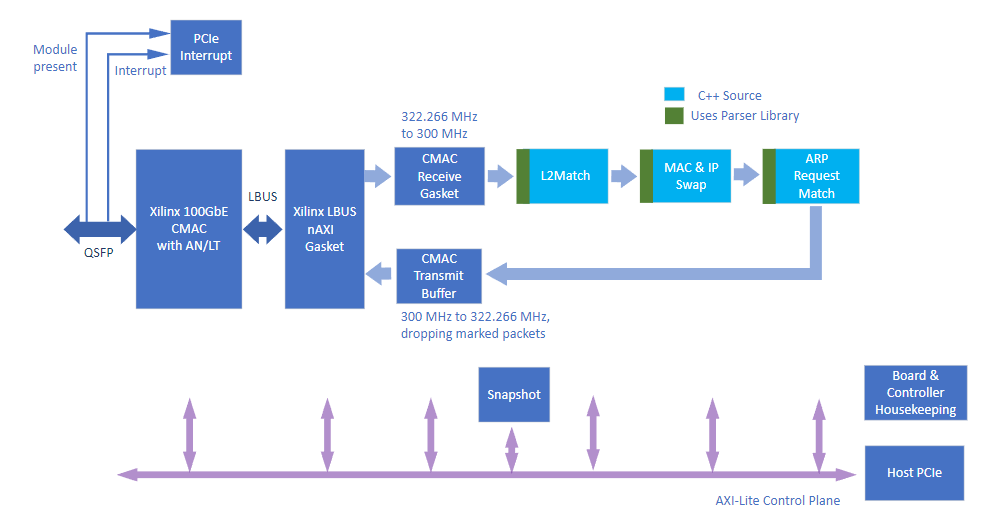

Loopback的FPGA位流包含几个组件。每个组件的输入和输出都有一个AXI4-Stream接口,共同作为数据平面使用。位流的控制平面使用AXI4-Lite接口连接到物理PCIe接口。

设计流程

Loopback是作为Xilinx IP Integrator项目提供的。其中几个组件是用Verilog编写的。有三个是使用Xilinx HLS流程编写的,该流程可以发出Verilog。

从IP Integrator的角度来看,目前的实现将用HLS编写的三个组件归为一个组件。然而,这三个组件在这里是分开记录的。事实上,它们被记录为四个不同的组件。这是因为HLS组件共享一个共同的 "解析器库",为了避免重复,我们将其分开记录。

重置和统计

从哲学上讲,在复位时,所有的组件都被初始化,但处于一种 "伤害最小 "的模式。然后,软件必须在环回系统开始成功运行之前配置这些组件。

每个组件还公开了统计寄存器,以协助用户调试硬件或软件。我们包括一个快照信号,以便所有的统计寄存器的值在时间上是同步的。

AXI接口

位流的接口宽度和时钟速度被选择来承载百兆以太网流量。数据面的AXI4-流接口是512比特宽。除了与CMAC接触的地方,该接口的时钟为300MHz。帧元数据在一个单独的总线上传输,即AXI TUSER位,当AXI TLAST为高时,有效数据。

元数据在整个比特流中是不一致的。因此,与每个组件相关的文档描述了该组件在输入时期望的元数据和在输出时转发的元数据。

注意:在这个Loopback的实现中,元数据跟随帧数据。这与NetFPGA.org学术团队的设计决定相反。他们为构建路由器进行了优化,在那里提前知道每个帧的目的地是有帮助的。相反,Loopback是围绕比特流大小和延迟进行优化的。拖动元数据需要在每个组件内进行更少的缓冲。

位流控制接口是AXI4-Lite从机,32位宽。所有的读和写都是32位的。在字节顺序重要的情况下,Loopback希望我们的控制寄存器能以网络或大-endian字节顺序持有数据。

我们将组件控制平面寄存器记录在一个地方,与组件本身的描述分开。交叉引用是为了帮助用户在这两个地方之间进行导航。用于Loopback控制寄存器的内存图在很大程度上受到Xilinx HLS工具链中AXI4-Lite接口实现要求的影响。

所使用的AXI的正式定义来自于赛灵思的 "AXI参考指南",可在此查阅:https://www.xilinx.com/support/documentation/ip_documentation/ug761_axi_... 。

控制平面软件概述

BittWare环回实例在插入主机的PCIe卡上运行。BittWare为该主机提供软件以控制该实例的功能。该控制软件使用在主机上运行的Python 3。

该实例的软件建立在BittWare的BittWorks II工具包之上。更确切地说,它为BwHIL和BmcLib库添加了Python绑定。然后,它在一组Python组件中利用这些绑定,这些组件是为了操作实例的位流在PCIe地址空间中暴露的寄存器。

此外,Loopback实例的比特流将一些硬件事件翻译成PCIe中断。为了支持这一点,Loopback的软件将这些中断翻译成Python调用。

用一个非常基本的与回环实例位流的交互来说明。

$# 首先使用工具包的命令行或使用GUI来映射PCIe卡

$ bwconfig --add=usb# 首先通过USB映射为设备0

$ bwconfig --add=pci# 同样的卡通过PCIe映射为设备1

$ python3# 调用python3

>>> from components.hildev import *

>>>card =Card(1)

>>> card.show_stats() # 显示所有组件的所有统计信息

>># 只显示第一个CMAC组件的统计信息,有一些选项

>>> card.cmac[0].show_stats(showall=False,doTick=False)

>>> help()

>>> exit()

所有的Python组件都支持一个共同的底层方法集合。请注意,我们的Python实现没有硬编码的PCIe内存图。相反,Python读取一个JSON数据库,该数据库定义了可用的FPGA位流组件,它们的寄存器,以及寄存器在PCIe地址空间的位置。这个JSON数据库是由Loopback Example的文档自动生成的。

完整的Python API文档可以在BittWare的开发者网站上找到。

低级别的方法包括。

可用的更高层次的方法取决于具体的组件。然而,有几种方法是比较常见的。