本文转载自:芯设计微信公众号

写在前沿

玄铁E902是一款面向低功耗端侧MCU,IOT应用的cpu,支持RISC-V RV32EMC ISA,开源版本openE902的配置缺少指令cache以及TEE功能。

本文基于平头哥半导体公司开源的openE902 core、以及smart soc代码,做了FPGA的软件测试。

准备工作

1: 下载openE902的core,smart soc,以及仿真文件:

https://github.com/T-head-Semi/opene902

按照README.md可以先跑一下仿真环境。

2: CDK工具包(剑池CDK集成开发环境V2.12.1):

https://occ.t-head.cn/community/download?id=5759974197753282563

3: E902软件库SDK(SmartL_E902M_RV32EMC-R2S0P0-V1.7.3):

https://occ.t-head.cn/community/download?id=582560116612956160

4: vivado(2017.01), FPGA(Xilinx Artix-7 XC7A200T), Putty, CLINK调试工具。

5: E902的产品手册, PPA数据:

https://img.102.alibaba.com/1623743224121/7a98153360599adc281c32f258a3c9...

硬件SOC部分工作

smart soc的架构如下图1所示(E906 core替换为openE902):

图1

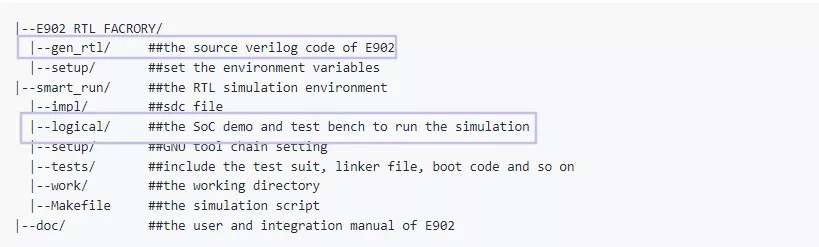

openE902的文件目录结构如图2:

图2

将图2中的cpu core、及smart soc代码添加到新建的vivado工程中。

添加工程约束xdc:对时钟复位,jtag接口,gpio[7:0] 和uart信号进行约束, 时钟约束选择了20Mhz。

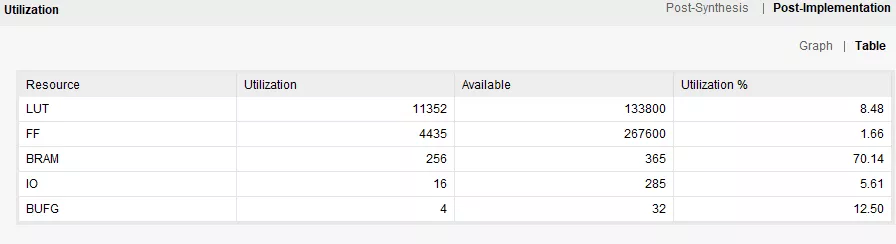

布局布线后的资源情况(其中ITCM, DTCM, SYS_SRAM,约1MB存储),如图3:

图3

生成bit 文件烧录到FPGA板子上。

软件SDK部分工作

在xxx\SmartL_E902M_RV32EMC-R2S0P0-V1.7.3\projects\examples\driver目录中有对uart、timer、gpio的CDK工程。

打开CDK工程: compile,build project,start debugger。

这里我重写了C代码,可以调用timer、gpio、uart、以及算术运算函数,如图4:

图4

第一次代码测试的时候,程序挂了,经过单步debug发现程序在trap_c.c文件中不断循环。

这里我把图5框中部分代码注释掉就没问题了(system.c代码),不知道会不会影响其他功能。

图5

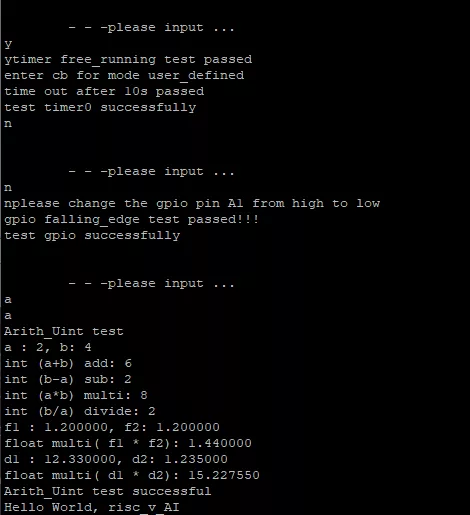

main函数的FPGA测试没问题,串口测试效果如图6所示:

图6

写在最后

基于openE902、smart soc,以及配套的SDK工程,芯片设计同学可以在底层硬件做一些数字IP RTL逻辑开发,软件同学也可以在上层软件做一些应用开发。

免责声明:本文转载于网络,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。