MIPI DSI 是一种基于数据包的高速接口,用于将视频数据传送到 LCD/OLED 显示器。在某种程度上,它类似于 DisplayPort,具有更节能(因此更复杂)的物理层。DSI 主要用于移动设备(智能手机和平板电脑)。

我开始这个项目是作为构建低成本高清投影仪的基础。后来我意识到它对于 VR 应用程序和作为小型 uC 的通用显卡也很有用 - 这就是它采用 Arduino 盾格式的原因。

具有 MIPI DSI 接口的 LCD/OLED 屏幕控制器。Arduino 扩展板格式、HDMI 转 DSI 适配器和内置帧缓冲器。

特征

支持 3/4 通道 MIPI DSI 显示器。

DSI 控制器在 60 Hz刷新率下支持高达 1080x1920 的分辨率。

将 HDMI 视频转换为 DSI - 让您将任何 MIPI DSI 屏幕连接到您的 PC、Raspi 或类似设备。转换最高可达 720p@60 Hz 或 1080p@48 Hz。

具有简单图形堆栈的内置帧缓冲区,允许通过 8 位并行或 SPI 总线连接小型微控制器,例如 Arduino

低于 50 美元的 BOM,包括 4 层 PCB(@100 件)。

通过迷你 USB 连接器供电。

嵌入式32 位 CPU,可供用户应用。

项目历史

12/2013:完成原理图和 PCB。

12/2013:固件的初始版本,适用于 FPGA 开发套件上的Iphone4/4s 屏幕。

02/2014: 拿到了 PCB和组件。

02/2014: 组装测试 PCB,驱动 3 通道和 4 通道屏幕。

07/2014:开始进行 HDMI <> DSI 转换。

08/2014:适用于 640x960 Iphone4 屏幕的 HDMI 转换。

08/2014: DSI 核心实现 1080p @ 60 Hz(使用 HDMI 转换为 48 Hz)。

08/2014:修订版 1.1。PCB 设计、原理图和固件发布。

06/2015:Prototypingr 修订版 2.0。

Arduino 界面/绘图命令(视需求而定)。

使用大于 1080p 的显示器测试外部 HDMI 解码器。

Port Doom 在软核 CPU 上运行。

硬件

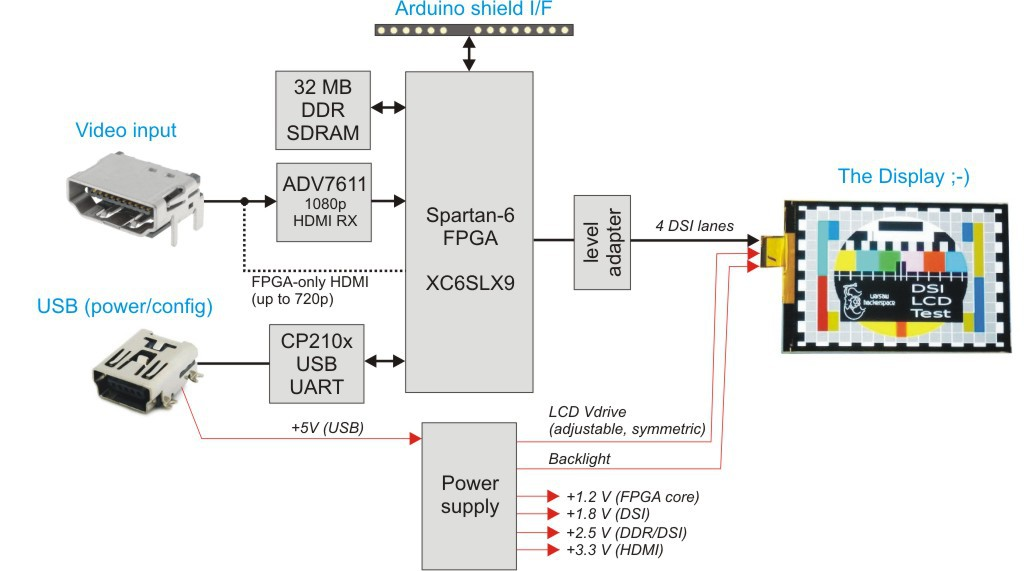

下图显示了设计的主要模块:

FPGA:赛灵思 Spartan-6-SLX9。亮点:业余友好型 TQFP144 封装和内置 SerDes,额定速率高达 1080 Mbits/s。FPGA 几乎完成了这个项目中的所有工作,托管 MIPI DSI 内核、带 DDR 存储器的帧缓冲控制器、HDMI/DVI 解码器。一切都由嵌入式 Lattice Mico32 CPU 管理。

DSI 电平适配器:一堆电阻,将 FPGA 的 1.8 V SSTL/LVCMOS I/O 连接到 DSI 电平。FPGA 部分中的更多信息。

DSI 连接器:标准 2x15pin 2mm 间距母连接器,带有所有 DSI 信号、电源和一些用于与显示器接口的 GPIO 引脚。由于显示器之间的连接器引脚排列不同,因此这里的想法是使用一个微型适配器板来承载特定 LCD 的连接器及其接线。

DDR SDRAM,为帧缓冲区提供内存,因为大多数智能手机 DSI 显示器都没有。

HDMI 输入:慢速版,使用 FPGA 的 ISERDES 模块(高达 1080p @ 48 Hz)或快速版(1080p @ 60 Hz),基于 ADI 公司的 ADV7611 芯片。外部HDMI解码器与SDRAM芯片和主机接口共用一些引脚,因此全高清-60赫兹版本只能作为HDMI转DSI适配器工作。

主机接口:12 个引脚连接到 Arduino 扩展板的 IOH/IOL 接头。确切的功能尚未定义,我正在考虑 4 线 SPI 接口和 8 位并行总线。

USB UART CP2102 芯片,为 FPGA 提供 USB UART、软件引导加载程序和 JTAG 功能。

主电源:集成PMIC(TI/National LM26480)。电压为:+3.3 V(HDMI 输入、USB、主机 I/F)、+2.5 V(SDRAM 和 FPGA Vccaux)、+1.8 V (DSI)、+1.2 V(FPGA 内核)。

LCD 偏置/背光电源:大多数显示器需要一些更高的正/负电压才能运行。该板有一个用于此目的的简单 DC/DC 转换器,可产生高达 +/- 6 V 的对称电压。可以通过在 DSI 连接器引脚之一和地之间连接一个电阻器来调整特定面板的电压。还有一个单独的背光 LED 电流驱动器,可由另一个电阻器编程。两个 DC/DC 转换器均使用 TPS61041 芯片。

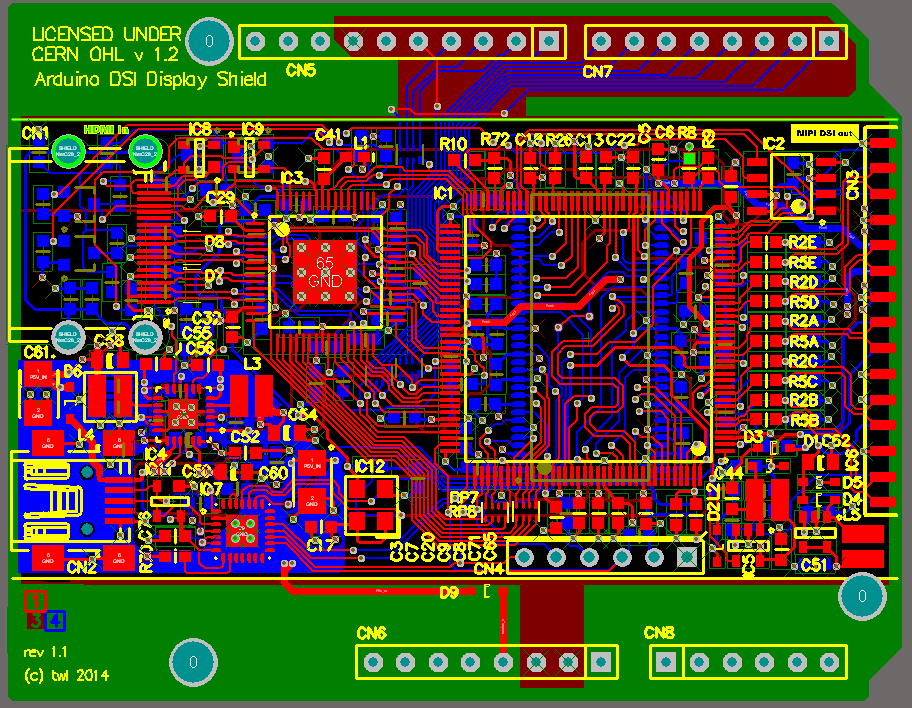

印刷电路板设计

DSI 屏蔽由两个 PCB 组成 - 主板,所有很酷的东西都在主板上,还有一个小型适配器板,通常每个显示器都不同,通过 30 针 2 毫米针头连接。

主板是典型的 Arduino 扩展板。我在 4 层上对设计进行了布线,信号在 2 个外层、一个连续的接地层和一个分离的电源层上。DDR 位于 FPGA 正下方以简化布线。SSTL 到 DSI 电平转换器电阻器紧邻 FPGA 输出引脚放置以避免存根。所有差分对都是针对 Z0=100 欧姆计算的。

适配器板只是将 DSI 通道、电源和背光信号路由到显示器的连接器。完全没有管理 DSI LCD 面板连接器和电源的标准,因此对于每种显示器类型,您都需要一个单独的适配器板。它们很简单(2 层,一个连接器 + 几个用于设置偏置电压/背光 LED 电流的电阻器)。下面的屏幕截图显示了 Iphone 4/4S Retina 显示适配器的布局:

FPGA

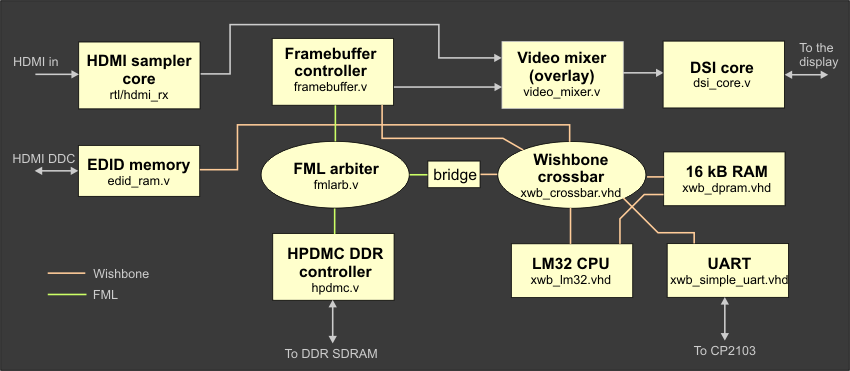

该项目的核心和灵魂:Xilinx Spartan-6 - 每个引脚上带有千兆位 SerDes 块的低成本 FPGA,这使得仅使用一堆外部电阻器就可以对 HDMI/DVI 信号进行采样或生成 DSI 数据流。FPGA 的肠子如下所示。目前,它只是对 Verilog/VHDL 代码中的内容进行了非常简短的描述。

CPU 和外围设备

CPU 负责显示器的初始化和控制帧缓冲区。它还可以做一些简单的绘图操作(虽然不会太快)。

我选择了莱迪思 Mico32 软处理器,因为设计的成熟度和其他成功的 OSHW 项目使用它(例如 Milkymist)。CPU 通过 Wishbone 互连控制以下外围设备:

- 一个小的 16 kB RAM 块,包含软件。前 2 kB 为引导加载程序保留,其余 14 kB 是实际应用程序。

- UART(用于调试和加载软件)。

- DDR 内存(通过 Wishbone 到 FML 桥的缓慢访问)。

- Framebuffer 和 DSI 核心(设置视频模式时序)。

- EDID RAM,伪装成 2402 I2C EEPROM。告诉 HDMI 信号源我们显示器的时序要求。

DDR 内存和帧缓冲

内存子系统使用 Milkymist 的高性能动态内存控制器(感谢 Sebastien!),连接到 32 MByte DDR RAM(16 位,100 MHz)。RAM 当前仅用于存储显示的图像,CPU 无法从中执行代码。帧缓冲器核心只是将帧数据从 DDR RAM 泵送到视频覆盖引擎,在那里它与 HDMI 视频合成。

HDMI采样器

赛灵思应用笔记 XAPP495 中的 HDMI/DVI 解码器。输入HDMI,输出并行RGB像素、时钟和同步信号。在这里几乎用作黑匣子。

视频叠加

顾名思义,它将来自 HDMI 的图像和帧缓冲区(使用简单的颜色键控)放在一起,并输出显示器的最终像素流。包括 3 个不同时钟域(HDMI 时钟、CPU 系统时钟和 DSI 内核时钟)之间的一些弹性缓冲和帧对齐逻辑。

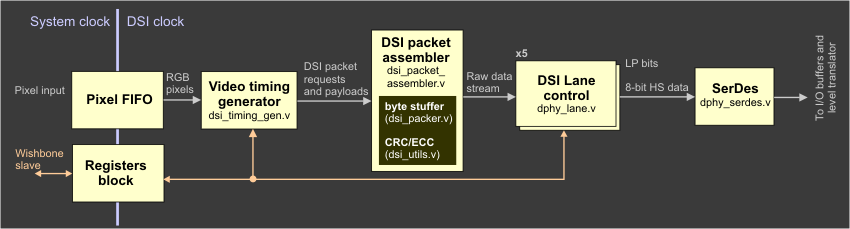

DSI核心

DSI内核的架构如下图所示:

像素流水线由 5 个阶段组成:

- 第一阶段是一个大的 4096 条目 FIFO。它的作用是将 RGB 像素数据从系统时钟域移动到 DSI 字节时钟域(= 数据速率除以 8)。多亏了这一点,我们不需要让系统与像素时钟同步运行——像素可以稍微快一点/慢一点。

- 定时发生器产生一系列 DSI 高速 (HS) 数据包标头和有效载荷,指示水平/垂直同步脉冲、消隐期或将 RGB 数据传递到显示器。显示分辨率和消隐时间由 CPU 通过 Wishbone 接口编程。

- 数据包组装器接收数据包请求,将它们填充到 3 或 4 个并行字节上,添加带有 ECC/CRC 校验和的数据包头和尾。

- 通道控制模块(4 个用于数据通道,1 个用于时钟通道)控制低功耗 (LP) 和高速 (HS) 模式之间的转换,并生成 LP 模式信号以初始化和启用显示器。在车道控制模块的输出端,我们获得 LP+/LP- 信号和 SerDes 的 8 位并行数据流。时钟通道数据输出简单地固定为 0xaa,从而在 SerDes 的输出端产生一个 DDR 时钟。

- SerDes 块 - 使用 Spartan-6 的 OSERDES2 块将并行 8 位数据转换为高速串行位。由于每个 FPGA 引脚上的 IODELAY 可编程延迟线,还可以确保数据和时钟通道之间的正确时序。

如果您对此项目有任何想法、意见或问题,请在下方留言。

本文转载自:电路城

免责声明:本文转载于网络,转载此文目的在于传播相关技术知识,版权归原作者所有,如涉及侵权,请联系小编删除(联系邮箱:service@eetrend.com )。