作者: James Shen,文章来源: Comtech FPGA

需求背景分析:

1、Xilinx Programmable Soc产品在可编程系统集成、提升系统性能、减少 BOM成本,降低产品整体功耗等方面具有多重优势;

2、Xilinx Programmable Soc内嵌的AES-256加解密引擎和HMAC认证引擎,保护知识产权,防止拷贝、抄板;

3、近几年来,Xilinx Programmable Soc产品在各个领域的应用越来越广,大规模量产SOC的产品越来越多;

4、一种高效的批量烧录AES keys和 RSA Keys 到EFUSE和BBRAM中的方法非常重要。

解决办法:

1、采用Xilinx提供的烧录器HW-USB-II-G,但Xilinx的烧录器只能支持一对一的烧录,无法支持一对多;

2、使用Xilinx指定的第三方烧录器。

https://china.xilinx.com/products/technology/configuration-solutions.html

3、使用本文基于SD卡方式来批量烧写。

硬件和软件平台要求:

1、支持ZYNQ7000和 MPSOC 等SOC器件,本案例使用XC7Z020-2CLG400I;

2、启动方式必须支持SD卡启动;

3、Vivado工具为2022.1,如果需要前面版本那么最好是2020版本及以后版本。

实验实现要求和流程:

1、创建生成硬件平台流程;

a、创建工程,选择型号,加载内核,配置外围电路;

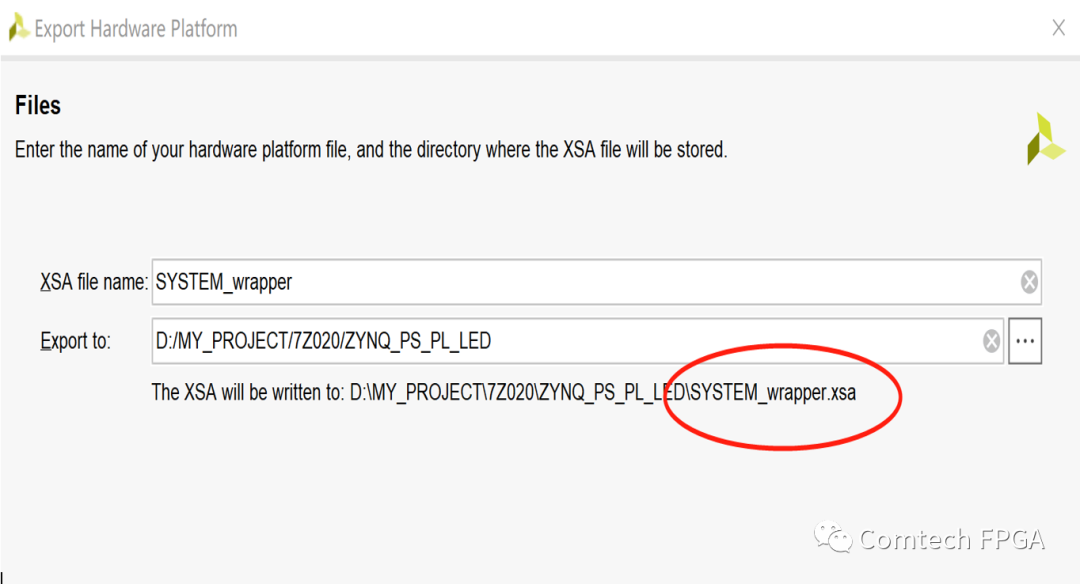

b、生成SYSTEM_wrapper.xsa文件(早期Vivado版本生成的是SYSTEM_wrapper.hdf)。

2、创建软件平台和设置:

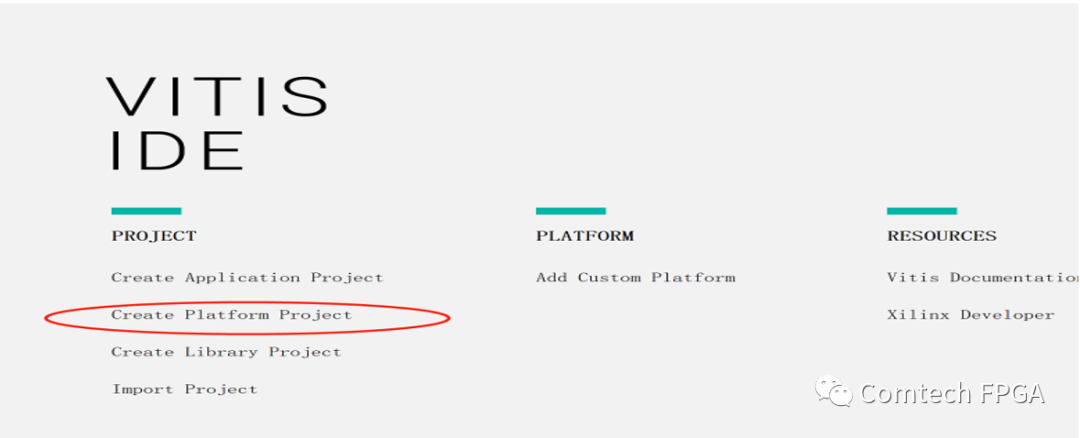

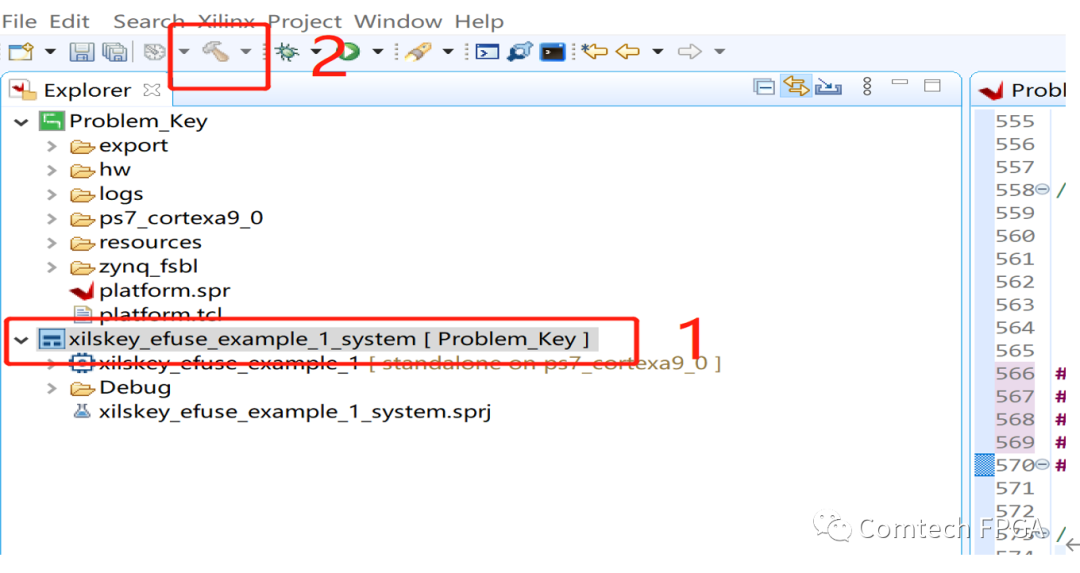

a、Lunch Vitis / Lunch SDK ,创建新的平台项目:

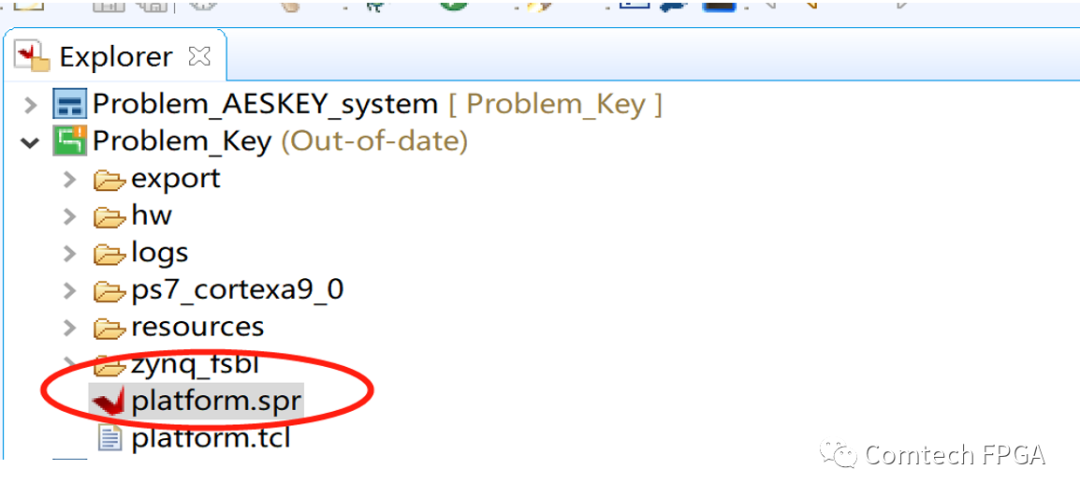

b、创建好平台项目后,找到platform.spr文件:

c、双击platform.spr文件,找到Modify BSP Settings :

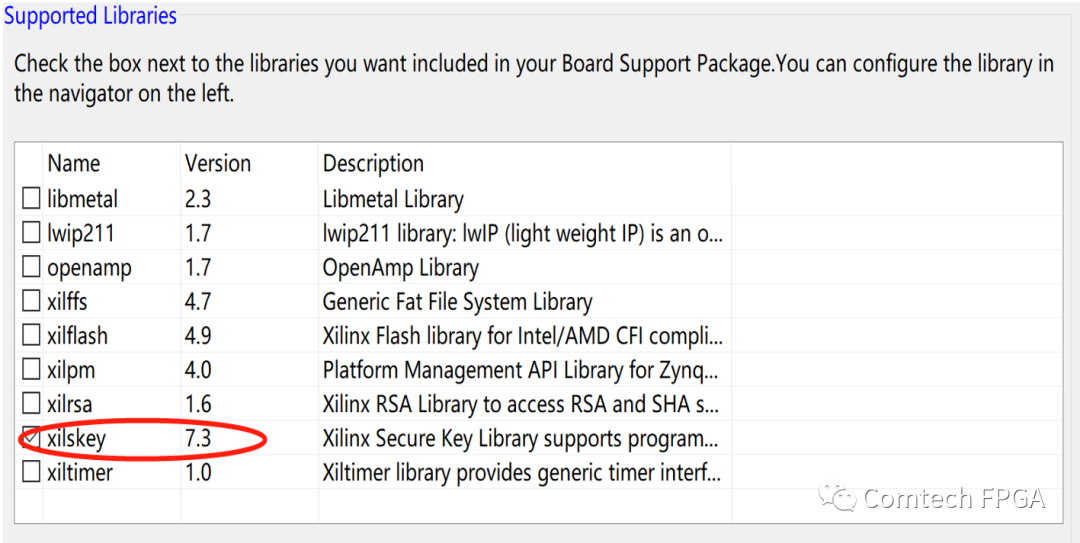

d、选择Xilskey 7.3:

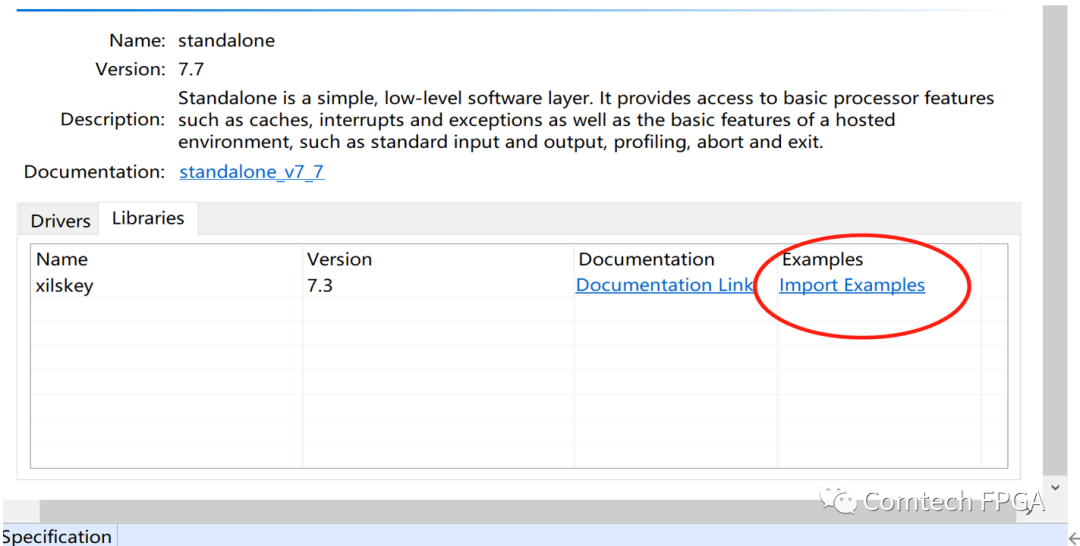

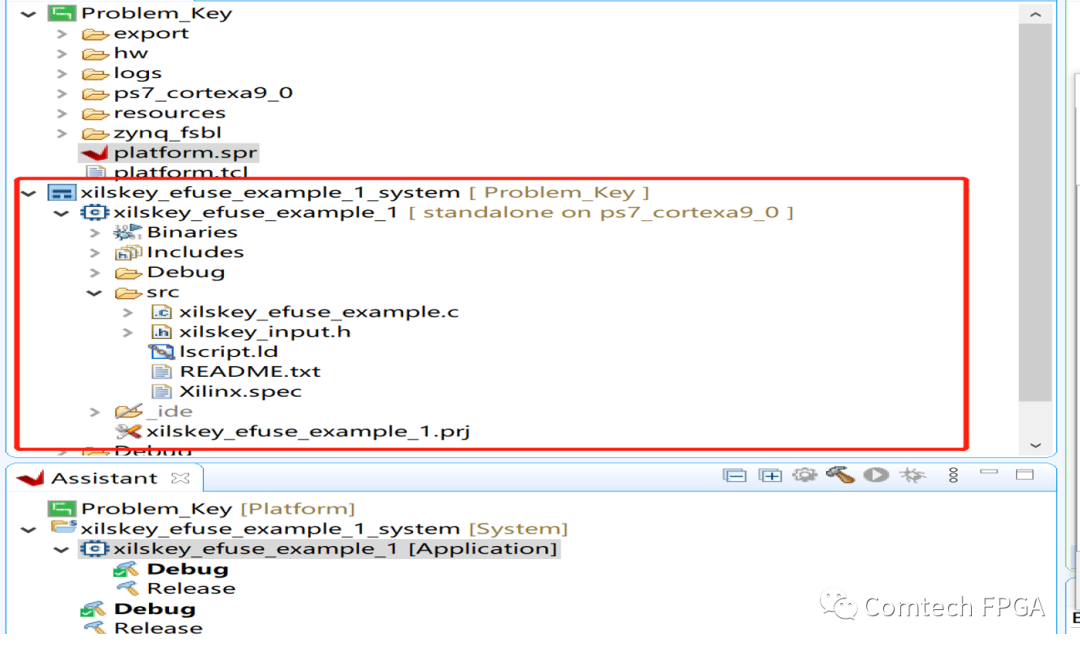

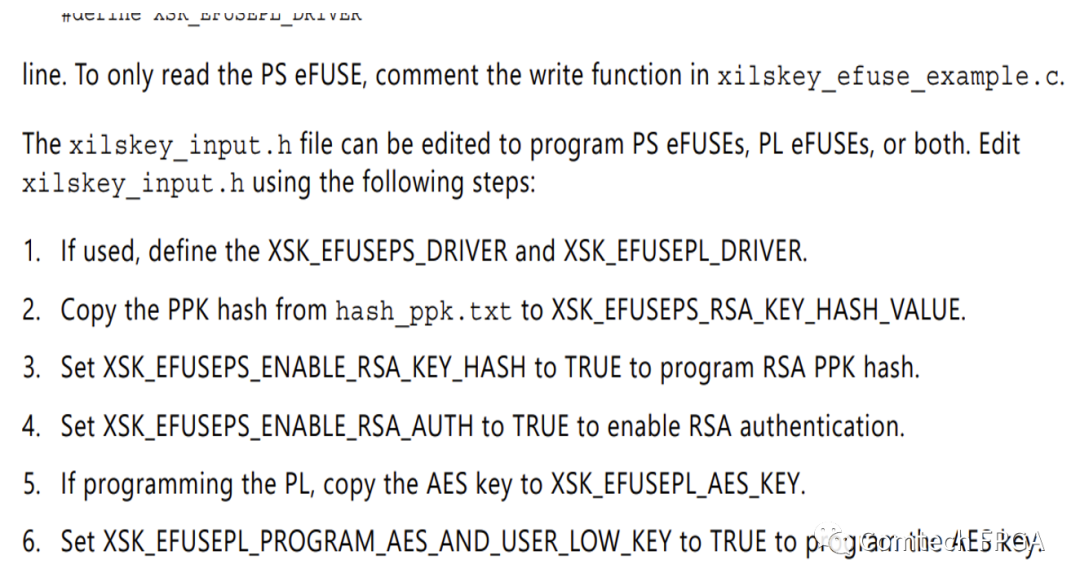

e、在Libraries中出现以下选型,选择并导入对应的工程:

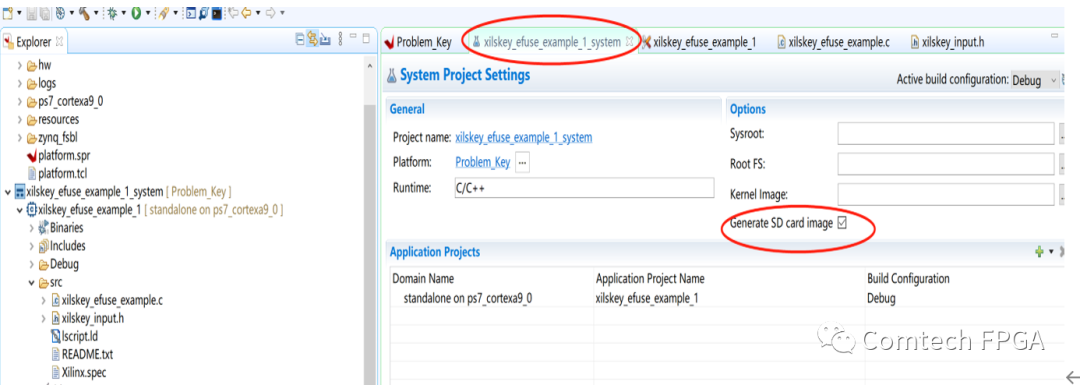

f、选择Generate SD card image:

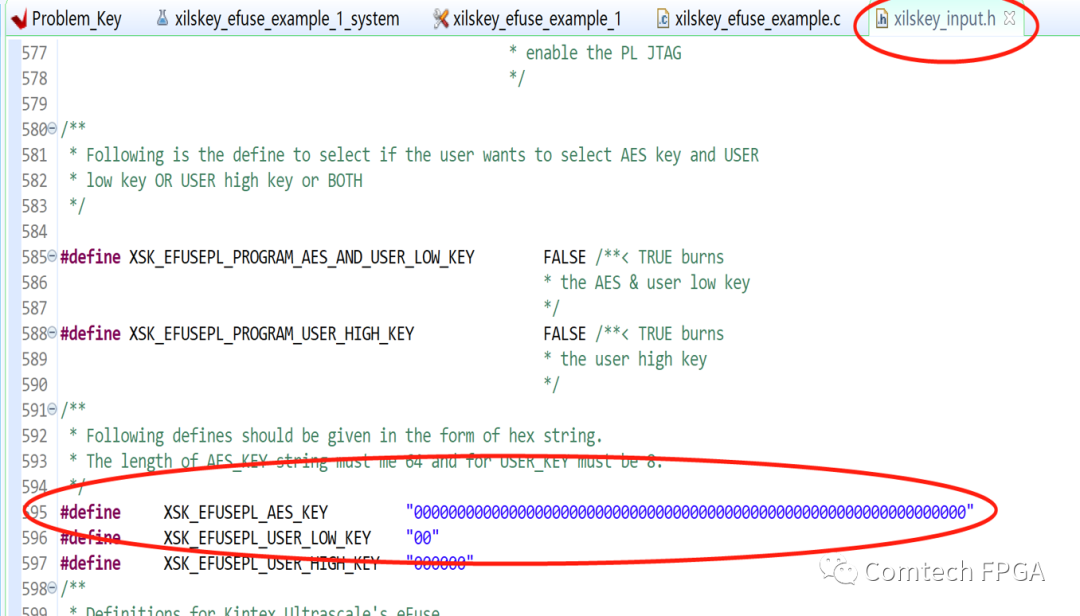

g、双击xilskeky_input.c,修改AES_KEY和对应的宏:

3、重要的环节来了,注意了:

原理讲解:SDK or Vitis 自带的example 中其实是封装了一个JTAG库,库中包含了JTAG的烧录Efuse的相关的协议,这部分协议是不开放的。下面讲解的内容就是用自带的example实现烧录Efuse 。

4、硬件连接要求和测试:

a、设计原理图时:选择4个MIO,可以是PS的BANK0,也可以是BANK1,最好是3.3V的BANK;

b、连接4个MIO到JTAG的4个引脚,TDI/TDO/TCK/TMS;

c、根据具体的连接情况修改下面的参数,数字代表MIO后面的编号,如17代表MIO17;

d、注意不要使用特殊的MIO[2-8],因为这些引脚在上电初期用于特定功能的复用;

e、根据原理图上对应关系,修改一下代码;

f、生成Boot.Bin

g、找到生成的文件,拷贝文件到SD卡中;

h、设置MIO4/5为高,SD卡启动方式;

j、至此,只要启动一次,将自动完成对EFUSE的烧录。

参考文档

1. Zynq UltraScale+ MPSoC: Embedded Design Tutorial (UG1209)

2. Zynq UltraScale+ MPSoC: Technical Reference Manual (UG1085)

3. Internal Programming of BBRAM and eFUSEs (XAPP1283)

4. Secure Boot of Zynq-7000 SoC (XAPP1175)

5. Zynq UltraScale+ MPSoC Technical Reference Manual (UG1085)

6. Changing the Cryptographic Key in Zynq-7000 SoC (XAPP1223)

7. Zynq UltraScale+ MPSoC Software Developer Guide (UG1137)

8. Key Revocation Lab (XAPP1344)

9. External Secure Storage using the PUF (XAPP1333)

10. Zynq UltraScale+ MPSoC: Embedded Design Tutorial (UG1209)

如果您在此方面有疑问,欢迎联系: