本文转载自:FPGA的现今未微信公众号

注:本文由作者授权转发,如需转载请联系作者本人

大家使用xilinx的多die FPGA时,或多或少的都遇到过时序收敛问题,那么对于多die的FPGA我们应该如何做好设计了。

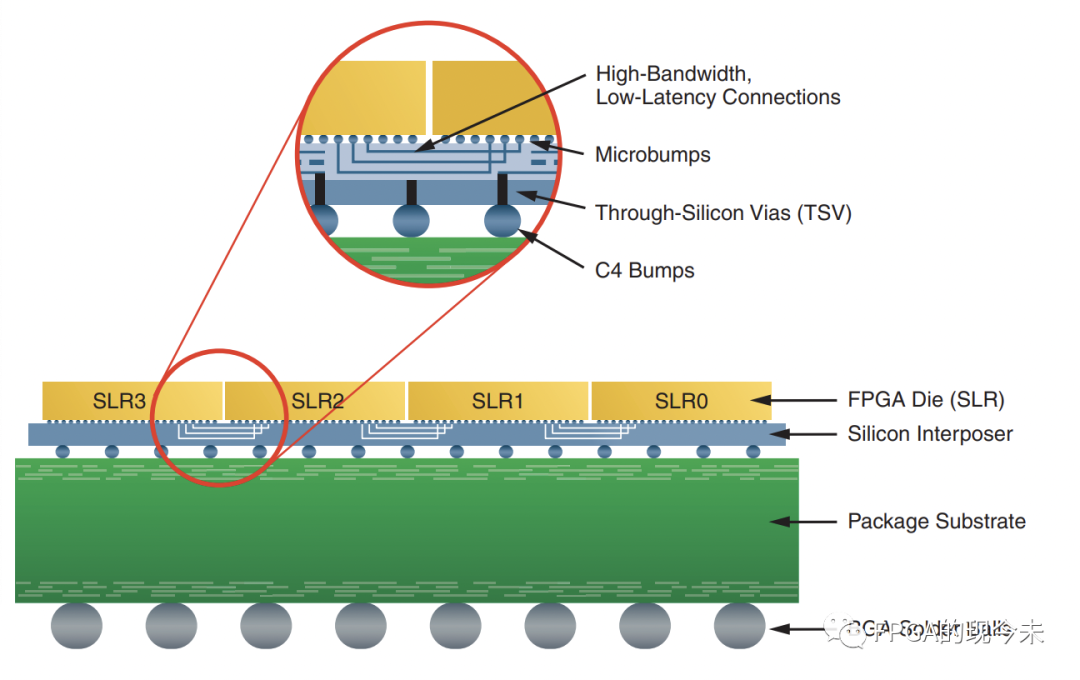

多die芯片其实是SSI(Stacked Silicon Interconnect)芯片,其结构如下图所示。其实就是在一个封装里,把多个芯片,也就是我们说的SLR(Super Logic Region)用interposer“绑”在一起,SLR之间的连接用专用布线资源SLL(Super Long Line)。

该截图来自xilinx文档872 - Large FPGA Methodology Guide (v14.3)

多die芯片为什么容易出现时序问题了,一个是SLL资源有限,两个SLR之间的SSL资源是有限的,比如U55N卡上2die芯片的SSL有23040。第二个就是本身die之间的走线延时相对比较长。这里就作者曾经遇到的问题总结下,如何从方案的角度规划,提前规避这类时序收敛问题。

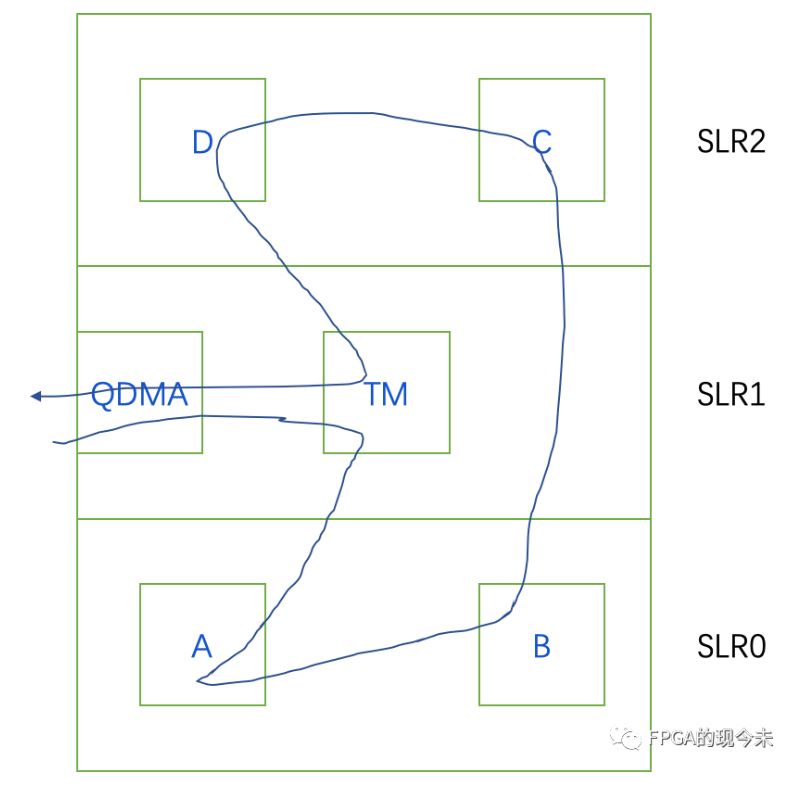

第一、从方案架构设计的角度看,FPGA的设计也就是数据流的设计,即数据流在不同模块之间的走动。多die芯片中,关键就是处理数据流跨die的问题。在方案设计阶段,首先要考虑一级模块在各个die中的分布。如何分配各个一级模块,如下图所示,主要从2个方面考虑。

(1)、资源,各个一级模块分布在各个die的时候,要进行合理的资源评估,考虑到资源占用情况,建议每个die中LUT不要超过70%,REG不要超过80%,RAM不超过80%。即moudle A + moudle B的资源尽量不要超过上述限制,如果超过,就要考虑把一个模块做拆分,移入SLR1或者SLR2中。

(2)、数据流,以die为单位,做到高内聚、低耦合。一级模块之间的接口要简单,尽量采用流式接口。数据流也要简单,不要在各个die之间来回穿越。即一级模块划分的时候,不断要考虑资源,还要考虑数据流的走向。

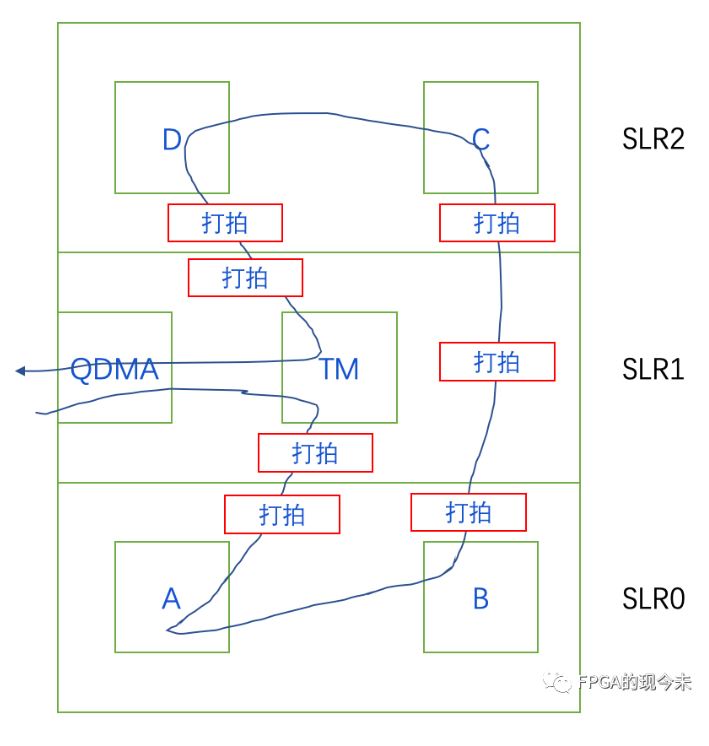

第二、在具体实现中,对于跨die的信号处理,官方的文档(ug949)中提供了2种方式,一种是通过约束的方式使用LAGUNA寄存器,一种是通过自动流水打拍的方式。秉承问题的解决能用代码就不用约束的思想,这里介绍一种和官方指导的第二种方案类似的方法,但是是用RTL代码解决,可移植性更好。

如下图所示,红色打拍逻辑(将所有的跨die信号打2-3拍)插入在跨die数据流的两侧。对于穿越整个die的数据流,比如module B到module C的数据流,可以在中间die插入一个过桥的打拍模块。这种方案在实践中被证明也能很好地解决时序收敛问题。

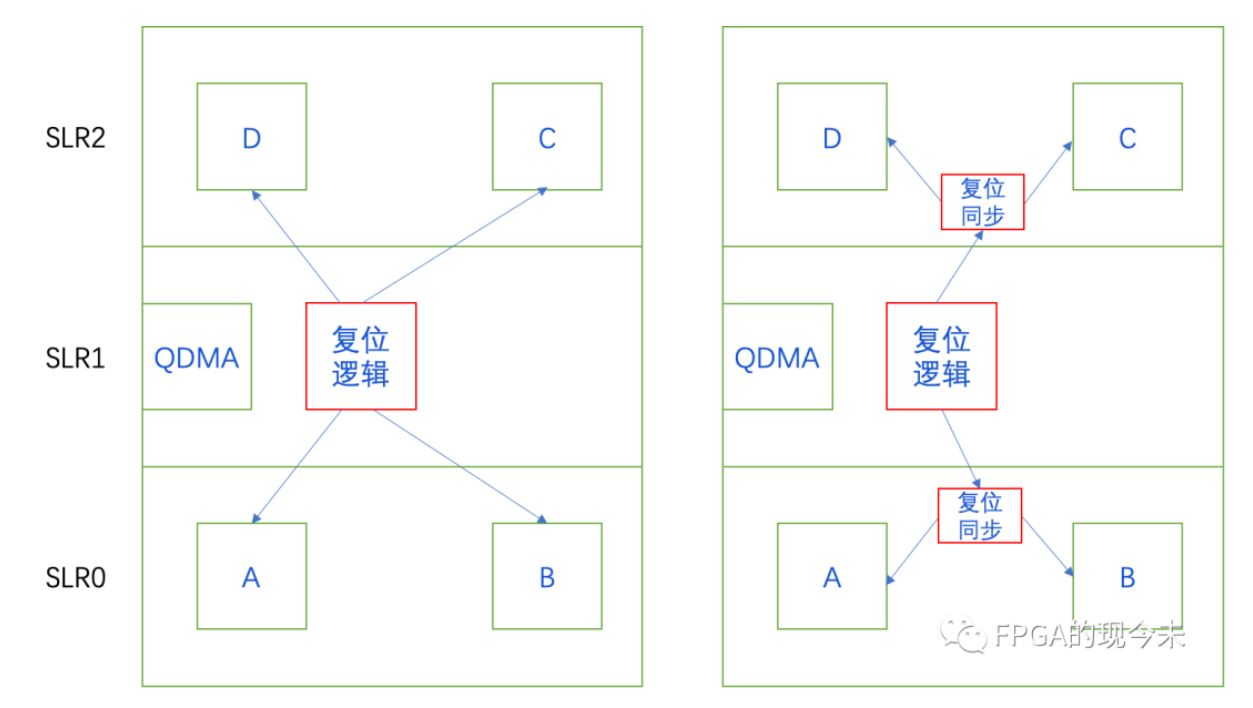

第三、复位信号的处理。跨die逻辑中有一类时序收敛问题就是复位信号的问题。笔者曾遇到一个问题,如下左图所示,复位逻辑在中间的die,复位3个die的所有逻辑。每个die的资源消耗比较高,LUT在70%,RAM在80%,REG相对好点,不到50%。最终因为扇出较大,导致Recovery不满足。

解决方案很简单,就是将复位信号先同步到各个die后,只复位一个die的逻辑,这样很好地解决了大量复位信号跨die问题,如下右图所示。

总结,解决多die FPGA的时序收敛问题,就是合理规划数据流、复位的方案,跨die数据流做好“桥接”。

你在跨die方案中遇到过哪些问题,欢迎留言交流补充。