文章转载自: 明德扬FPGA科教

明德扬(MDY)在2022年承担了多个高速ADC研发项目,今天给大家分享下高速ADC噪声系数计算方法。

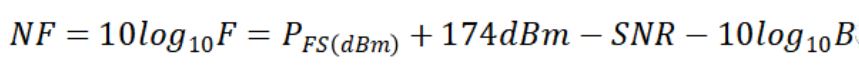

首先在AD选型时,我们最关心的一个指标就是AD的信噪比(SNR),这项指标直接影响了抗干扰板的噪声系数。噪声系数(NF)的计算过程如下:

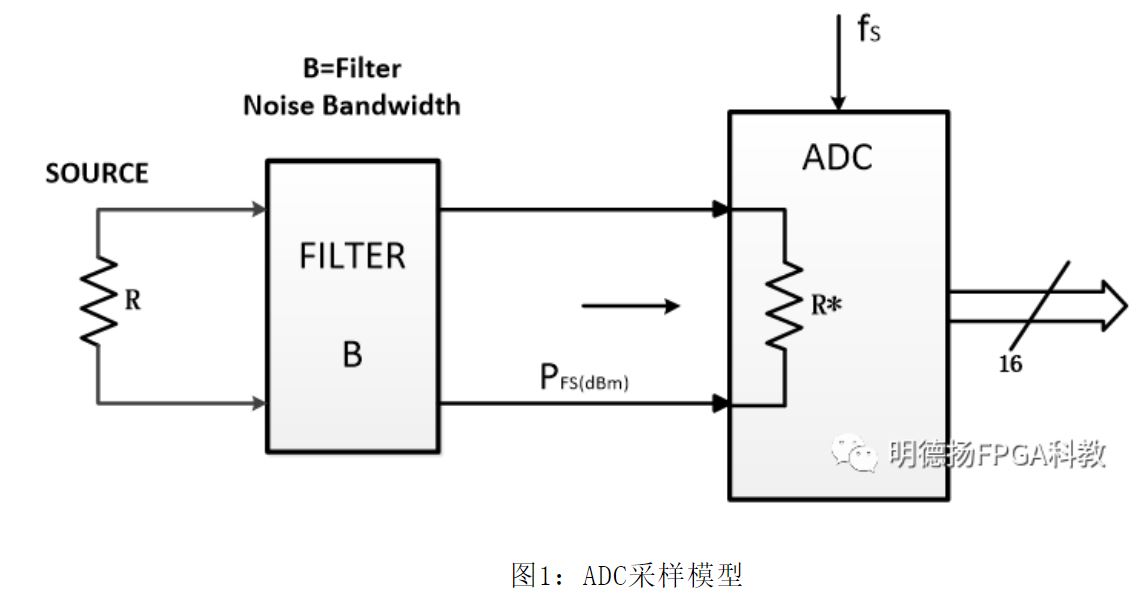

图1为ADC采样过程的一个简易模型。该模型假定一个电阻为R的信号源作为ADC的输入。由于有ADC采样时钟的限制,信号源与ADC之间相当于接入了一个奈奎斯特带宽(DC至fS/2)的滤波器。同时,这也限制了输入信号的噪声带宽。设该带宽为B。在ADC端的电阻R*为ADC的输入阻抗。由于我们设计电路时已经根据数据手册提供的参数对输入端进行了阻抗匹配,因此在该模型中认为ADC的输入阻抗等于源电阻。

图1:ADC采样模型

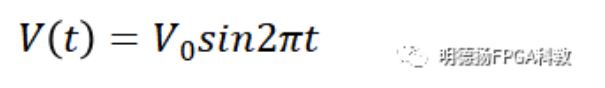

设输入信号功率为AD的满量程输入功率,则该电压表达式为:

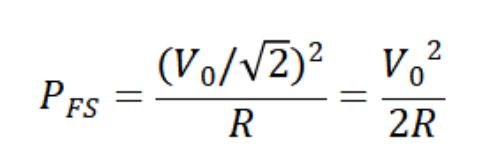

该正弦波信号的满量程功率为:

将其表示为dBm:

利用ADC的SNR值计算等效输入均方根电压噪声(该SNR值不包括基波信号的谐波):

上式是在整个奈奎斯特带宽(DC至fs/2)测得的总有效输入均方根噪声电压,注意该噪声包括源电阻的噪声。由此得到噪声因数F的表达式:

其中,SNR的单位是dB,B的单位是Hz,T=300K,

将F转化为dB并简化可获得噪声系数: