问题描述:

在 Vivado 2022.2 中使用 Advanced I/O Wizard 并配置源同步 TX+RX 接口时,RX/TX 单端和差分管脚对(总计 54 个管脚)理应能置于单个 bank 内。

但如果 bank 接近已满,该 Wizard 可能无法找到最优管脚分配,并出现以下错误:

[IP_Flow 19-3478] Validation failed for parameter 'Number of Banks(MAX_BANKS)' with value '1' for IP

'advanced_io_wizard_test/advanced_io_wizard_test_phy_test'.Selected configuration of data and strobe pins cannot fit into 1 Banks.Please update the Number of Banks to 2 Banks

解决方法:

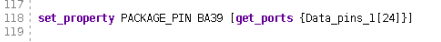

这是一个已知问题。要找到此问题的变通方法,在使用 Advanced I/O Wizard 配置源同步 RX+TX 接口时,请在“Advanced”选项卡下,将“Number of Banks”设为“2”,如下所示:

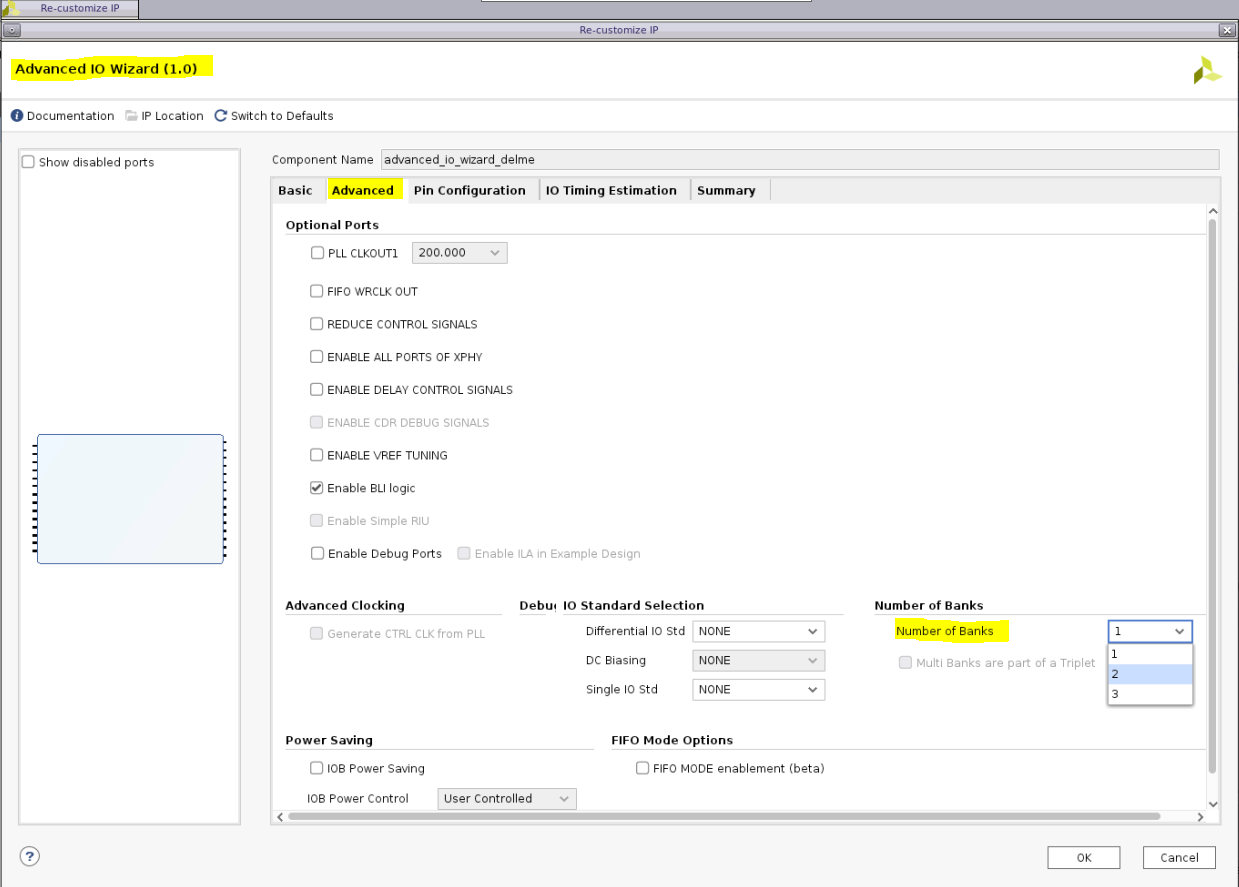

在“Pin Configuration”选项卡中,将您的管脚设为必需。

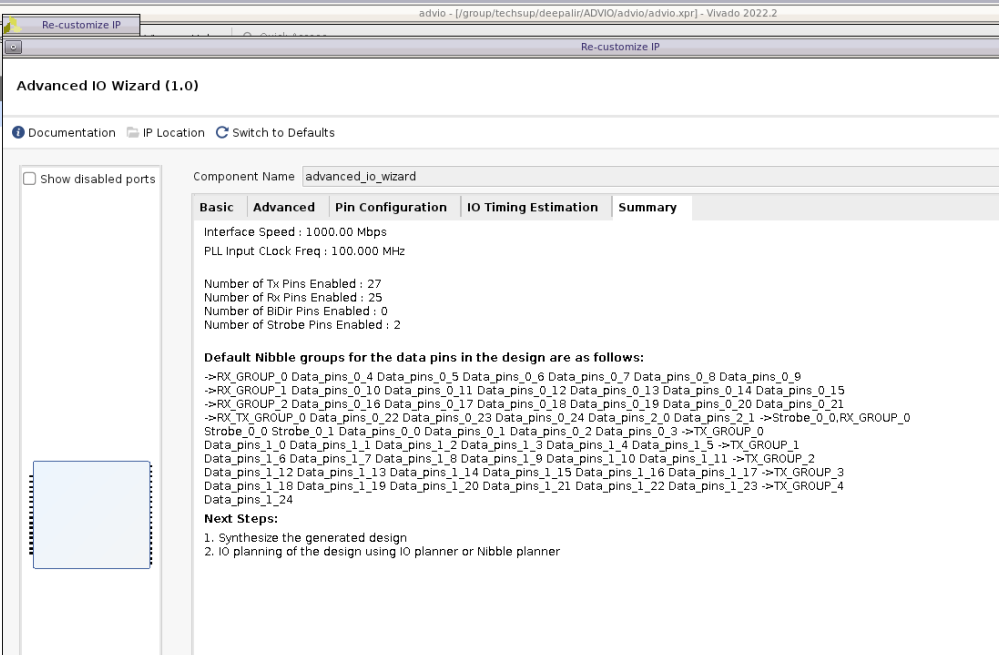

如上示例所示,共有 25 个 RX 单端管脚、1 个差分选通/时钟管脚对(2 个管脚)、25 个 TX 单端管脚、1 个 TX 差分管脚对 Clk_fwd(2 个管脚)。

该 Wizard 将创建 10 个半字节组 - RX_Group_0、RX_Group_1、RX_Group_2、RX_TX_Group0、Strobe_0_0_Group_0、TX_Group_0、TX_Group_1、TX_Group_2、TX_Group_3 和 TX_Group_4。

这些半字节组跨 2 个 bank。

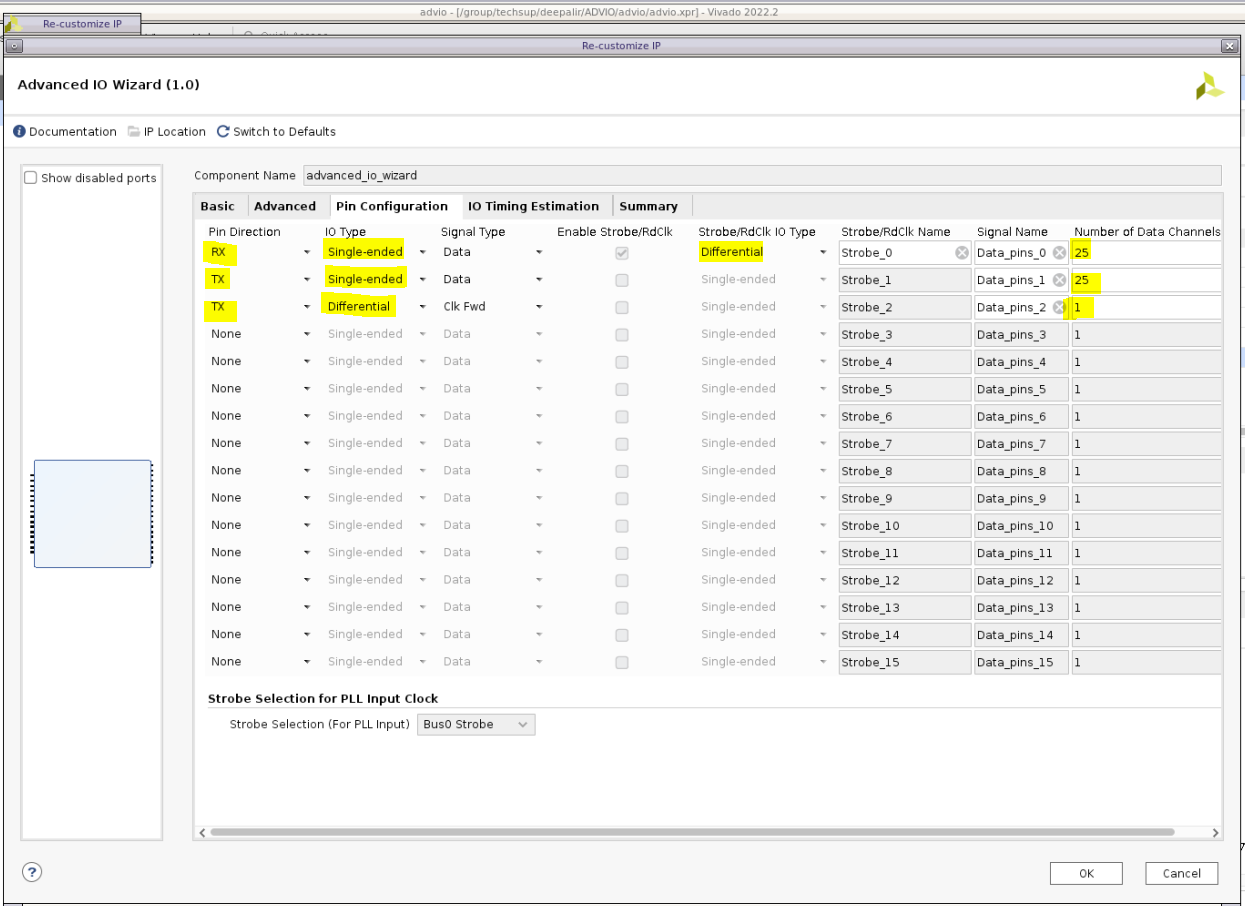

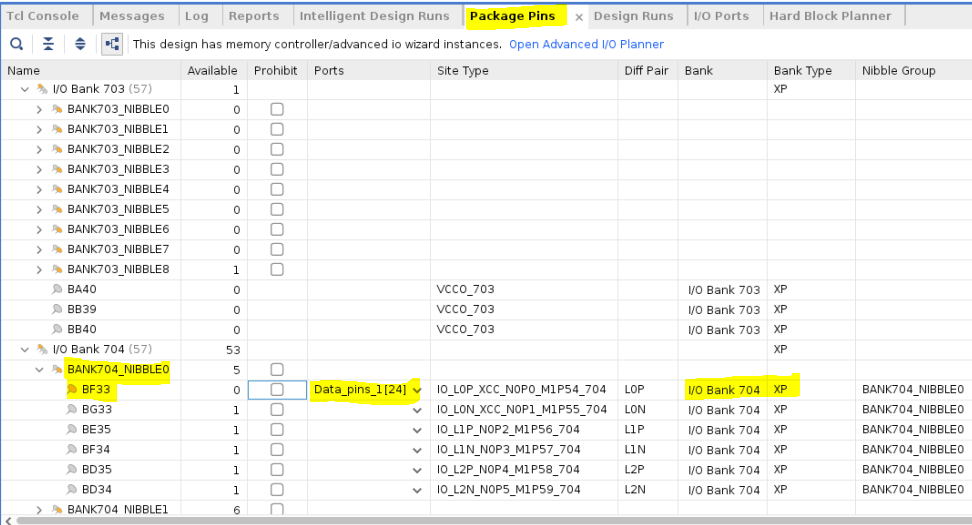

随后,您可将这些管脚强制置于 1 个 bank 内。

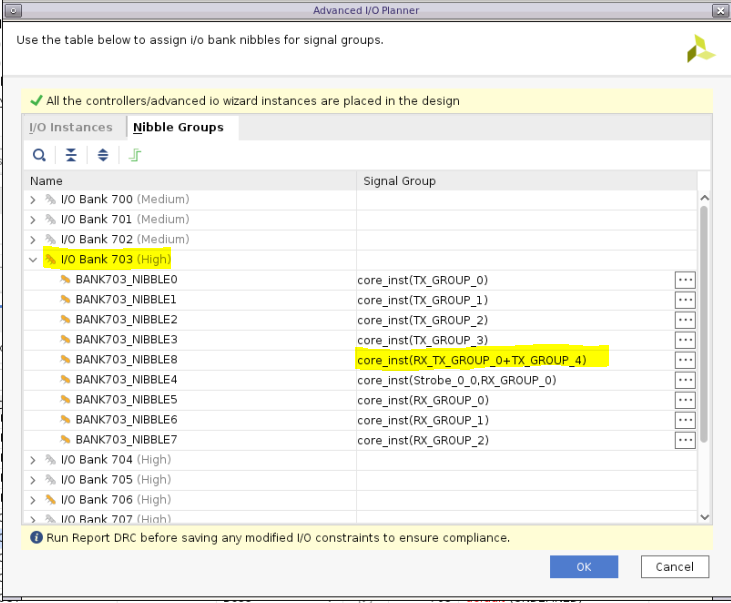

要执行此操作,请在“Advanced I/O Planner”中,将 9 个“Nibble Group”布局到 1 个 bank 中。

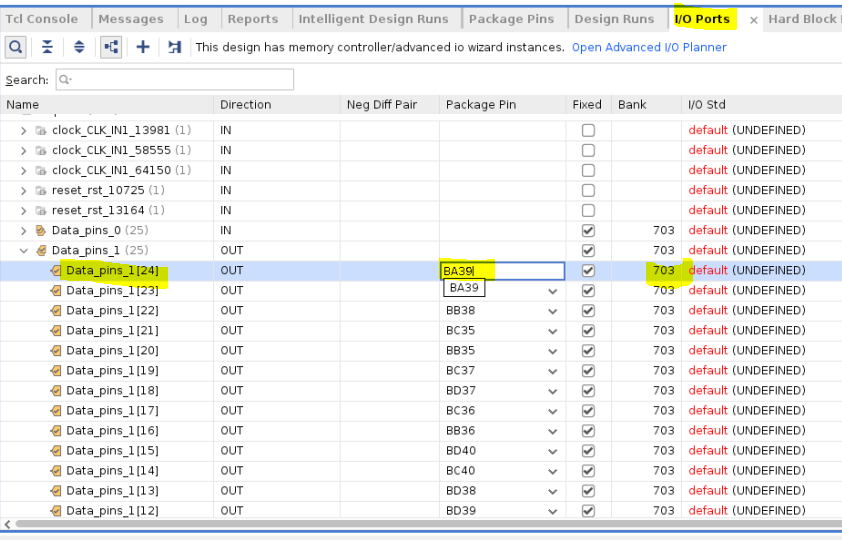

然后,使用管脚分配器(“I/O ports”选项卡或“Package pin”视图),将最后一个管脚布局到该 bank 内,方法是添加一个管脚位置或者在 XDC 约束中手动添加该管脚。