作者: Jesse Zhang,文章来源: Comtech FPGA微信公众号

一、背景及应用场景

在 ASIC SoC 开发设计过程中,原型验证(Prototype)和硬件仿真(Emulator)是两种不同的验证方法,AMD Xilinx FPGA在Prototype 和Emulator方案发挥着重要作用。

Prototype是指使用可编程逻辑构建的硬件平台,用于验证 ASIC 或 SoC 设计。原型设计的主要目的是在硬件级别模拟整个芯片系统,以便在实际生产 ASIC 或 SoC 芯片之前识别和解决潜在的设计问题。它使得设计人员能够快速验证 ASIC 设计的功能和性能,同时也可对 IP/RTL 进行验证。

Emulator是一个专用的硬件设备,用于在更高层次上模拟芯片设计的功能和性能。与原型设计相比,仿真器可以在设计流程的早期阶段进行验证,从而在整个设计过程中节省时间和成本。往往使用 FPGA 来模拟 ASIC 设备的行为,这使得设计人员在设计、验证和优化 ASIC 设备之前进行快速迭代和测试。

比如Synopsys 的 HAPS FPGA 原型解决方案,使用 Xilinx 的 Virtex UltraScale 系列 FPGA 器件。它提供了模块化、可扩展的原型设计平台,可以满足各种 ASIC 和 SoC 验证需求。HAPS解决方案还包括专用的原型编译器,以便将 RTL 代码高效地转换为 FPGA 实现。

在搭建Prototype或者Emulator平台时,单片FPGA资源往往逻辑容量不够,需要在多个 FPGA 设备之间传输大量数据,在这些应用场景中,片间通信尤为关键,需要在多个 FPGA设备之间传输大量数据。

在Vivado设计套件中,提供有AXI Chip2Chip IP,它提供了高吞吐量和低延迟的数据传输实现方式,成为实现片间通信的理想选择。

本文详细介绍基于北京芯加速科技有限公司(www.xspeed.net.cn)的VU13P平台,使用AXI Chip2Chip IP,开发测试了一套用于ASIC验证仿真的片间通信方案。

图一:芯加速VU13P FPGA 板卡硬件实物图

二、AXI Chip2Chip IP详细介绍

AXI Chip2Chip IP 是一种基于 AXI4 协议的高性能片间通信解决方案,支持灵活的参数配置,如数据宽度、时钟频率等。这使得它可以在多个芯片之间实现高速、低延迟的数据传输,从而提高 ASIC SoC 原型设计和 ASIC 模拟器的性能。

本文demo主要涉及片间高速通信,选择Aurora64B/66B接口和AXI4总线,通过VU13P的25Gx4光口进行互联,实现两片VU13P片间通信。

图二:VU13P C2C 互联实物图

2.1 设计:

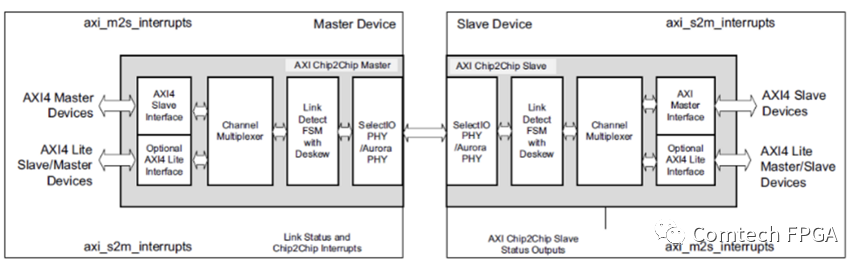

AXI Chip2Chip 的功能类似于bridge,可通过 AXI 接口无缝连接两个设备, AXI Chip2Chip (C2C) IP 分为两部分,C2C 主机和 C2C 从机,并且是点对点连接,因此每个slaver需要一个单独的master。如下图所示,C2C master 有一个 AXI4 slave 接口。C2C master AXI 接口上的任何 AXI 事件都被打包并通过收发器传输到 C2C slaver。

图三:Xilinx AXI Chip2Chip Master and Slave

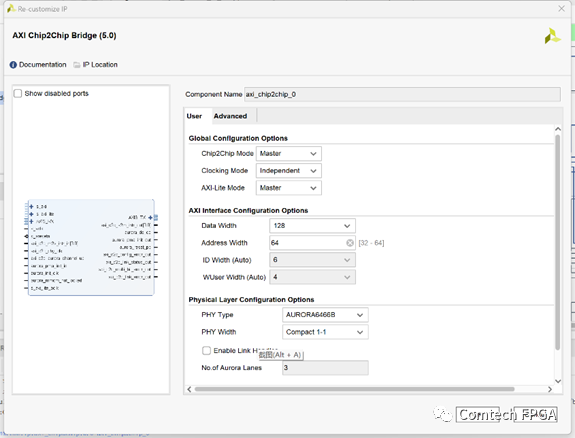

首先,根据应用场景和性能要求,配置 AXI Chip2Chip IP 的参数,如数据宽度、时钟频率等。

图四:AXI Chip2Chip IP

下面详细介绍各配置选项含义:

全局配置选项:

Chip2Chip AXI Mode:选择主从模式;

AXI Clocking Mode:时钟配置,选择 Chip2chip 核的钟和 SelectIO 的钟是否同步;

Chip2Chip AXI4-Lite Mode:AXI4-Lite模式选择;

AXI接口配置选项:

AXI Data Width:数据位宽选择,主设备和从设备数据位宽需保持一致;

AXI ID Width:为通道的信号提供标识,主从设备需保持一致;

AXI WUSER Width:写数据通道传输的边带信息,主从设备需保持一致;

物理层配置选项:

Chip2Chip PHY Type:物理层接口类型,有 SelectIO DDR, SelectIO SDR, Aurora 8B/10B, Aurora 64B/66B选择;

Chip2Chip PHY Width:宽度选择,主设备和从设备中间的 FPGA IO的实际数量;

Chip2Chip PHY Frequency:当接口类型为 SelectIO 时,共同钟(common clock)模式下,m_aclk_out由MMCM产生,Chip2Chip PHY Frequency为 MMCM 的参考频率;

Enable Link Handler:选择后,增加axi_c2c_lnk_hndlr_in_progress指示端口;

本文测试的片间通信使用了光口进行传输,所以选择了Aurora接口,Aurora 64B66B是一个轻量化的,多吉比特(multi-gigabit )链路串行通信协议,用于一个或多个GTX,GTH或GTY收发器之间的数据传输,连接可以是全双工(full-duplex)的或单工(simplex)的。这里就不展开介绍了。

2.2 集成:

然后,在 Vivado 设计套件中将 IP 集成到 FPGA 设计中,并将其连接到其他模块,如处理器、内存控制器等,这里的测试demo,是由Traffic Generator生成数据,发送给C2C IP,通过25G X 4光口传输出去,到对方芯片接收后进行Check。

图五:DUT架构图

图六:Vivado 工程Blockj design框图

图七:Vivado 工程dataflow

2.3 仿真:

由于AXI Chip2Chip用于片间通信,IP生成的example,会自动在simulation的代码中例化对端的IP。比如IP设置的Master,simulation的代码中会自动加一个slave端,反之亦然。

在设计完成后,使用仿真工具验证 AXI Chip2Chip IP 的功能正确性。根据仿真结果进行调整和优化。

图八:AXI Chip2Chip IP 仿真波形图(从上到下 lane-up拉高、读数据、写数据)

2.4 上板验证:

将设计烧录到VU13P FPGA 芯片上,并通过实际硬件测试 AXI Chip2Chip IP 的性能。可使用逻辑分析仪或其他测试工具对通信进行监控和分析,确保其满足应用要求。在硬件上实际验证 AXI Chip2Chip IP 的性能,包括测试通信带宽、延迟等关键参数。

图九:功能仿真结果

三、AXI Chip2Chip IP的优缺点

优点:

高吞吐量:AXI Chip2Chip IP 支持高速数据传输,可实现高性能片间通信,比如本文设计实现了25Gx4光通信;

低延迟:AXI Chip2Chip IP 可降低片间数据传输延迟;

灵活性:支持多种参数配置,适应不同的应用场景和通信需求;

缺点:

设计复杂性:AXI Chip2Chip IP 的集成可能略微增加设计复杂性,需要花费更多时间进行验证和优化;

资源消耗:AXI Chip2Chip IP 可能占用一定的 FPGA 内部资源,如逻辑、存储器和互连资源;

四、结论

在本文使用的VU13P FPGA 中,AXI Chip2Chip IP 结合VUP这类大规模逻辑器件为 ASIC SoC 原型验证和 ASIC 仿真器等应用提供了高性能、低延迟的片间通信解决方案。通过深入理解 AXI Chip2Chip IP、光互联等,设计人员可以充分发挥它们的潜力,提高设计性能和效率。同时,也需要注意设计复杂性和资源消耗等潜在挑战,通过优化设计方法和充分利用 Xilinx 提供的技术支持和设计资源,确保成功实现高性能的片间通信设计方案。

如果您在AXI Chip2Chip、高速片间互联方面有问题,欢迎联系:

simonyang@comtech.cn

charlesxu@comtech.cn