AMD又要出大招了。

AMD将在明年推出Zen5架构的锐龙8000系列、霄龙9005/8005系列,更下一代的Zen6架构也已经崭露头角,据说可以支持到史无前例的16通道内存。

现在,MLID曝光了一份AMD架构路线图,列出了Zen5、Zen6的不少细节,尤其是前者料很猛。

AMD Zen架构家族采取了波动式升级策略,一代大改、一代小改交替进行,比如Zen5就会是一次大改,Zen6则是一次小改。

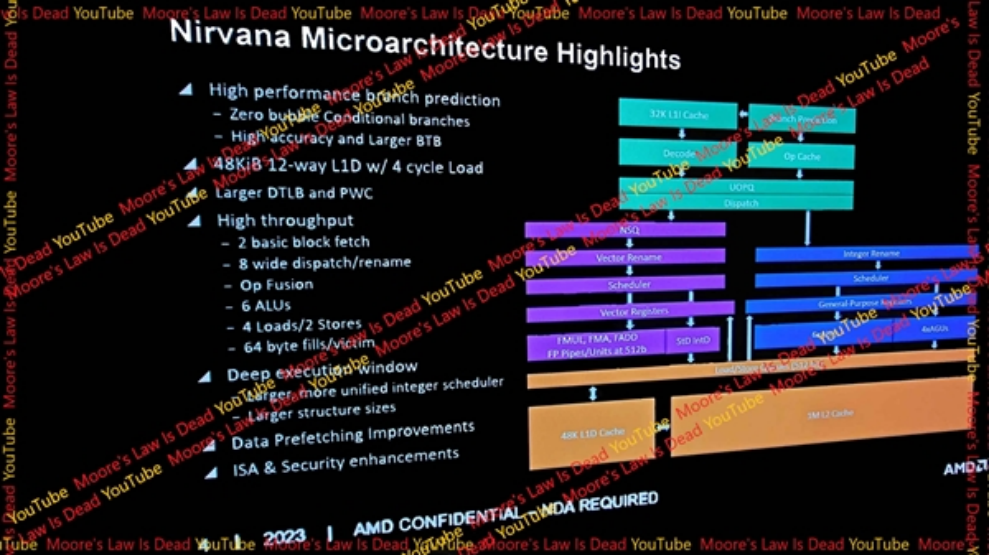

Zen5架构代号Nirvana(涅盘),预计会将IPC提升大约10-15%,对比Zen3 19%、Zen4 14%似乎不是很突出,但一则这是早期预估目标,不排除未来进一步提升,二则也要考虑频率同步提升所带来的性能增益。

另一点就是首次大范围应用“大小核”混合架构,搭档Zen5c,但应该主要面向笔记本。

制程工艺方面,CCD升级为3nm,IOD升级为4nm。

尤为值得注意的是,Zen5将会首次支持原生16核心的CCD,相比这几代的8核心翻了一番,使得桌面主流32核心成为可能。

其它方面,一级数据缓存容量从32KB增至48KB,同时8路关联升级为12路,不过一级指令缓存仍是32KB, 二级缓存仍是每核心1MB。

分支预测继续提升性能和精度,数据预取继续改进,ISA指令与安全继续增强,吞吐能力也进一步扩大,包括8宽度的分派与重命名、6个ALU算术逻辑单元、4个载入与2个存储,等等。

Zen6架构代号Morpheus(希腊神话梦神摩耳甫斯),制造工艺将会进一步升级到CCD 2nm、IOD 3nm,而且CCD再次升级为原生32核心!

IPC性能预计再提升10%,同时加入面向人工智能、机器学习的FP16指令,以及新的内存增强。

此外,Zen6据说还会有新的封装技术,可能会将CCD堆叠在IOD之上,可以达到缩小芯片面积、提升内部通信效率,但就没法直接堆成64核心了。

Zen6大概率会继续沿用AM5封装接口,毕竟AMD承诺过要支持到2026年。

Zen5:Zen架构诞生以来最大飞跃

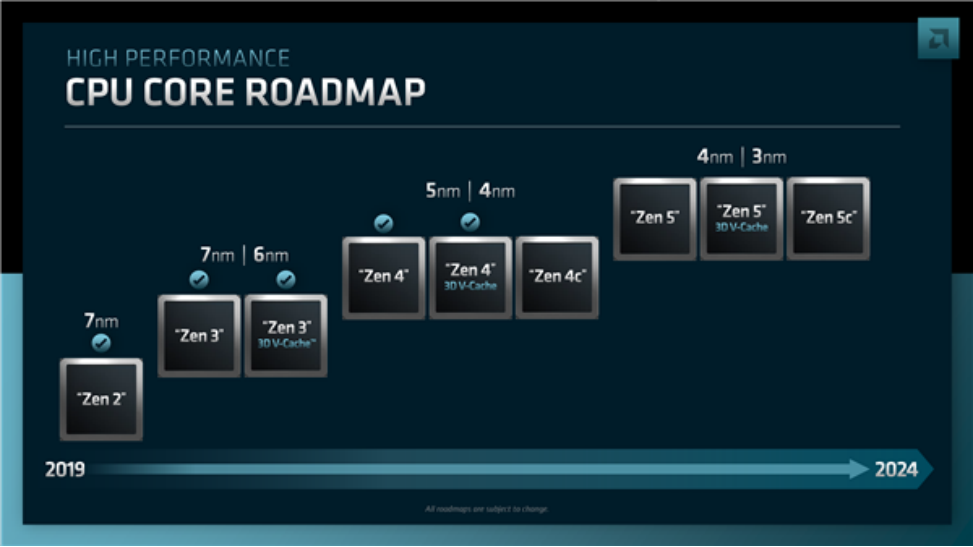

AMD早已在官方路线图上大大丰富地列出了下一代Zen5 CPU架构,升级为4nm、3nm工艺,2024-2025年陆续推出。

其中,服务器产品代号Turin,桌面上是Granite Ridge,笔记本上有Strix Halo、Fire Range,不少规格都已经曝光,相当震撼。

RedGamingTech现在首次曝光了Zen5的性能跑分,来自AM5桌面款的锐龙8000,早期工程样品,频率、功耗等测试条件未知。

最多还是16个核心,CineBench R23多核心跑分大约49000,相比目前的38000分左右提高了几乎30%!

同时,12核心36000分左右,8核心23000分左右,6核心17000分左右,与核心数量几乎呈完美的线性关系,都有显着提升。

单核心跑分在2500-3000分左右,依然超过了如今6GHz高频率的i9-13900KS!

别忘了,这还只是工程样品,后期仍有很大的提升空间,16核心的多核跑分突破5万分应该不是啥事儿。

值得一提的是,被誉为Zen架构之父的Jim Keller早期曾经曝光过一张幻灯片(后被删除),显示Zen5 SPECint跑分一枝独秀,遥遥领先,没有任何对手。

Jim Keller虽然早已离开AMD,但是他参与了Zen架构的设计,可以说为AMD这么多年的发展奠定了坚实的基础。

之前就有说法称,Zen5将是一次大改款,也是Zen诞生以来提升幅度最大的一次,甚至超越Zen2到Zen3的变化。

同时,Zen5时代AMD也将正式全面采用大小核心设计,Zen5搭配衍生版本Zen5c,但后者的IPC、ISA都不变,主要只是精简缓存,这和Intel的异构大小核截然不同。

Zen6霄龙首曝:史上第一次16通道内存

根据官方路线图,AMD将在明年推出Zen5架构家族,其中在EPYC霄龙服务器端将延续现有体系,划分为Zen5(代号Turin)、Zen5 3D V-Cache、Zen5c三个版本,制造工艺升级为3/2m(应该分别是CCD、IOD)。

那么再往后的Zen6呢?

最新曝光的一张路线图显示,AMD Zen6架构霄龙的代号为“Venice”,也就是意大利水城威尼斯,延续该系列一贯以意大利城市作为代号的传统。

封装接口改为SP7,而现在的Zen4家族是SP5,这意味着下一代Zen5家族会使用SP6,一代换一次。

规格方面只显示了一点,内存通道有16个、12个两种,这将是历史上第一次做到16通道,而现在最高只有12通道。

据说,Zen6架构霄龙CCD部分的制造工艺将升级为2nm,IOD则可能是3nm。

顺便回顾一下AMD历代CPU架构的内部代号和对应工艺:

Zen 2 (7nm) – Valhalla(英灵殿)

Zen 3 (7nm) – Cerberus(刻耳柏洛斯,古希腊神话中的地狱三头犬)

Zen 4 (4/5nm) – Persephone(珀耳塞福涅,古希腊神话冥后)

Zen 5 (3/4nm) – Nirvana(涅盘)

Zen 6 (2/3nm) - Morpehus(摩耳甫斯,古希腊神话梦神)

另外,路线图上可以看到AMD下一代Instinct MI400系列加速器,包括三个版本:MI400A肯定是CPU+GPU融合方案,MI400X是纯GPU方案,MI400C就不知道了。

Intel这边,至强处理器明年是纯大核Granite Rapids(GNR)、纯小核Sierra Forest(SRF),后续升级版分别是Diamond Rapids(DMR)、Clearwater Forest(FCS),但是在Intel官方路线图上,Diamond Rapids至少目前消失了。

加速器方面是下一代Falcon Shore,分为X、G两个版本,但不清楚什么区别。

它最初规划是CPU+GPU融合,但现在已经退回到纯GPU。

本文转载自:半导体产业纵横