来源:内容由半导体行业观察(ID:icbank)编译自servethehome,谢谢。

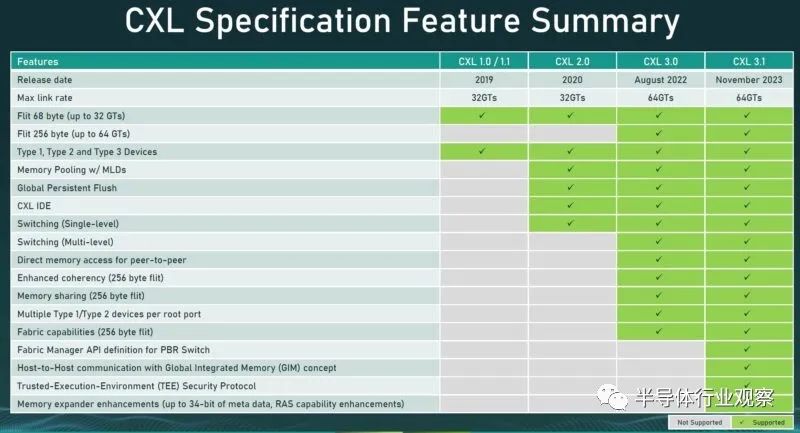

最近发布了 CXL 3.1 规范。新规范对横向扩展 CXL 进行了额外的结构改进、新的可信执行环境 ehnahcments 以及对内存扩展器的改进。

CXL 3.1 在底层进行了许多重大更改,主要是为了解决团队构建更大的 CXL 系统和拓扑时发生的问题。

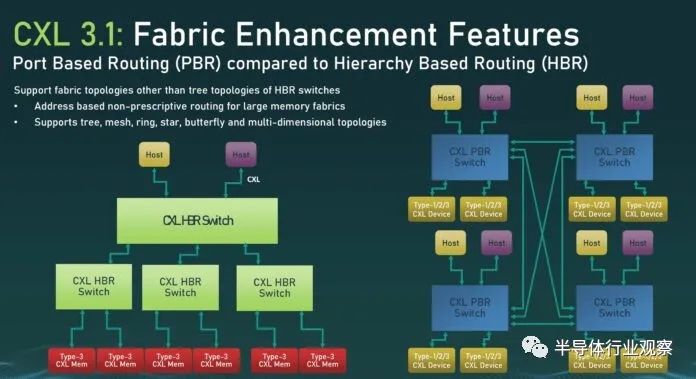

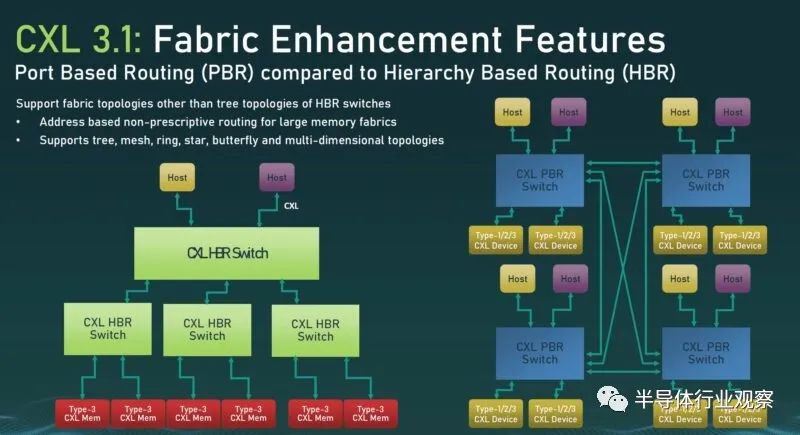

CXL 3 带来了基于端口的路由 (PBR) 等功能,这与基于层次结构的路由不同,后者更类似于 PCIe 树形拓扑。这是促进更大的拓扑和任意通信所必需的。

CXL 3.1 的一项增强功能是支持使用全局集成内存 (GIM) 通过 CXL 结构进行主机到主机通信。

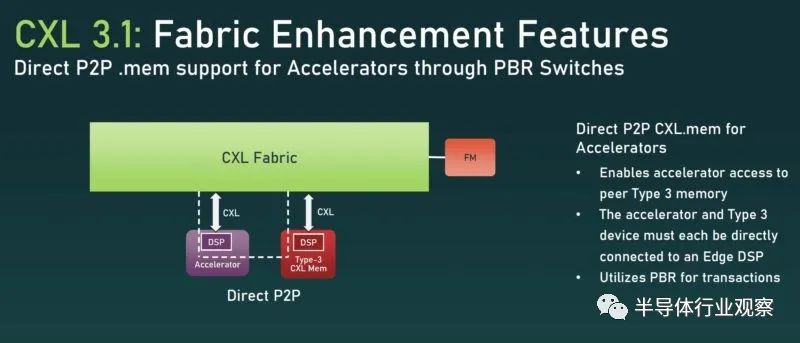

另一大问题是通过 CXL 对 .mem 内存事务的直接 P2P 支持。所有关于 GPU 内存容量的讨论都是 AI 的限制因素,这将是一种可以将 CXL 内存和加速器添加到 CXL 交换机上并让加速器直接使用 Type-3 CXL 内存扩展设备的用例类型。

还有针对基于端口的路由 CXL 交换机的 Fabric Manager API 定义。结构管理器最终可能会成为 CXL 生态系统的关键战场,因为它需要跟踪集群中发生的许多事情。

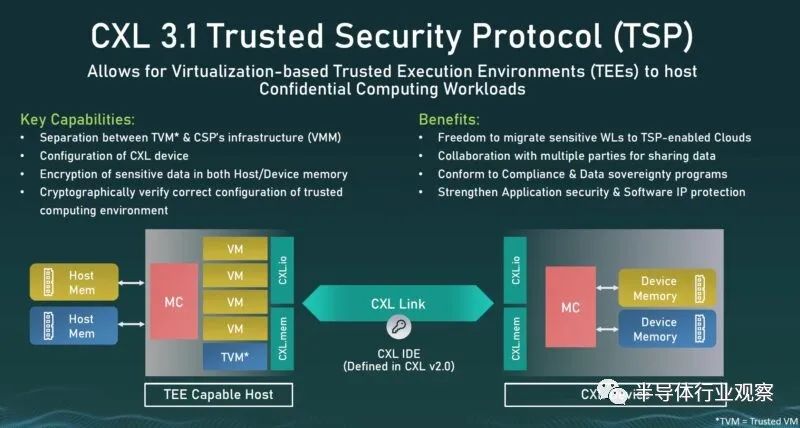

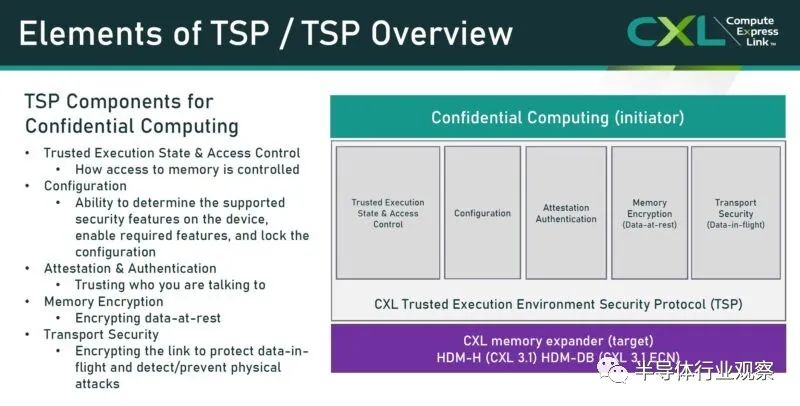

CXL 3.1 可信安全协议 (TSP) 是处理平台安全性的下一步。想象一下,云提供商拥有多租户虚拟机共享通过 CXL 连接的设备。

因此,诸如机密计算之类的当今云虚拟机中的热门话题需要扩展到服务器和连接到结构的设备的范围。

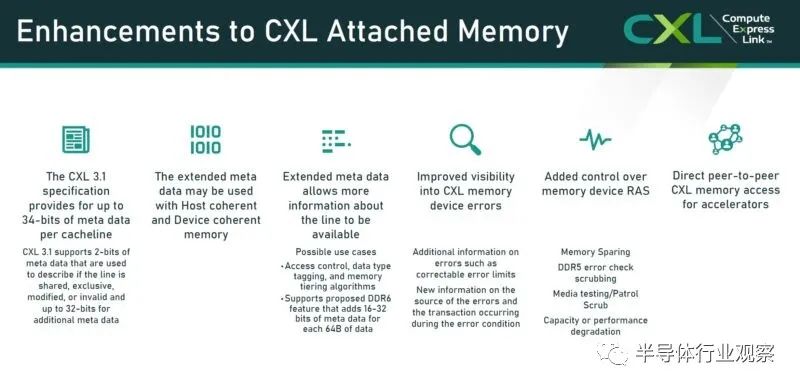

CXL 附加内存还获得了许多 RAS 功能以及元数据的附加位。同样,随着拓扑变得越来越大以确保可靠性,这一点很重要。

CXL 3.0/ CXL 3.1 就产品而言仍然远远不够,我们的感觉是,当我们看到产品投放市场时,大多数公司将采用 CXL 3.1 而不是 CXL 3.0。与此同时,我在 Supercomputing 2023 上向 CXL 人员提出的问题是,CXL 3.1 的设计是否足够大。目前,该规范是为连接数千个 CXL 设备而设计的。与此同时,我们今天正在用数万个加速器构建人工智能集群。在 CXL 世界中,连接的 CXL 设备可能比当今的加速器更多,因此我的问题是 CXL 是否也需要扩展。

还有很多工作要做,但好消息是,我们将开始看到 CXL 支持在 2024 年得到加强,不仅是实验性的,而且还有有用的生产用例。

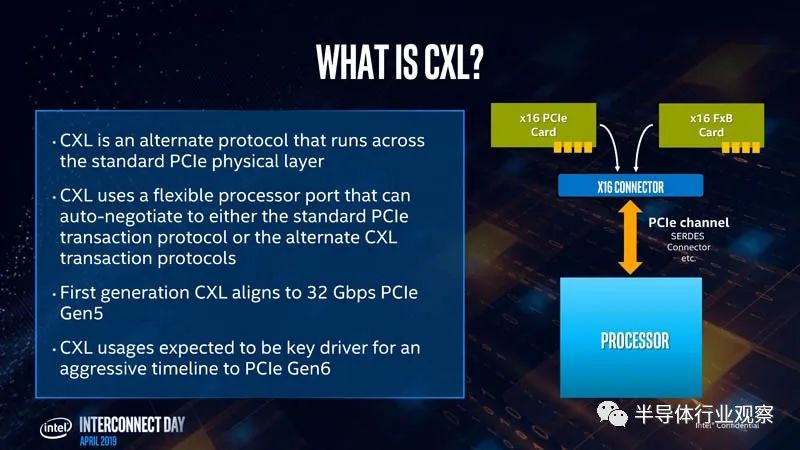

什么是 CXL?

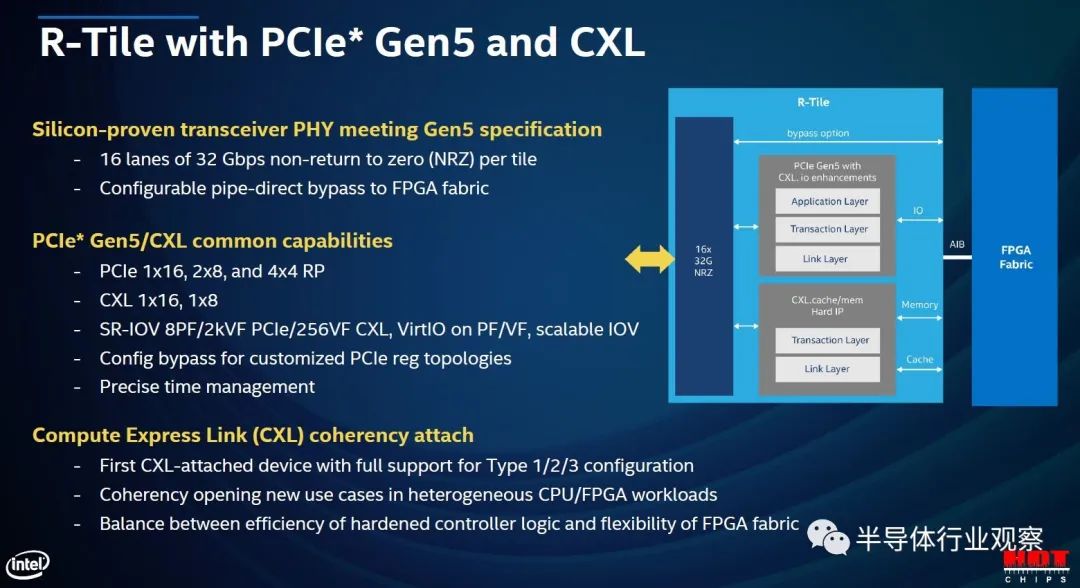

Compute Express Link 是一种缓存一致性链接,旨在帮助系统(尤其是具有加速器的系统)更高效地运行。CXL 位于 PCIe Gen5 链路基础设施之上。可以有 PCIe Gen5 设备,但许多 PCIe Gen5(或 PCIe 5.0)设备还将支持在 PCIe 或 CXL 模式下运行通道的能力。在某些方面,这类似于 AMD EPYC CPU 如何将其 I/O 通道作为 PCIe 或 Infinity Fabric 运行。这将成为一个广泛的行业标准,而不是特定于供应商的实施。CXL 的主要优点是它允许对直接连接到不同端点的内存进行加载/存储,这就是我们接下来要讨论的内容。

我们将在这里重点关注内存。内存是一个关键驱动因素,因为超大规模厂商意识到如今几乎每个设备都具有板载内存,而内存既是一个巨大的成本驱动因素,又常常因所连接的设备利用率不足而陷入困境。在更高的层面上,CXL 是系统在多个设备之间有效共享和利用内存的工具。我们今天在服务器的背景下讨论这些,但没有理由不能将其应用到服务器之外。

为什么PCIe Gen3/Gen4时代不使用CXL?

我们等待 CXL 的 PCIe 5.0 有几个原因。首先是时间安排。CXL 于 2019 年从引入到采用,这意味着 2021 年底和 2022 年初实际上是我们预计获得支持的第一代芯片,这些事情需要时间。

PCIe Gen5 的快速采用是一个关键推动因素。业界花了大约七年时间从 PCIe Gen3 过渡到 Gen4。PCIe Gen5 的过渡发生在 Gen4 之后大约 3 年。速度的大幅提升有效地将 PCIe Gen4 与 Gen5 的带宽加倍。由于 CXL 位于 PCIe Gen5 之上,我们通常会看到具有 32GT/s x16 链路的控制器,但 CXL 也可以支持 x8 和 x4 的分叉。有一些模式可以进入 x2 和 x1 链接,即所谓的“降级”模式。重要的是要记住,PCIe Gen5 x4 链路有足够的带宽来处理 100GbE 链路,因此起始级别代表大量带宽,类似于 PCIe Gen3 x16 链路。

额外的带宽意味着 PCIe 将有足够的带宽来处理新一类用例,特别是那些涉及前几代速度不够快而无法处理的远程内存加载/存储的用例。

对于那些想知道为什么这种情况没有早点发生的人来说,有三个主要原因。首先,我们需要 PCIe Gen5 的速度。其次,我们需要创建 CXL。第三,行业采用需要时间。现在我们已经拥有了这三者,CXL 就是未来。

CXL协议三重奏

CXL 使用三个主要协议:

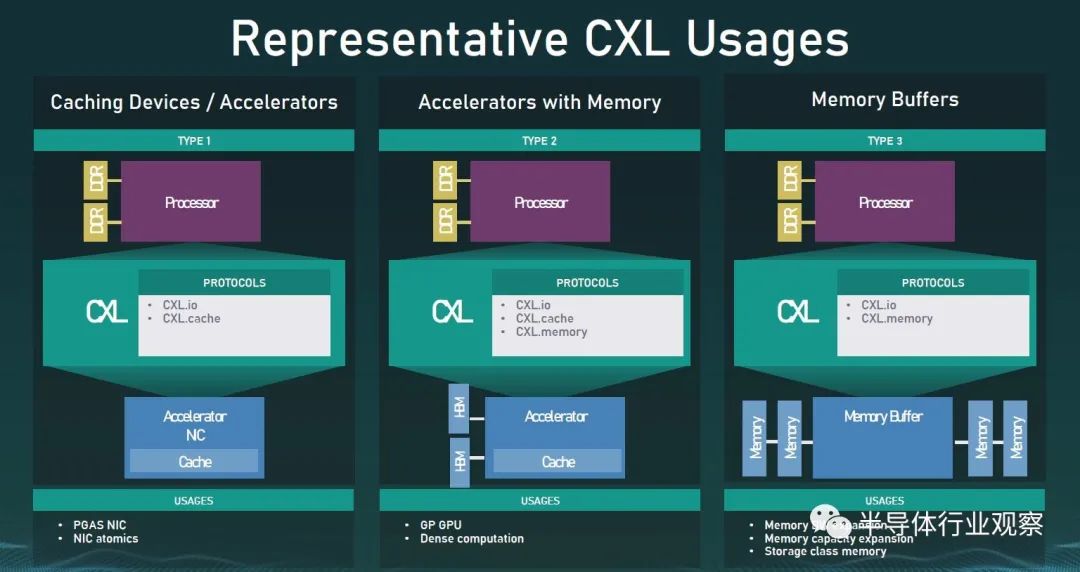

CXL.io是用于初始化、链接、设备发现和枚举以及寄存器访问的协议。它为 I/O 设备提供非一致的加载/存储接口,类似于 PCIe Gen5。CXL 设备还必须支持 CXL.io。

CXL.cache是定义主机(通常是 CPU)和设备(例如 CXL 内存模块或加速器)之间交互的协议。这允许连接的 CXL 设备以低延迟缓存主机内存。可以将其视为 GPU 直接缓存数据存储在CPU的内存中。

CXL.memory / CXL.mem是一种协议,它为主机处理器(通常是 CPU)提供使用加载/存储命令直接访问设备附加内存的功能。可以将其视为使用专用存储级内存设备或使用 GPU/加速器设备上的内存的 CPU。

要获取 CXL 上的端点,必须使用 CXL.io,但从那里我们可以拥有 CXL.io 以及 CXL.cache 和/或 CXL.mem 的三种组合中的任何一种。CXL 人员使用类型 1 (CXL.io + CXL.cache)、类型 2(全部三种)和类型 3 (CXL.io + CXL.mem) 作为示例。

类型 1 可以被视为一种加速器,如直接访问主机 CPU 内存的 NIC。类型2是我们有加速器的情况,就像带有内存的GPU一样,GPU可以访问主机内存,而主机CPU可以访问GPU内存。类型 3 人们可以将其视为一种内存模块,其主要目的是将 CXL 内存设备的介质暴露给主机 CPU。

原文链接:https://www.servethehome.com/cxl-3-1-specification-aims-for-big-topologies/