来源:内容来自半导体行业观察(ID:icbank)编译自semiengineering,谢谢。

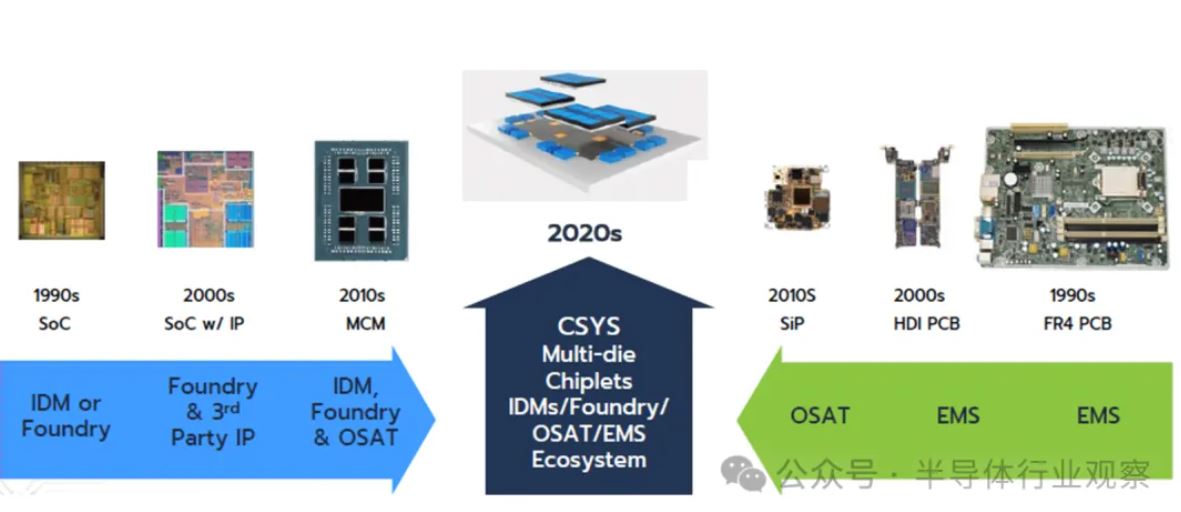

半导体行业正在准备从基于专有小芯片的系统向更加开放的小芯片生态系统迁移,其中由不同公司采用不同技术和器件节点制造的小芯片可以以可接受的良率集成在单个封装中。

为了使这项工作按预期进行,芯片行业将必须解决各种有据可查的技术和业务问题,并且必须控制一些可能发生的更宏伟的愿景——至少在最初是这样。基本挑战是将包含越来越多小芯片的终端系统的特定领域性能需求与IDM、代工厂和OSAT的组装和封装能力及方法相结合。这包括创建大致相当于工艺开发套件 (PDK) 的装配开发套件 (ADK),如今已将其编入制造规范。

PDK 提供了开发平面芯片所需的适当详细程度,将设计工具与制造工艺相结合,以实现可预测的结果。但要让该功能适用于具有异构小芯片的PDK,要复杂很多倍。设计和装配团队需要管理热、机械和电气的相互依赖性,这些依赖性会导致电气和机械应力,从而导致实际工作负载下的翘曲、良率降低和可靠性问题。除此之外,还有与不同制造商的不同设备的包装相关的业务和法律问题。

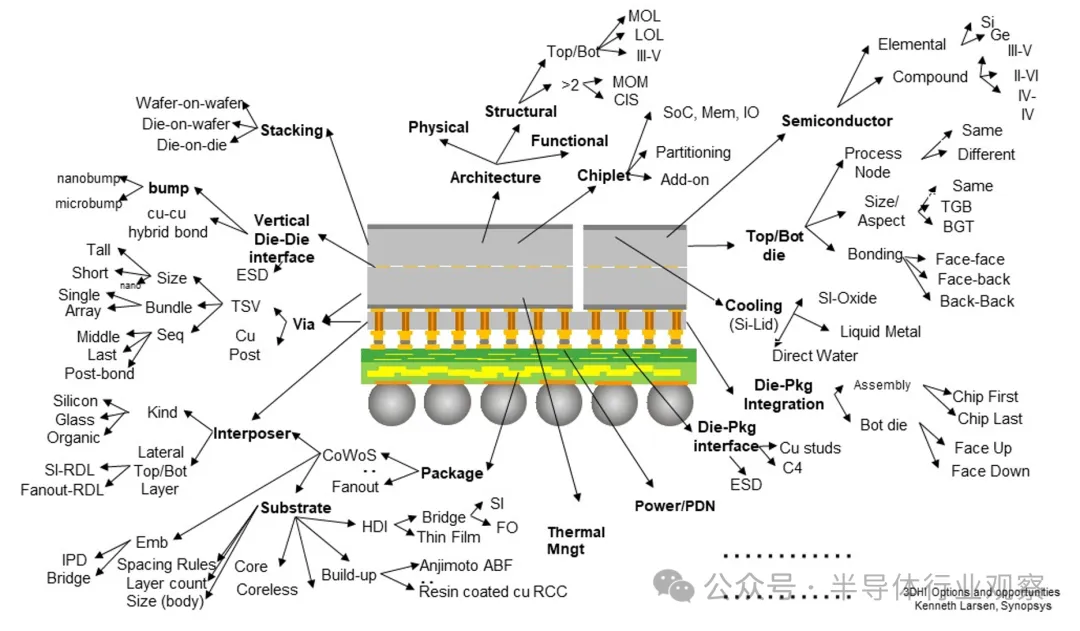

Yole Intelligence半导体封装技术和市场分析师 Gabriela Pereira 表示:“小芯片是一种不断增长的趋势,尤其是在 HPC 和网络领域,并且有潜力扩展到其他应用。” “业界已经认识到需要高端先进封装技术来连接它们 - 但这比看起来要复杂得多。连接小芯片需要在封装级设计高带宽互连,可以采用不同的形式,例如 2D、2.5D 或 3D,同时确保满足散热和功耗要求。”

基于小芯片的商业设备通常是特定于领域的,有时是针对特定工作负载而开发的。因此,尽管业界大力推动为小芯片创建类似乐高的混合搭配生态系统(目前包括多个 IP 和 EDA 供应商、代工厂、内存供应商、OSAT、基板供应商等),但要按计划进行这项工作仍需要时间和大量的工作。

在创建异构集成设计时,代工厂、IDM、OSAT 和 PCB 制造商之间必须进行更紧密的合作。由于每个基于小芯片的系统都将被定制,因此组装工艺的数量将大幅增加。例如,一家 OSAT 指出,在其约 5,000 家客户中,有约 1,000 种不同的组装工艺。

产品和工艺的多样性使得从大量选项中选择小芯片很难获得可预测的结果。

“我们已经遇到了很多限制,不仅包括芯片,还包括集成和生态系统,”日月光集团高级总监曹立红(音译)在 MEPTEC 的“Chiplet 之路”论坛上表示。她强调,客户继续推动低成本小芯片组装工艺,这在开发复杂的组装工艺与不同行业的经济现实之间造成了建设性的紧张关系。例如,汽车计算设备比数据中心具有更高的成本敏感性,但它们的芯片在更恶劣的环境中运行,使用寿命更长。

我们需要的是一套明确的装配工艺配方——基本上是一个高度有限的选择菜单——特定于最终应用(HPC、汽车、射频电信),以降低基于小芯片的系统的成本。OSAT 和代工厂已经朝着高性能计算的方向发展。例如,在 2024 年 Direct Connect 活动中,英特尔分享了其六种不同的小芯片封装工艺。台积电和三星还提供定义的小芯片工艺集。但这些装配工艺的成功需要工程团队共同优化流程、工艺和材料,以最好地满足系统要求。

“以前,当我们设计系统时,我们只需要担心系统要求。一旦我们开始分离die并重新组装它们,我们就必须开始考虑其他事情。我们必须担心将它们组合在一起,同时考虑芯片之间的信号完整性、可靠性、散热等。”应用材料公司人工智能系统解决方案总监 Itai Leshniak 在 MEPTEC 论坛上说道。“如果我们以基于人工智能的计算机视觉为例,我们可以在硬件方面将其逐层分解,确定需要哪些计算机视觉处理器、传感器、过滤器来将其分解为层架构。然后我们开始研究如何封装所有这些小芯片,然后使用哪些材料以及如何利用这些材料。”

材料和装配工艺

从概念上讲,设计工程师将使用小芯片来设计系统。然而,协同设计和集成比组装一组乐高积木要复杂得多,因为小芯片、中介层和封装基板来自不同的设计公司和制造工厂。用于连接小芯片的先进封装技术各不相同——FOWLP、FOPLP、CoWoS 等,每种技术都带来了额外的设计和材料选择以及某些工艺限制。

目前,工程团队正在确定不同封装选项之间的权衡,以选择材料、得出工艺配方并确定设计规则。

材料是一个很好的起点。“材料非常重要,因为它们能够实现新产品和封装技术,”弗劳恩霍夫可靠性和微集成 IZM 研究所副组长 Tanja Braun 说道。“当你转向更先进的封装时,流程变得更加复杂,因为你要将更多的东西放在一起。最终,这是设备、材料和工艺开发的结合。”

封装组装过程中有三个至关重要的热参数——热膨胀系数 (CTE)、玻璃化转变温度 (T g ) 和导热率。这些因素影响材料在制造到包装过程中的表现,以及它在现场的表现。

“我们的材料面临的挑战包括不同芯片的温度限制,” Brewer Science首席技术官 Rama Puligadda 说道。“我们必须确保用于粘合材料的温度不超过集成到封装中的任何芯片的热限制。此外,可能还有一些后续工艺,例如重新分布层(RDL)形成或模制。我们的材料必须能够经受住这些过程。它们必须能够经受住整个包装过程中接触到的化学品的考验。封装中的机械应力给粘合材料带来了额外的挑战。”

在具有可选中介层的基板上小芯片堆栈中,它们的材料属性也会影响相邻材料之间的热机械应力。这直接影响大面积衬底区域上的互连尺寸控制。

Promex Industries首席执行官迪克·奥特 (Dick Otte) 表示:“如果你仔细研究一下数字,你会发现所需的容忍度和控制水平令人恐惧。” “你所说的控制尺寸相当于足球场长度上草叶的宽度,所以这大约是十万分之一。”

目标是在回流焊中均匀加热结构,以获得最佳工艺结果并避免破裂。“当你让它经历 250 摄氏度的温度变化时,你需要缓慢加热,这样顶部就不会先于底部变热,”Otte 说。

多物理场理解协同优化

多物理场建模已成为协同优化包装设计和装配工艺开发的首选方法。这会影响永久和临时材料,以及处理器、存储器和其他组件的放置。

“你总是关注客户对电力的需求,因为这将有助于定义材料集。该材料集广泛适用于一系列速度范围。只要不超出这些电气规范,理论上应该没问题,” Amkor Technology高级封装和技术集成副总裁 Mike Kelly 说道。

为了节省基于经验的开发的多次迭代,工程师可以使用基于物理的模拟来了解材料组的属性对装配过程、功率/热量和机械振动的影响。

考虑到 HPC 小芯片产品在峰值性能下的功耗约为 1,000 瓦,因此需要充分了解功率和热相互作用。

“正如每个人一样,我们一直在努力应对不同技术的复杂性。它们不仅在不同的供应商之间存在差异,而且还会随着时间的推移而变化。” Ansys产品营销总监 Marc Swinnen 说道。“我们的方法是确定需要解决的要点。我们与客户共同开发了一个能够真正实现现在所需的模拟流程。”

材料只是拼图中的一小部分。“然后需要对装配应力进行建模,以了解是否可以正确组装该设备。第三个是机械振动,”Swinnen 说。“你的设备能承受这些定期振动吗?对这些属性进行建模直接与我们的机械分析工具(声学、热学、振动等)联系在一起。最后,您将必须进行物理模拟。我们正在努力让人们以多种不同的形式使用它。但我们工具产品的基础是我们拥有网格模拟和分析。问题是如何以实用且可用的方式获取正确格式的数据。”

不断发展的装配设计套件

对于传统封装,OSAT 为每种封装技术提供了设计规则。这些需要考虑电气、机械和热设计要求以及制造工艺限制。实际上,这是一个多维边界框。供应商与客户一起进行迭代,以创建产品特定的工艺配方。

规则涵盖了宏观层面的属性。“至少,您从设计规则中看到的是最大封装尺寸、最大硅尺寸以及硅是否可以[安装]在基板的两侧,这样当您遵循这些结构时,最终产品的使用寿命将是例如,1,000 次热循环,”Fraunhofer 的 Braun 说道。

此外,设计规则需要描述中介层和/或重新分布层的布线约束,例如RDL线宽和间距、球栅/柱/焊盘尺寸和间距以及互连的最大数量。

将单片 HPC 器件分解为多个芯片可将部分半导体设计/工艺复杂性转移到封装空间。这让事情变得更加复杂。考虑到连接 10 个芯片需要中介层或基板的重新分布层内有 100,000 条迹线。

为了应对芯片级的复杂性,IC 行业长期以来一直依赖工艺设计套件 (PDK) 将设计规则捕获到可导入 EDA 工具的电子文件中。其对应的装配设计套件 (ADK) 相对不成熟。

“我们称之为智能包,”Amkor 的 Kelly 说。“这是我们为每位自行设计的客户提供的 ADK。它是一组宏,以及根据客户的特定设计定制的数据库。对于chiplet来说,它是一种高密度扇出封装技术。而且它认识到金属密度和金属间距等的限制。这使我们更容易进行设计规则检查(DRC)。”

但目前,由于仍需要一定程度的定制,ADK 的派生方式及其所需内容正在不断变化。EDA 工具供应商、OSAT 和半导体器件供应商之间需要建立合作伙伴关系。

“我们来自 IC 世界,那里的一切都非常严格,” Synopsys旗下 EDA 集团 3D-IC 产品管理总监 Kenneth Larsen 说道。“在 OSAT 方面,也许这是因为它是如此定制,设计规则看起来就像一个数据表。然后,您可以随着时间的推移或与 OSAT 合作来构建和优化产品。这不是电子交换。在 IC 领域,这完全是闻所未闻的。虽然可以调整一些东西,但你有一个资格流程。而且似乎还没有这样的包装。”

材料和相关的组装配方最终决定了小芯片-基板堆叠在柱间距、RDL 线宽和间距、键合工艺以及小芯片放置公差方面的可能性。但在少数 ADK 中,有许多可能的交互需要考虑。

当前的重点是协同优化系统设计与小芯片组装工艺,从而形成组装工艺开发流程(见图 4)。该流程考虑了组装过程的定制需求,并创建了封装设计人员使用的必要设计规则。

“首先,您需要使用小芯片定义您的结构。您使用的是基板 RDL、2.5D RDL 还是桥接器?之后,您需要考虑结构的材料。您选择什么样的材料来满足您的电气性能和机械应力要求,”曹说。“之后,您进行预分析,以确保您使用的所有结构和材料在电气、翘曲和机械应力方面均可行。”

设计规划流程还包括通过协同设计签核文档评估芯片间互连。

结论

在 IDM 模型之外实现基于小芯片的设计之前,业界需要完成连接制造和设计复杂性的生态系统。这是因为需要根据材料、工艺和集成能力共同优化系统架构。虽然通过一系列定义明确的产品来推动小芯片生态系统的发展会更容易,但这还没有发生。

整个设计和制造堆栈的工程团队需要合作选择适当的材料、架构、工艺等,以开发最终的可设计的基于小芯片的产品。正如日月光集团的曹指出的那样,“集成的设计和制造生态系统非常重要。IDM、供应商、材料供应商之间的合作非常重要。每个人都需要共同努力才能真正实现实际应用程序的集成。”