作者:FPGA入门到精通

FPGA约束文件是FPGA设计中不可或缺的一部分,它们用于指导综合和布局布线工具如何处理设计。

约束文件确保了设计满足所有的时序、管脚和区域要求,从而使得设计能够在特定的FPGA硬件上正常运行。

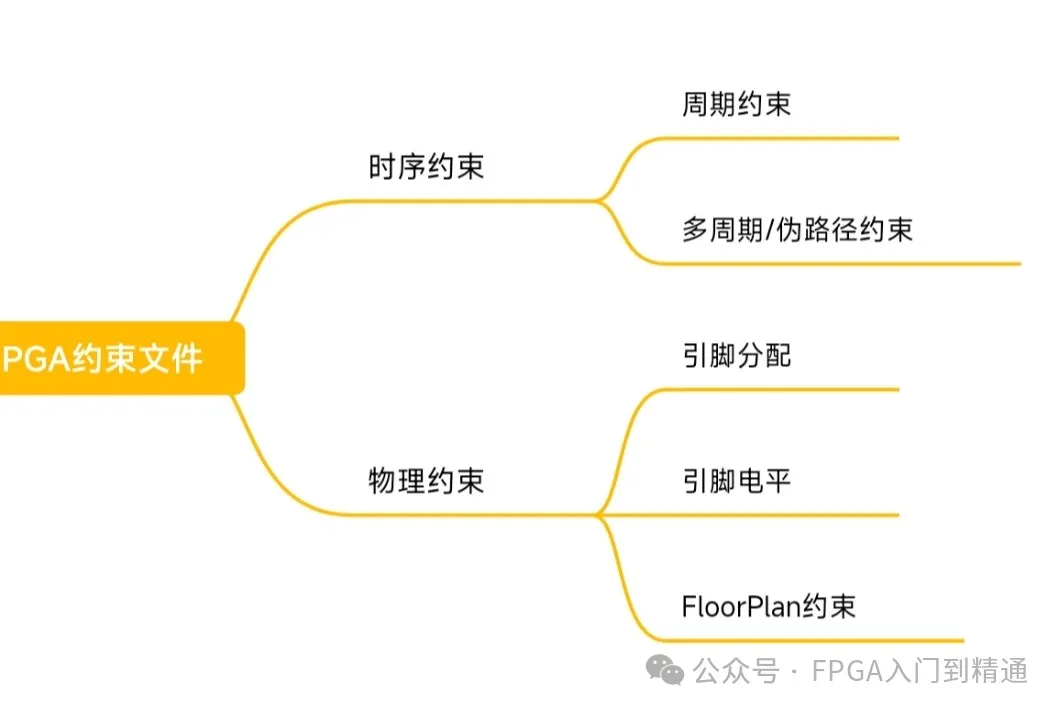

一、约束文件的类型

FPGA中有多种约束文件,主要可以分为时序约束和物理约束。一般建议将这两种约束分成两个文件。

Xilinx vivado的约束文件通常采用.xdc扩展名。

Xilinx一般建议将这两类约束分开写在不同的约束文件中,可以分别命名为timing.xdc和pin.xdc。

1、时序约束

用于定义设计中的时钟、数据路径和延迟要求。它们确保数据在逻辑门之间正确传输,避免时序错误。

2、物理约束

物理约束涉及FPGA的具体布局和布线,包括引脚分配、I/O标准和引脚电压等。

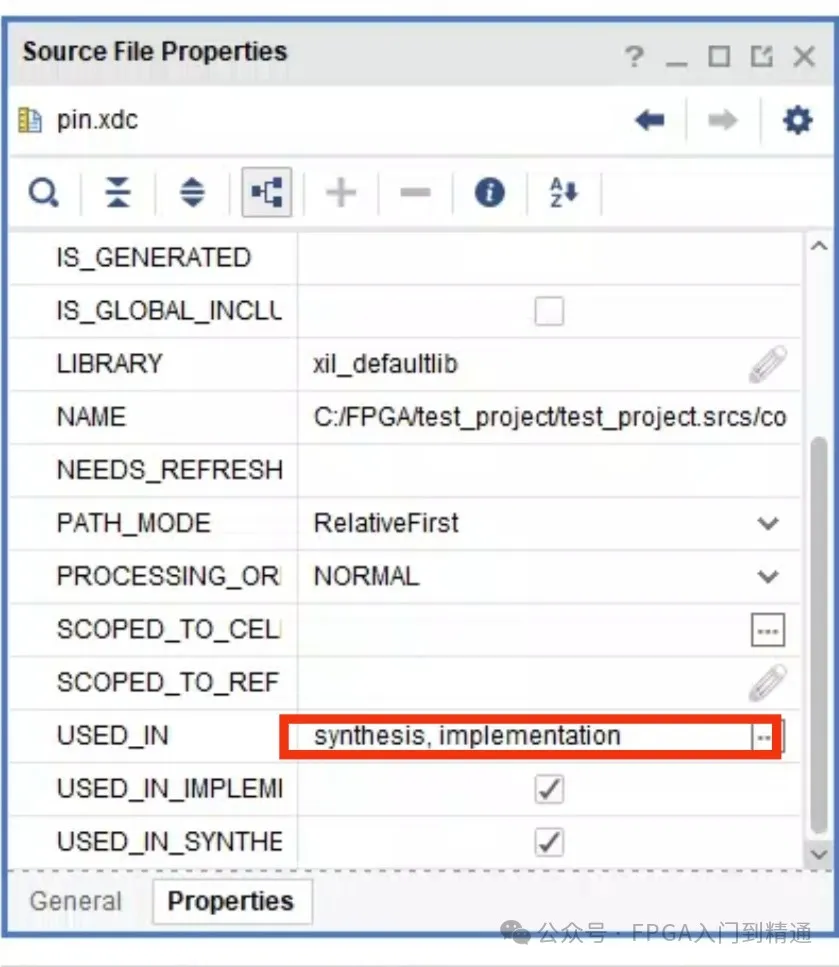

二、如何设置约束文件在不同步骤下生效?

通过设置不同约束文件在不同阶段下生效,可以控制当前工程,满足不同的时序要求。

约束文件可以在属性窗口中查看,也可以通过Tcl脚本在Vivado Tcl Console中查看,TCL命令如下:

report_property [get_files *timing.xdc] Lauren的FPGA

1、属性【USED IN】

通过属性窗口【USED IN】,控制文件在不同阶段是否生效,上图中的属性窗口中{synthesis, implementation},表示这个约束文件在综合和实现阶段均有效。

USED_IN_IMPLEMENTATION属性值为1时,表示当前文件在不限实现阶段生效。

USED_IN_SYNTHESIS属性值为1时,表示表示当前文件在不限实现阶段生效。

2、属性【IS_ENABLED】

用于管理当前约束文件是否使用,可以控制多个约束文件的生效状态。

3、多个Design Runs

vivado可以创建多个不同的Design Run,也可以使用不同的约束设置和约束文件。