来源: FPGA技术实战

I2C,通常被称为I'two'C,代表集成电路间协议。I2C由飞利浦半导体公司(现为恩智浦半导体公司)于1982年开发,是一种低速通信协议,用于连接微控制器和处理器等控制器设备与数据转换器和其他外围设备等目标设备。

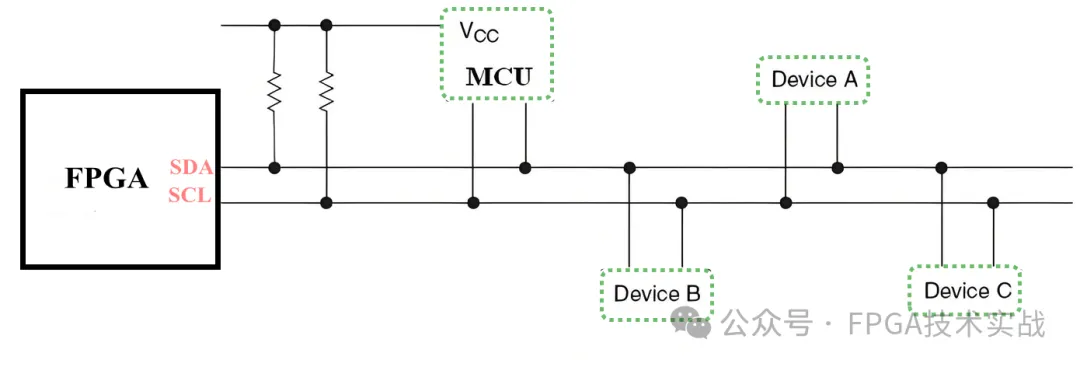

由于该协议只需要两条通信线路,I2C在很多工程中有广泛的应用,如数据采集领域的串行ADC、DAC、摄像头配置,X射线管配置等。除此之外,由于I2C协议占用引脚特别少,硬件实现简单,可扩展型强,现在被广泛地使用在系统内多个集成电路(IC)间的通信。

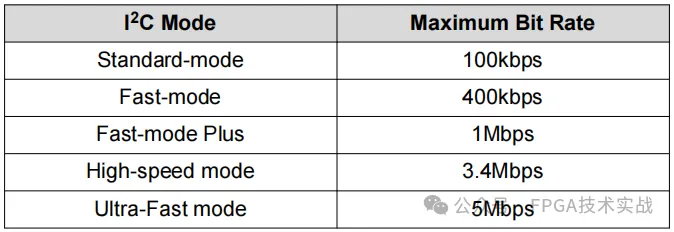

I2C还具有用于更高数据速率的另外两种模式。高速模式(Hs模式)和超快模式(UFm)是最快的操作模式。表1-1显示了不同的I2C模式及其各自的数据速率。

表1:不同I2C模式的最大传输速率

2. 物理层

2.1 2线通信

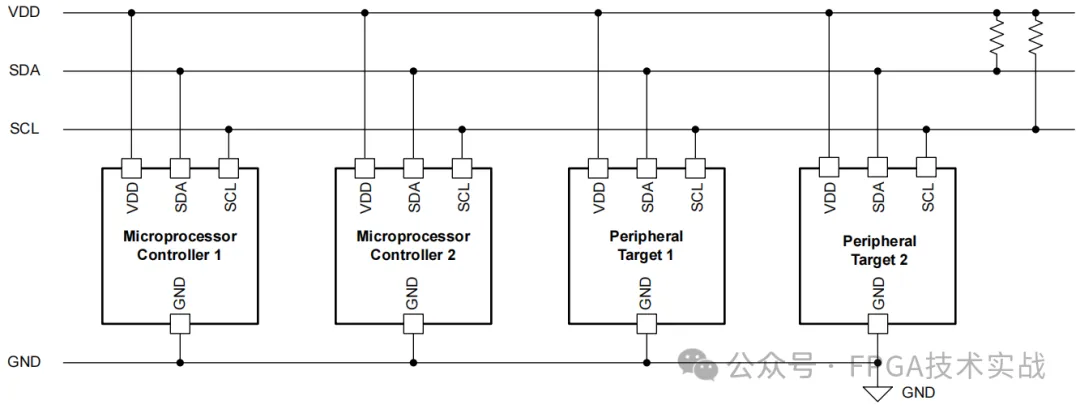

第一条线是SCL,它是主要由控制器设备控制的串行时钟。SCL用于将数据同步地时钟输入或输出目标设备。

第二条线是SDA,它是串行数据线。SDA用于将数据传输到目标设备或从目标设备传输数据。

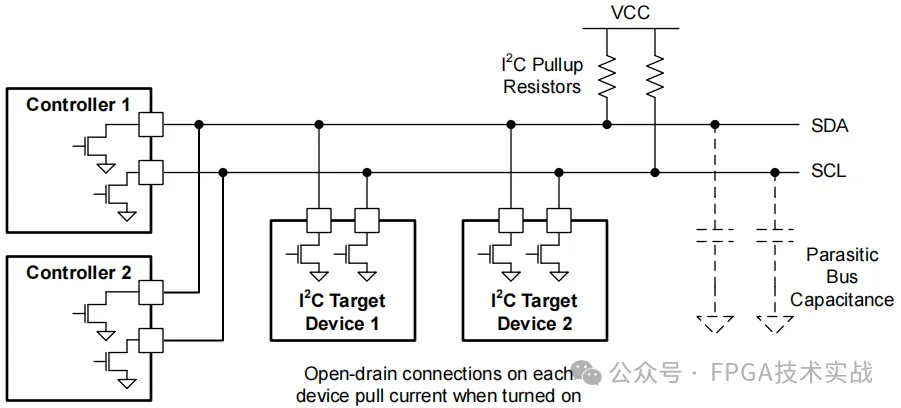

I2C控制器设备启动和停止通信,这消除了总线争用的潜在问题。通过总线上的唯一地址发送与目标设备的通信。这允许I2C总线上的多个控制器和多个目标设备。

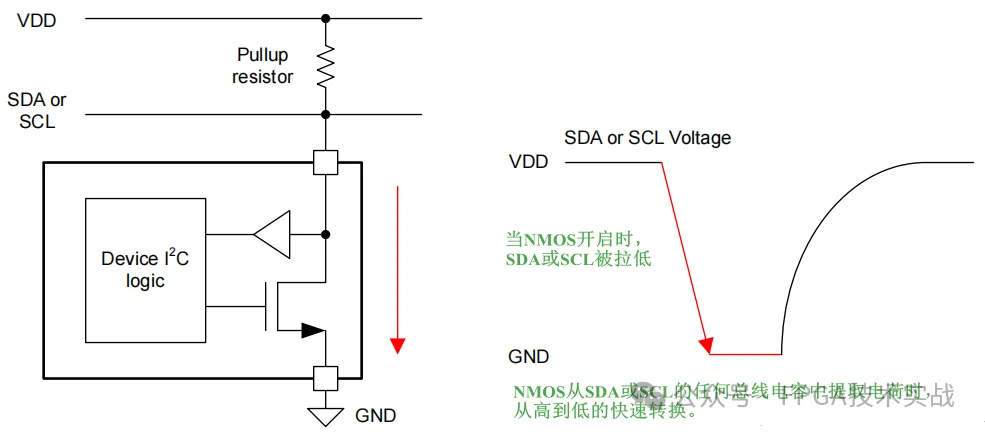

2.2 漏极开路连接

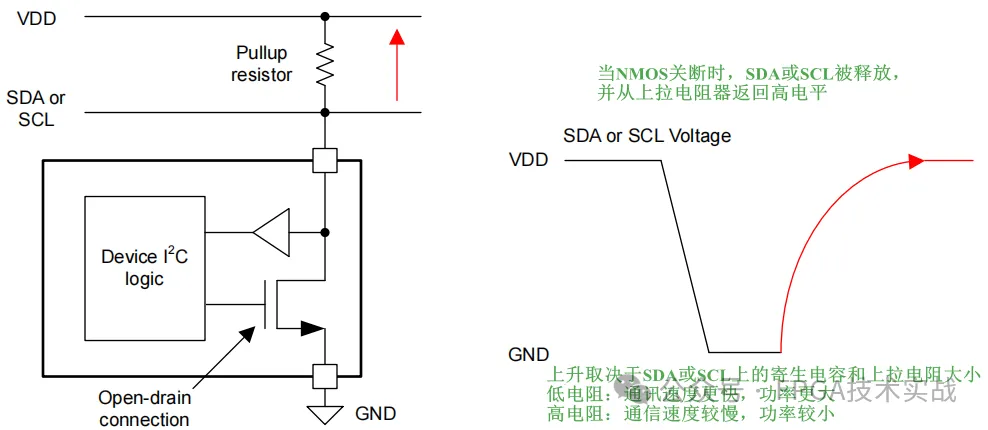

漏极开路连接用于SDA和SCL线路,并连接到NMOS晶体管。该漏极开路连接控制I2C通信线路并将线路拉低或释放线路高。漏极开路指的是NMOS关闭时的NMOS总线连接。图3显示了NMOS打开时的漏极开路连接。

要设置SDA或SCL线的电压电平,需将NMOS设置为打开或关闭。当NMOS打开时,设备通过电阻器将电流拉到地。这将打开的NMOS拉低。通常,当NMOS在SDA或SCL上下拉时,I2C从高到低的转变是快速转变。转变的速度由NMOS驱动强度和SDA或SCL上的任何总线电容决定。

当NMOS关闭时,器件停止拉电流,上拉电阻器将SDA或SCL线拉至VDD。图2-3显示了NMOS关闭时漏极开路。上拉电阻器将线路拉高。开路漏极线的转变较慢,因为线是相对于总线电容上拉的,并且不是主动驱动的。

通过控制该漏极开路连接,SDA和SCL都可以设置为高电平和低电平,从而实现I2C通信。

由于I2C通信线路上的电容,SDA和SCL线路以指数稳定RC时间常数放电,这取决于上拉电阻器的大小和I2C总线上的电容。更高的电容限制了I2C通信的速度、设备的数量以及总线上设备之间的物理距离。较小的上拉电阻器具有更快的上升时间,但需要更多的功率用于通信。较大的上拉电阻器具有较慢的上升时间,导致较慢的通信,但需要较少的功率。

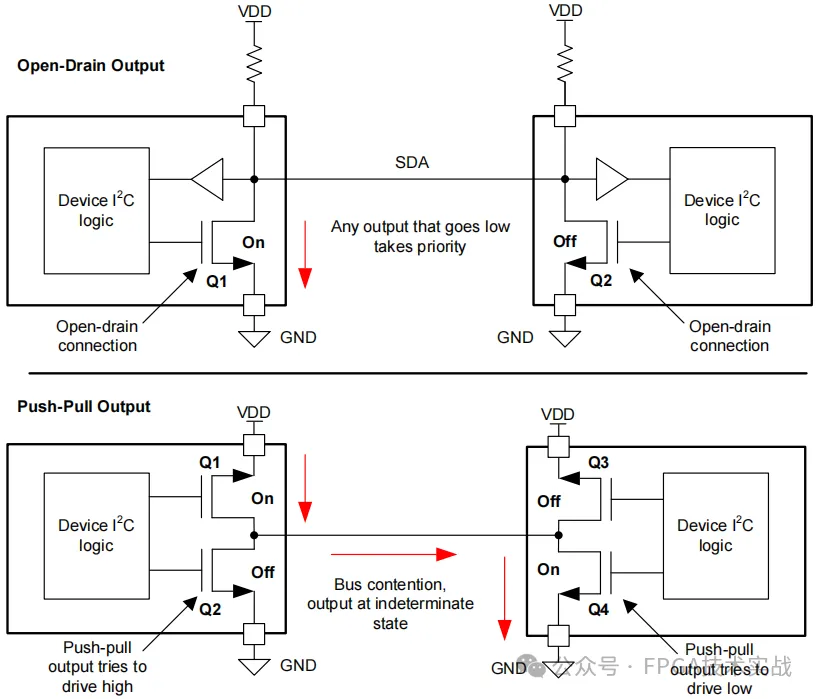

使用开放漏极的I2C的好处之一是总线争用不会使总线进入破坏状态。通过开漏输出,许多设备可以连接在一起,而不会发生破坏性争用。对于该连接上的任何输出,如果任何输出将线路拉低,则线路为低。这种连接被称为有线AND连接。当连接在一起时,输出是所有输出的逻辑AND。

图5:推挽式与开漏输出的比较

如果输出是推挽式的,那么在没有破坏状态的可能性的情况下,输出就不能连接在一起。推挽输出(通常用于SPI通信)具有互补的NMOS和PMOS晶体管,它们驱动输出为高或低。图5显示了在争用中开漏和推挽输出之间的比较。

采用开放式漏极连接,任何设备都可以随时将连接拉低。每当任何设备将线路拉低时,线路都会显示为低电平,但不会显示为破坏性争用。

在推挽输出中,输出也被连接在一起。如果总线上有两个设备处于活动状态,并且一个输出为高,另一个输出低,则此总线争用具有未确定的状态,可能在中间供电点处解决。此外,一个器件具有NMOS导通电流,而另一个器件则具有PMOS导通电流。这些器件通过非常低的阻抗路径将电流从VDD供应到GND,传导晶体管允许的尽可能多的电流。这种争用的结果可能是大量的电流,可能会损坏设备。

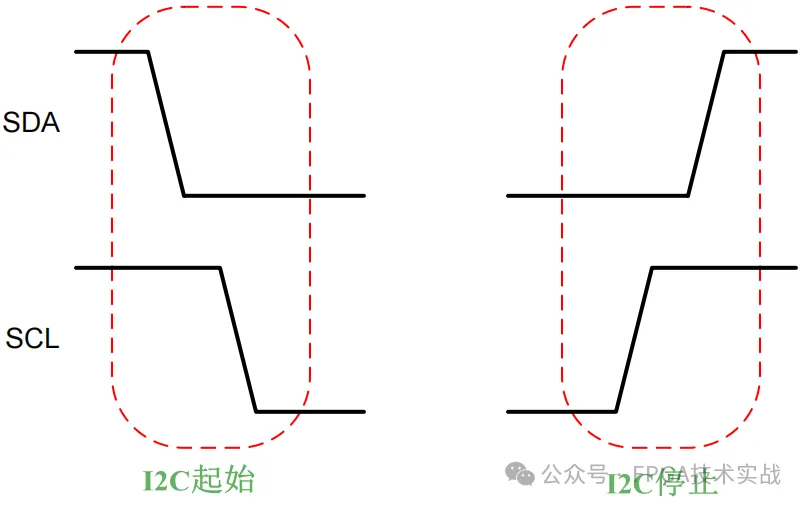

I2C通信是在I2C启动条件下从控制器设备启动的。如果总线开路,I2C控制器通过发送I2C START来请求总线进行通信。为此,控制器设备首先将SDA拉低,然后将SCL拉低。此序列表示控制器设备正在请求I2C总线进行通信,从而迫使总线上的其他控制器设备保持其通信。

当控制器设备已经完成通信时,SCL释放高电平,然后SDA释放高电平。这表示I2C停机状态。这释放了总线以允许其他控制器通信或允许同一控制器与另一设备通信。图6显示了I2C启动和停止的协议。

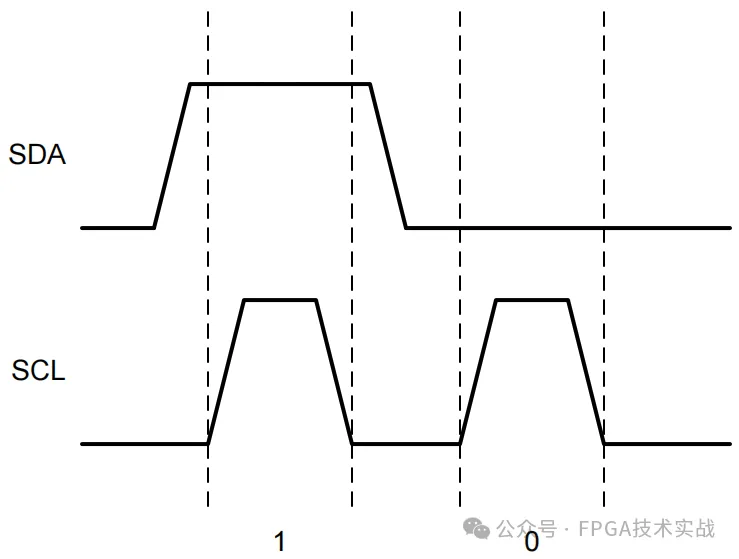

I2C使用1和0的序列进行串行通信。SDA用于数据位,而SCL是对位序列进行计时的串行时钟。当SDA释放线路时,发送一个逻辑1,允许上拉电阻器将线路拉至高电平。当SDA在线路上下拉时,将发送一个逻辑零,在接地附近设置一个低电平。图7显示了I2C通信的数字1和0的表示。

当SCL被脉冲化时,1和0被接收。对于有效位,SDA不会在该位的SCK的上升沿和下降沿之间变化。SDA在SCL的上升沿与下降沿之间的变化可以解释为I2C总线上的START或STOP条件。

I2C协议被分解为多个帧。通信开始于控制器设备在START之后发送地址帧。地址帧后面跟着一个或多个数据帧,每个数据帧由一个字节组成。每个帧还具有一个确认比特(ACK),以提醒控制器目标设备或控制器设备已经接收到通信。图8显示了两个I2C通信帧的示意图。

在地址帧的开始,控制器设备启动START条件。控制器设备首先将SDA拉低,然后将SCL拉低用于START。这允许控制器设备在没有来自总线上的其他控制器设备的争用的情况下请求总线。每个I2C目标设备都具有相关联的I2C地址。当开始与特定目标设备通信时,控制器使用目标设备地址在I2C帧中发送或接收数据。I2C地址由I2C总线上的7个位和R/Wn组成,每个设备在总线上都有一个唯一的地址。

7位地址意味着128个唯一地址。然而,有几个保留的I2C地址限制了可能的设备的数量。发送地址时,SDA作为数据,SCL作为串行时钟。

该帧地址后面的第8位是读写(R/W)位。如果该位为1,则控制器要求从目标设备读取数据。如果该位为0,则控制器要求将数据写入目标设备。

在任何通信字节之后,额外的第9位用于验证通信是否成功。在地址字节通信结束时,目标设备在SCL脉冲期间下拉SDA,以向控制器指示地址已被接收。这被称为确认(ACK)比特。如果该比特为高,则没有目标设备接收到该地址,并且通信不成功。如果比特是高的,这被称为NACK,并且没有ACK。

地址帧后面跟着一个或多个数据帧。这些帧一次发送一个字节。在每个数据字节被传输之后,会有另一个ACK。如果数据字节是对设备的写入,则目标设备将SDA拉低以确认传输。如果数据字节是从设备读取的,则控制器将SDA拉低以确认数据已被接收。ACK是一个有用的调试工具。该位的缺失可以指示目标外围设备没有接收到用于通信的适当I2C地址,或者控制器外围设备没有收到期望的数据。

通信完成后,控制器发出I2C STOP条件。首先释放SCL,然后释放SDA。控制器使用STOP指示通信已完成,I2C总线已释放。

这是控制器设备和目标设备之间的任何I2C通信的基本协议。通信可以由多个字节的数据组成。在目标设备具有多个数据和配置寄存器的某些情况下,从设备的读取可以从对设备的写入开始,以指示要读取哪个寄存器。

4.1 电压电平转换

设计大型系统的一个常见问题是系统内不同电压电平的混合。这些不同的电压可以为不同的I2C控制器和目标设备供电。电源中不匹配的电压可能会中断通信,甚至损坏设备。

对于不匹配的电源电压,最好的选择是使用特殊设备桥接两个电源电压。图9显示了使用I2C电压电平转换器桥接两个不同电源电压之间通信的示例。有两组上拉,每个电压电平一组。作为一个通用的电压转换器,PCA9306允许不同电源电平之间的通信。

为了设计系统,使总线速度足够快,以满足协议总线速度,本节介绍如何计算上拉电阻的值。

对于SDA和SCL的漏极开路连接,从这些线路从高到低以及从低到高的转换取决于器件漏极开路的电流吸收、总线电容和上拉电阻值。基于这些不同的参数,可以计算I2C总线速度的最小和最大电阻。

推荐的正常上拉电阻为1kΩ至10kΩ。电阻越高,I2C通信越慢。由于电阻较低,I2C通信需要更多的功率。基于几个不同的参数,可以计算I2C总线速度的最小和最大电阻。

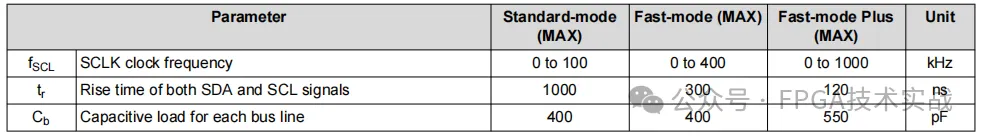

表2:I2C总线参数特性

除了这些参数外,还考虑了I2C输入和输出电压的最小值和最大值。表3描述了这些电压。

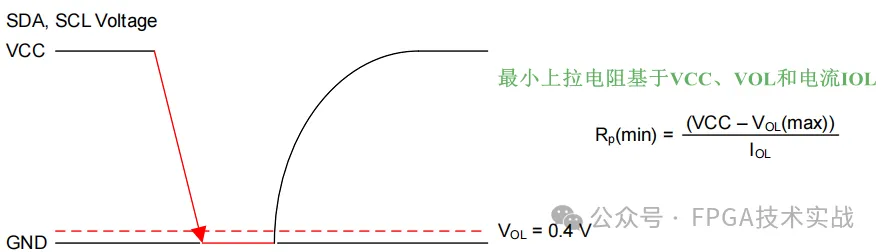

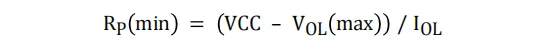

当设备释放SDA或SCL时,总线连接到VCC电压。当激活时,器件漏极将总线输出拉到接近接地的位置。输出必须下降到输出低电平电压VOL。该设备用电流IOL将总线拉低。VOL和IOL(3mA电流汇点)如表3所示。根据该电流,计算上拉所需的最小电阻。如果电阻较小,则输出电流不能将总线的输出电压拉低到足以被识别为数字低。这如下公式所示。

求出最小上拉电阻,从3.3 V的电源电压中减去0.4 V的输出低电压。然后除以3 mA的总线所拉的电流。这导致最小电阻为967Ω。

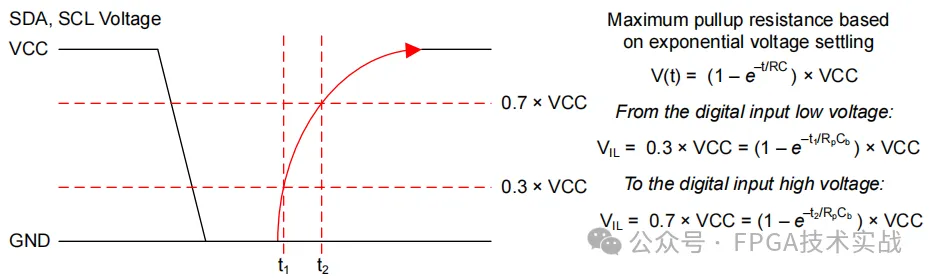

随时间的指数方程如下公式所示:

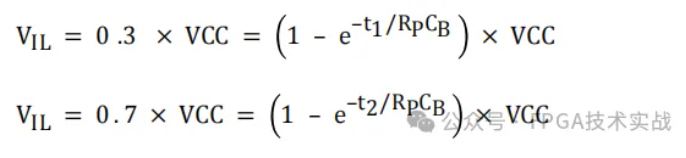

上升时间基于从电源电压的0.3倍的数字输入低电压(VIL)到电源电压的0.7倍的数字输出高电压(VIH)的转变。上升时间如表2所示,而VIL和VIH如表3所示。

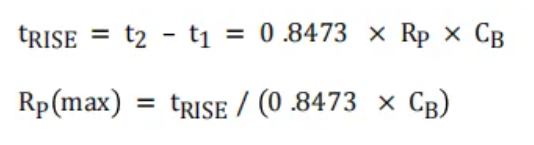

根据上述方程,可以根据最大上拉电阻和总线电容来求解上升时间。在这个例子中,计算是针对400pF的总线电容(针对最大总线电容)和3.3V的电源电压。根据上升时间,然后求解最大上拉电阻。

上升时间取决于I2C模式。对于此示例,可以使用标准模式。取1000ns的上升时间,除以0.8473乘以400pF的量。这给出了2.95kΩ的最大电阻。

最小电阻为967Ω,最大电阻为2.95kΩ,这些值的电阻范围似乎很窄。然而,这个小范围是因为上拉电阻器的大小是在最大标准模式总线电容为400pF的情况下计算的。总线电容量异常大,尤其是对于板上的寄生电容而言。如果设计具有较低的总线电容(很可能),则可以增加最大电阻,从而减少I2C总线上的功耗。

I2C是一种常见的通信协议,本文对I2C协议的历史、速度模式、物理层、数据帧结构以及混合电压系统中电平兼容性以及上拉电阻大小计算均进行了详细介绍,后续将基于本文I2C理论知识学习,利用FPGA实现EEPROM器件I2C接口驱动设计,敬请关注。