来源:内容来自半导体行业观察(ID:icbank)综合,谢谢。

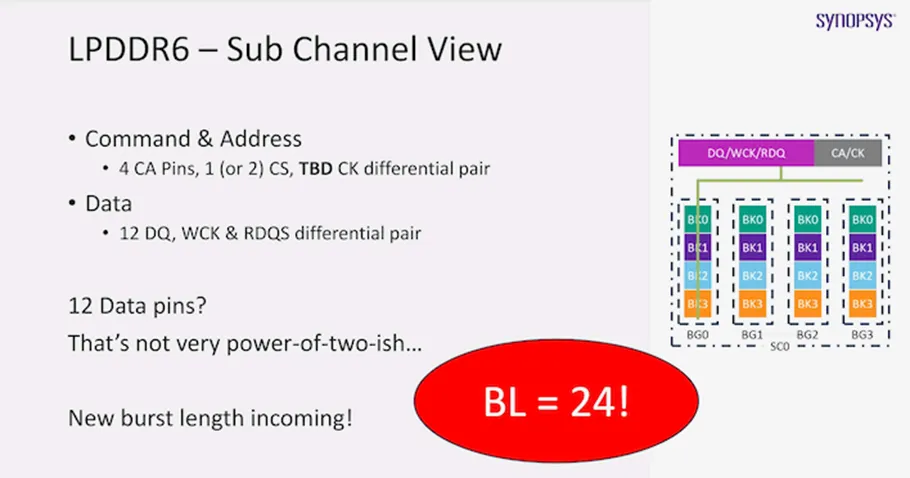

微电子行业标准制定领域的全球领导者JEDEC 固态技术协会自豪地宣布即将推出先进内存模块标准,旨在为下一代高性能计算和人工智能应用提供支持。JEDEC 今天公布了即将推出的 DDR5 多路复用列双列直插式内存模块 (MRDIMM) 和下一代 LPDDR6 压缩连接内存模块 (CAMM) 标准的关键细节。新的 MRDIMM 和 LPDDR6 CAMM 将以无与伦比的带宽和内存容量彻底改变行业。 DDR5 MRDIMM 提供创新、高效的新模块设计,以提高数据传输速率和整体系统性能。多路复用允许将多个数据信号组合并通过单个通道传输,从而有效地增加带宽而无需额外的物理连接,并提供无缝带宽升级,使应用程序能够超过 DDR5 RDIMM 数据速率。其他计划中的功能包括: 平台与 RDIMM 兼容,可实现灵活的最终用户带宽配置; 利用标准 DDR5 DIMM 组件(包括 DRAM、DIMM 外形尺寸和引脚分布、SPD、PMIC 和 TS)以方便采用; 利用 RCD/DB 逻辑处理能力实现高效的 I/O 扩展; 利用现有的 LRDIMM 生态系统进行设计和测试基础设施; 支持多代扩展到 DDR5-EOL; JEDEC MRDIMM 标准旨在提供高达原生 DRAM 两倍的峰值带宽,使应用程序能够超越当前数据速率并实现新的性能水平。它保持与 JEDEC RDIMM 相同的容量、可靠性、可用性、可维护性 (RAS) 特性。该委员会的目标是将带宽提高一倍至 12.8 Gbps 并提高引脚速度。MRDIMM 预计将支持两个以上的等级,并正在设计为使用标准 DDR5 DIMM 组件,以确保与传统 RDIMM 系统兼容。 目前正在计划采用高 MRDIMM 外形尺寸,以提供更高的带宽和容量,而无需更改 DRAM 封装。这种创新的、更高的外形尺寸将使 DIMM 上安装的 DRAM 单芯片封装数量增加一倍,而无需 3DS 封装。 作为 JEDEC 的 JESD318 CAMM2 内存模块标准的后续,JC-45 正在开发用于 LPDDR6 的下一代 CAMM 模块,目标是最大速度超过 14.4 GT/s。按照计划,该模块还将提供 24 位子通道、48 位通道和连接器阵列。

DDR6和LPDDR6的展望

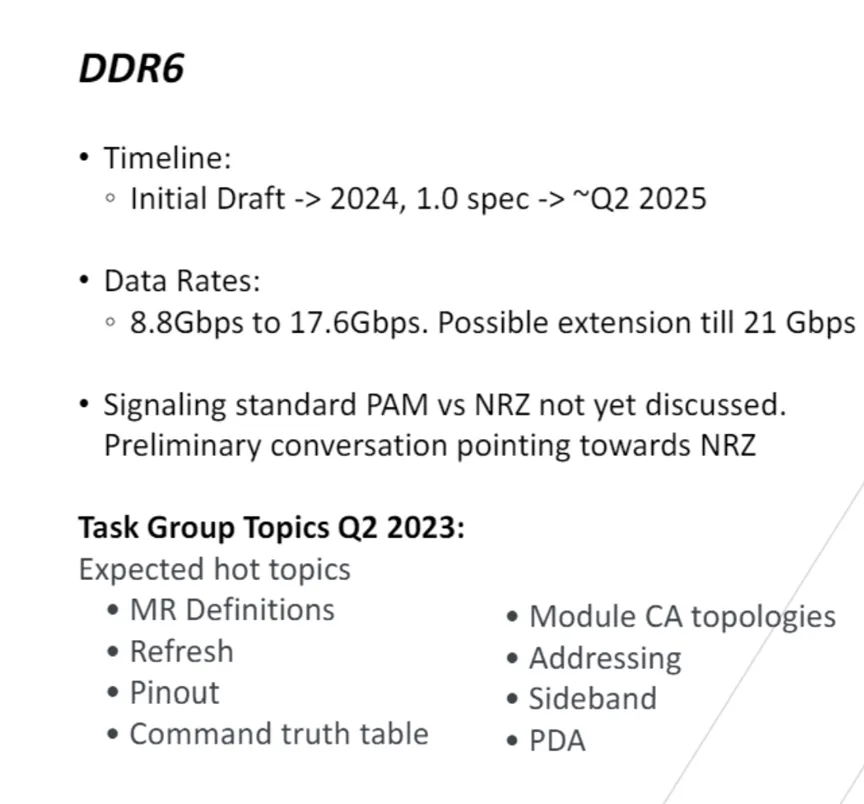

向 DDR5 的过渡早在 2021 年就开始了,但从 DDR4 到 DDR5 的转变仍在进行中,每天都有许多新的基于 DDR4 的系统出货。但根据 @DarkMontTech发布的幻灯片,业界已经开始开发 DDR6,即下一代主流 DRAM 标准,它可能会比我们预期的更早到来。不过,我们对此有合理的怀疑,所以一定要谨慎对待。

该幻灯片的来源未知,但它表明 DDR6 的数据传输速率将比 DDR5 有显著提高,据称起始速率为 8.8 GT/s,最高可达 17.6 GT/s。这些速率还有可能进一步提高,最高可达 21 GT/s。

不幸的是,幻灯片中没有描述如何实现这些传输速率,因为现在甚至连信令标准(PAM 与 NRZ)都还没有决定,但初步讨论表明更倾向于 NRZ,而这对于 17.6 GT/s – 21 GT/s 来说似乎太高了。

据报道,截至 2023 年第二季度,任务组已成立,重点关注 DDR6 开发所必需的几个关键方面。这些包括定义模式寄存器参数、刷新机制、引脚配置和创建命令真值表。此外,任务组还探索了模块命令/地址拓扑和寻址方案(命令和地址信号在内存模块内的路由设计和安排,这会影响性能、信号完整性和功耗),这对于内存模块的物理和逻辑组织至关重要。其他重要的讨论主题包括边带信令和封装后 (PDA) 修复。边带信令处理额外的数据路径以改善通信,而 PDA 则专注于修复机制以增强内存模块的耐用性和使用寿命。这些领域中的每一个对于确保 DDR6 内存的可靠性和效率都至关重要。

目前尚不清楚开发 DDR6 的任务组是否已完成工作。不过,幻灯片非常清楚地概述了 DDR6 内存的开发时间表:初始草案预计将于 2024 年准备就绪。此后,1.0 规范预计将于 2025 年第二季度左右完成。

幻灯片并未透露作者预计何时开始向 DDR5 过渡,但向 DDR5 的过渡始于 2021 年,即标准最终规范发布后约一年。假设 DDR6 规范将于 2025 年第二季度最终确定,则向该技术的过渡可能最早在 2026 年下半年开始。然而,这可能有点太早了,因为在未来几年,AMD 和英特尔都计划为其服务器平台采用相当复杂的 MRDIMM 和 MCRDIMM DDR5 内存,而且他们今年不需要下一代 DRAM。

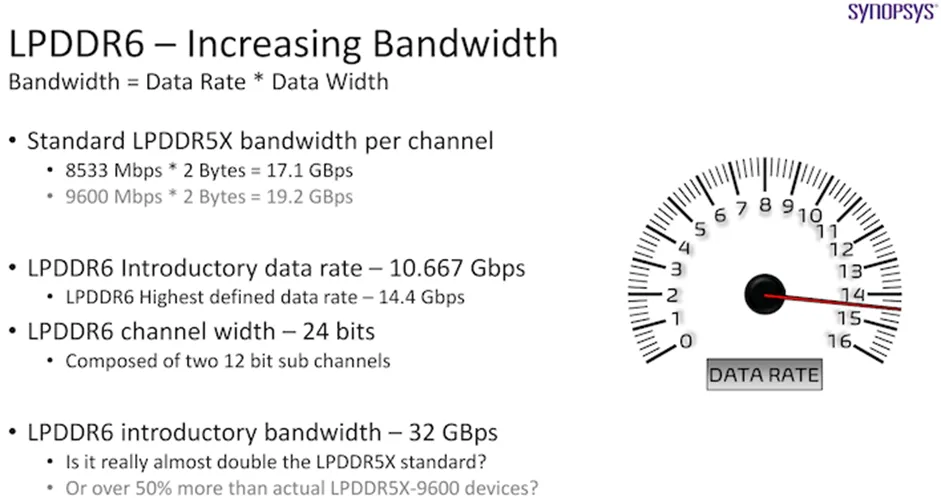

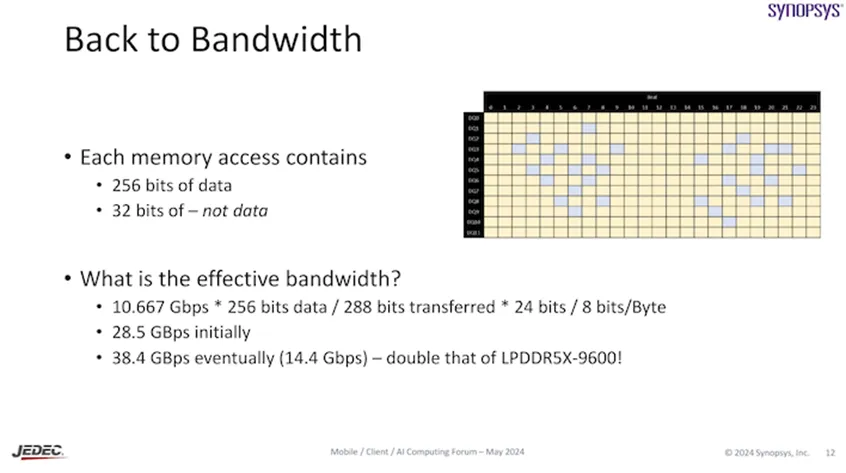

同时,该组织还设定了 LPDDR6 变体的速度,这次范围从 10.667Gbps 到 14.4Gbps。作为参考,这比三星尚未发布的 10.7Gbps LPDDR5X 内存更快。LPDDR6 还将使用由两个 12 位子通道组成的 24 位宽通道。

从现在的情况开始可能听起来并不那么令人印象深刻,但请记住,通常一种新的内存技术的起步速度实际上远远落后于当前技术最快的内存速度。最早的 DDR3 内存支持 800 MT/s 的传输速率,而发烧友可用的 DDR2 内存时钟频率为 1333 甚至 1600。同样,当 DDR4 首次亮相时,它是缓慢的 DDR4-1866,而 DDR3 已经达到 2133、2400 甚至更高的速度一段时间了。

也就是说,最初的 LPDDR6 能够超越目前可用的 LPDDR5 内存确实非常令人印象深刻。不过,这里除了更高的时钟之外,还有更多的事情要做。在 Darkmont(Xwitter 上的 @DarkmontTech)分享的文档中,LPDDR6 内存似乎使用 24 位数据通道,而不是普通 LPDDR5 使用的 16 位通道。这是因为它使用 12 条数据线而不是 8 条,从而产生新的 24 位突发长度。

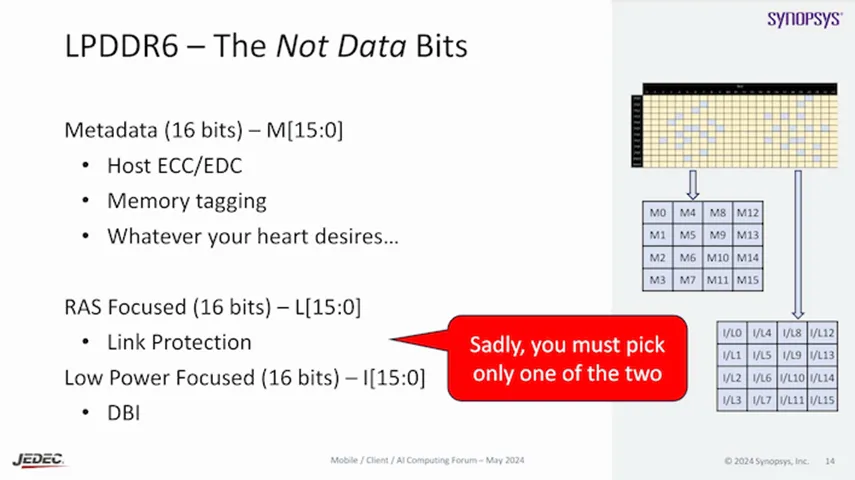

结果是,与 LPDDR5 相比,LPDDR6 的实际带宽在每个时钟周期内增加了约 33%,即使考虑到单次内存访问中 288 位中只有 256 位是实际可用数据。其他 32 位可用于特殊功能,这些功能要么通过检查和报告写入错误来提高 RAM 的可靠性,要么进行数据总线反转 (DBI),从而节省大量写入功耗。

由于带宽增加,10.667 Gbps 每针数据速率相当于单个 LPDDR6 IC 的内存带宽约为 28.5 GB/秒。如果我们谈论典型的台式电脑的“双通道”内存接口,我们会看到 228 GB/秒的内存带宽。相比之下,使用 DDR5-6400 内存的 PC 的内存带宽仅为 102.4 GB/秒。简而言之,一旦达到 LPDDR6,它看起来将使可用的系统内存带宽大致翻倍。

但是普通的旧台式机 DDR6 呢?它的规格尚未最终确定,但 JEDEC 的文件表明,可插拔 RAM 的数据速率可能从 8.8 Gbps 开始,然后一路扩展到 17.6 Gbps,甚至可能高达 21 Gbps。JEDEC 的说明表明,DDR6 的草案规格应于今年发布,然后该规格应于 2025 年第二季度最终确定。

参考链接

https://www.design-reuse.com/news/56550/jedec-ddr5-mrdimm-lpddr6-camm-standards.html