作者:Ramsey Wang,文章来源:易灵思FPGA技术交流

有客户认为Ti60F100内部flash容量比较小,只有16Mb,需要外挂flash.这里我们提供了内部flash和外部flash分别操作的方案。

该程序是通过SOC操作4线的外部flash和内部flash.程序先经过外部flash的擦除,写入和读出操作,再经过外部flash的擦除,写入和读出操作,每次读出后会进行数据的比较以判断写入和读出的数据是否一致。

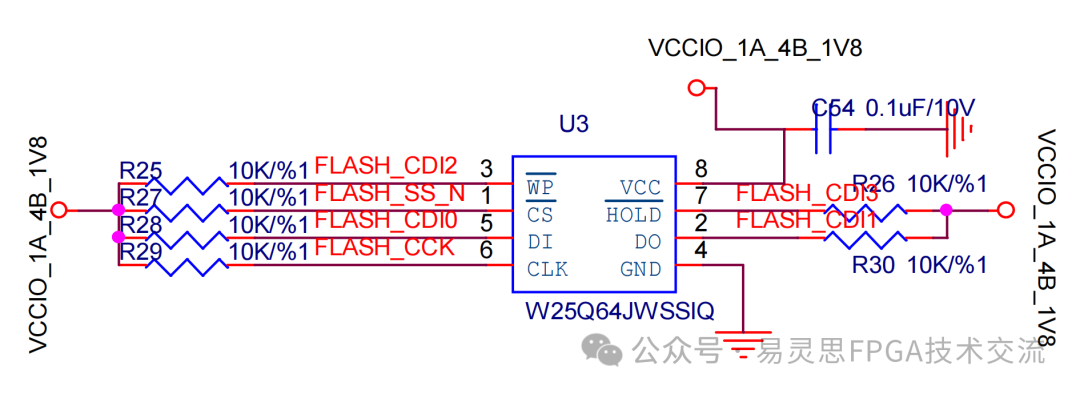

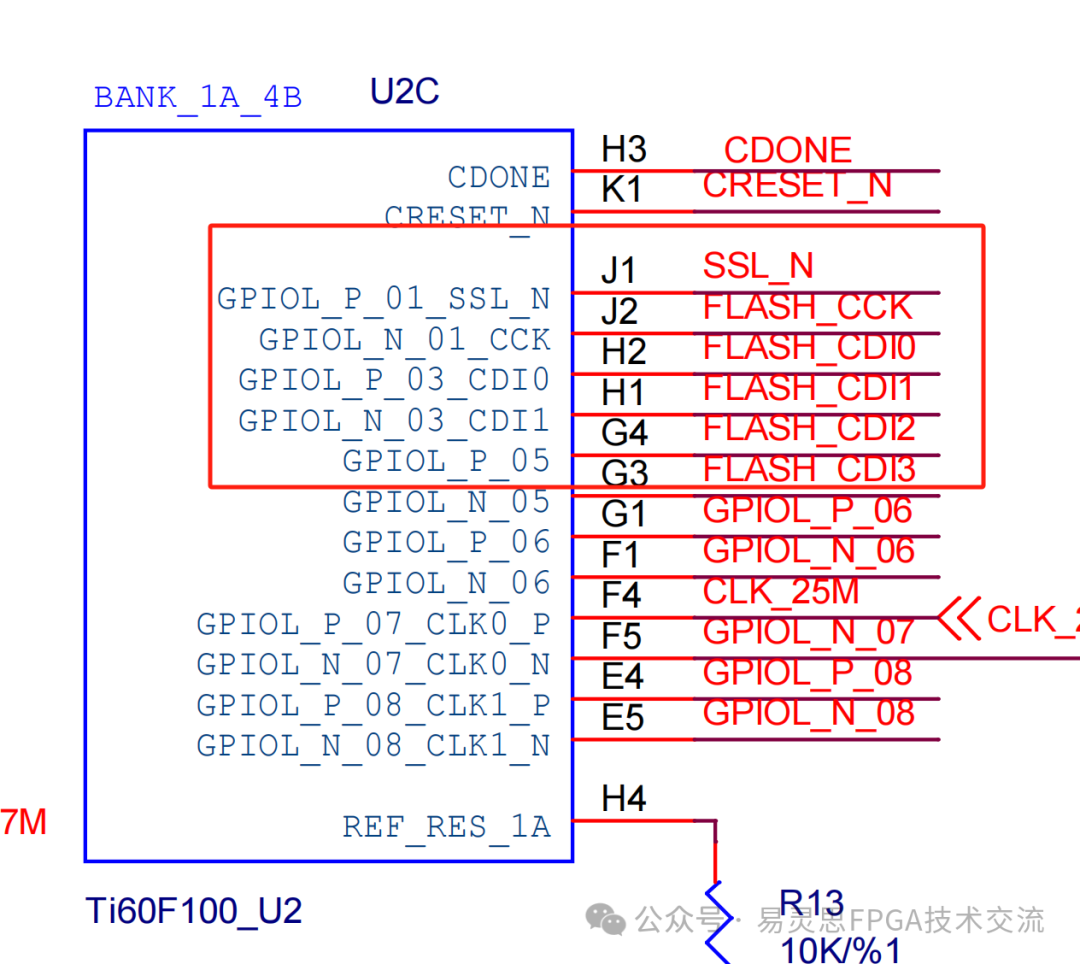

硬件方案如下:

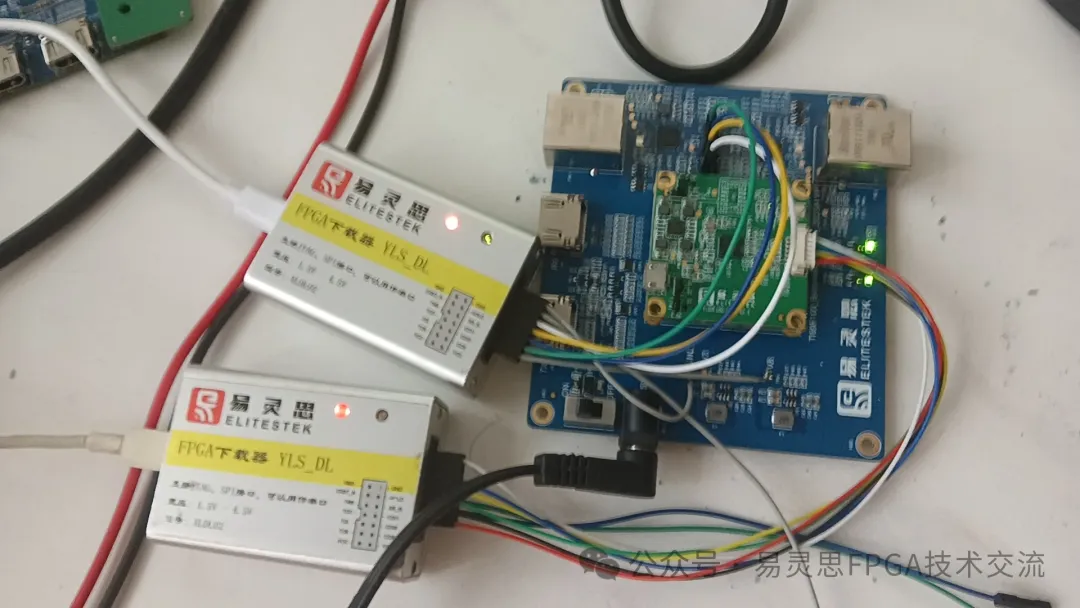

由于使用的RSICV是softjtag操作,所以使用了两个下载器。在硬件设计外外挂一片64Mb的flash。

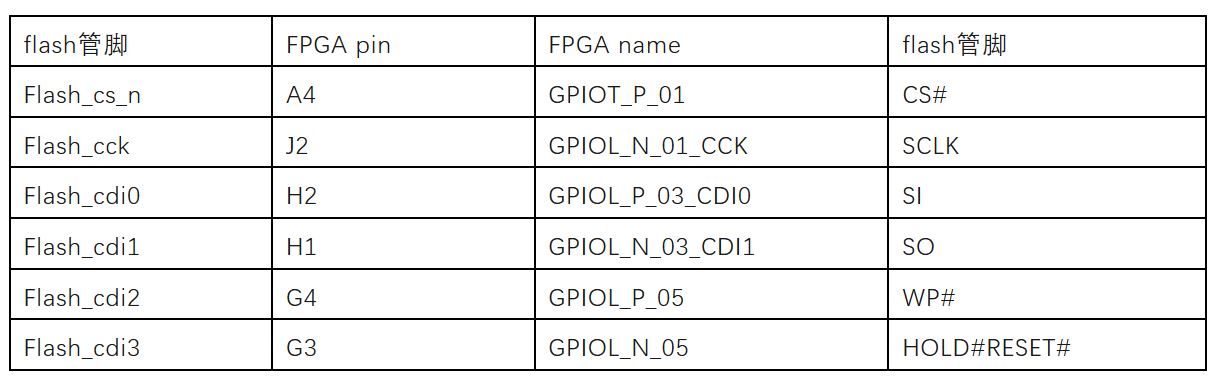

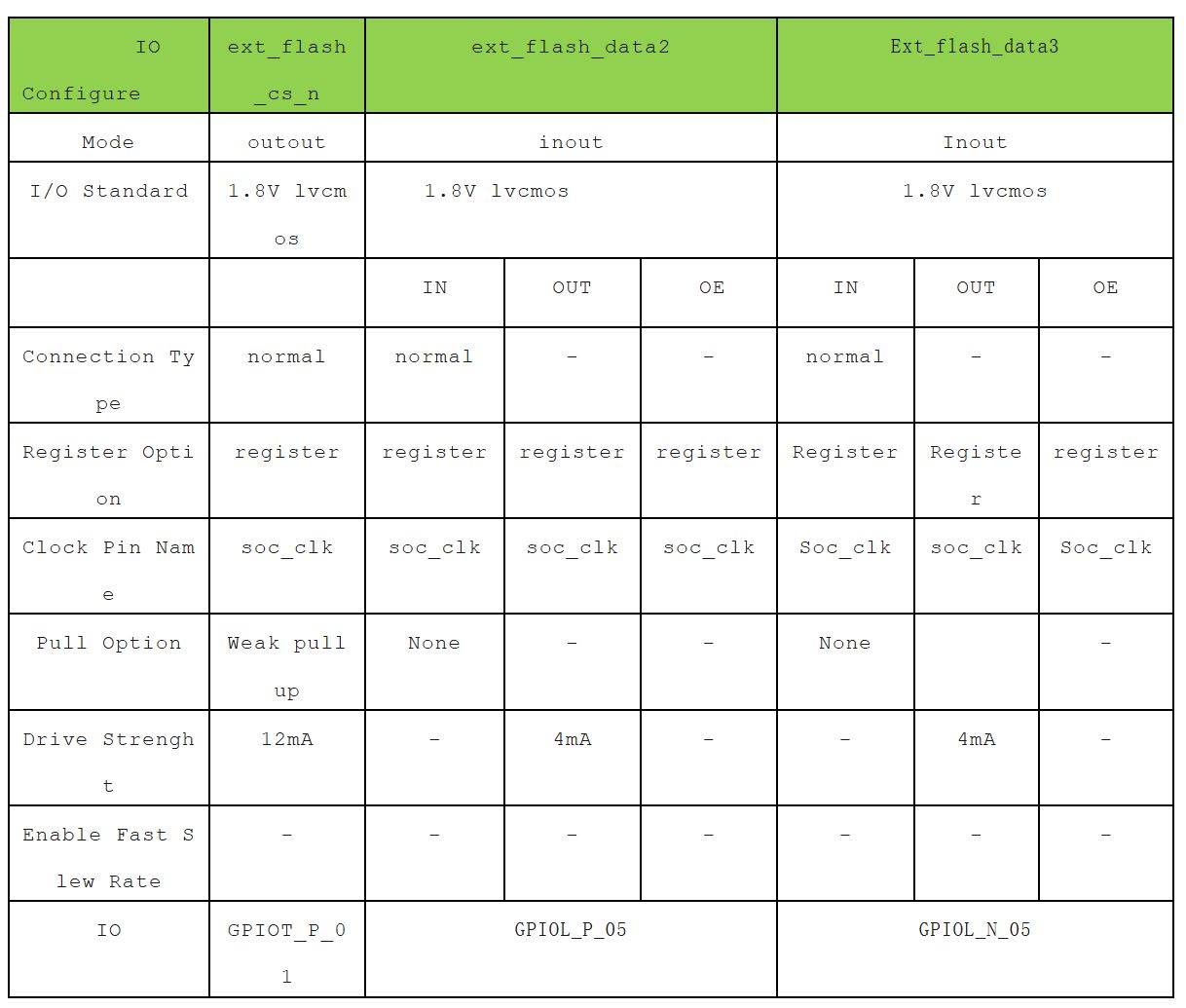

IO的连接方案如下:

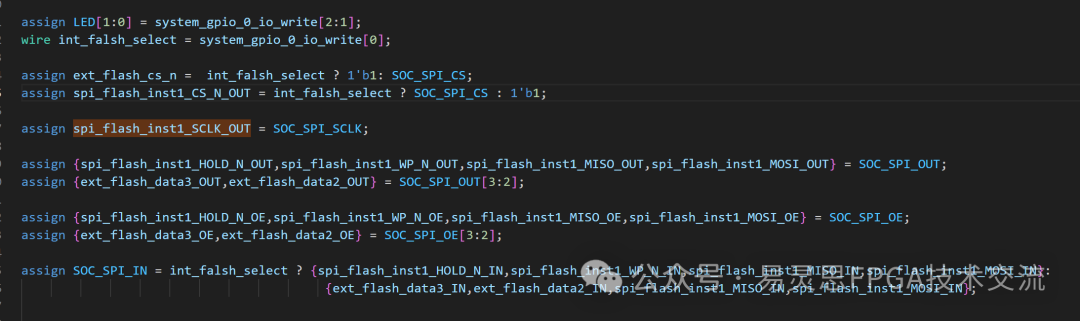

内flash与外部flash除片选信号分开外,对于4线flash,IO[3:2]是分开的,其余信号都是共用。SOC操作flash时,我们通过一个GPIO来控制flash的选择。

可能会有人有疑问为什么内外flash的管脚能够共用呢?因为内部flash的管脚也拉到GPIO上面的原因。如下图SSL_N,CCK,CDI0,1和都是与内部flash相通的。

外部flash的data2,data3及cs_n的接口配置。

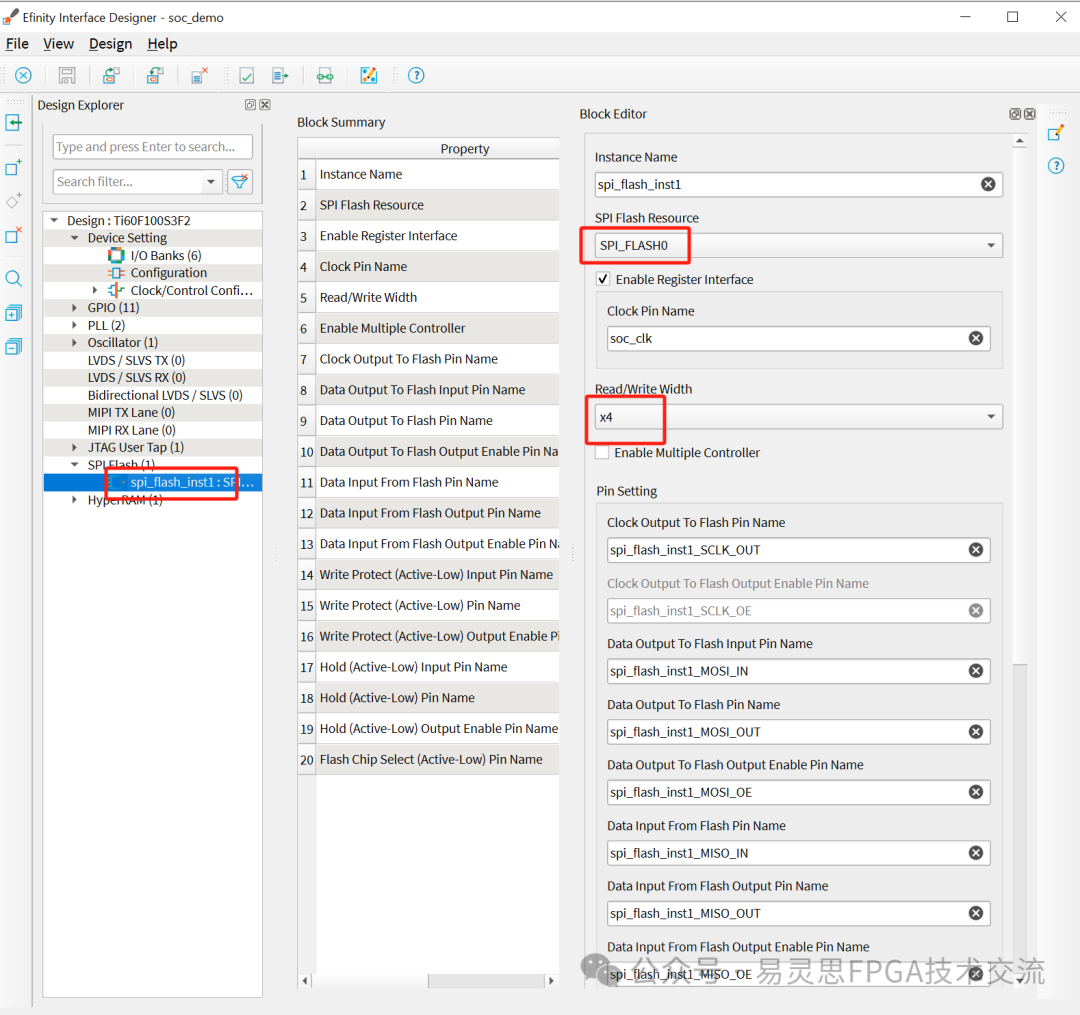

添加SPI flash block,如下图,使能Enable Register Interface, Read/Write Width设置为4。

FPGA通过GPIO来控制操作内部与外部flash,如下图,通过gpio_0来控制选择内部flash还外部flash,int_flash_select为高,表示选择内部flash,为低则选择外部flash。

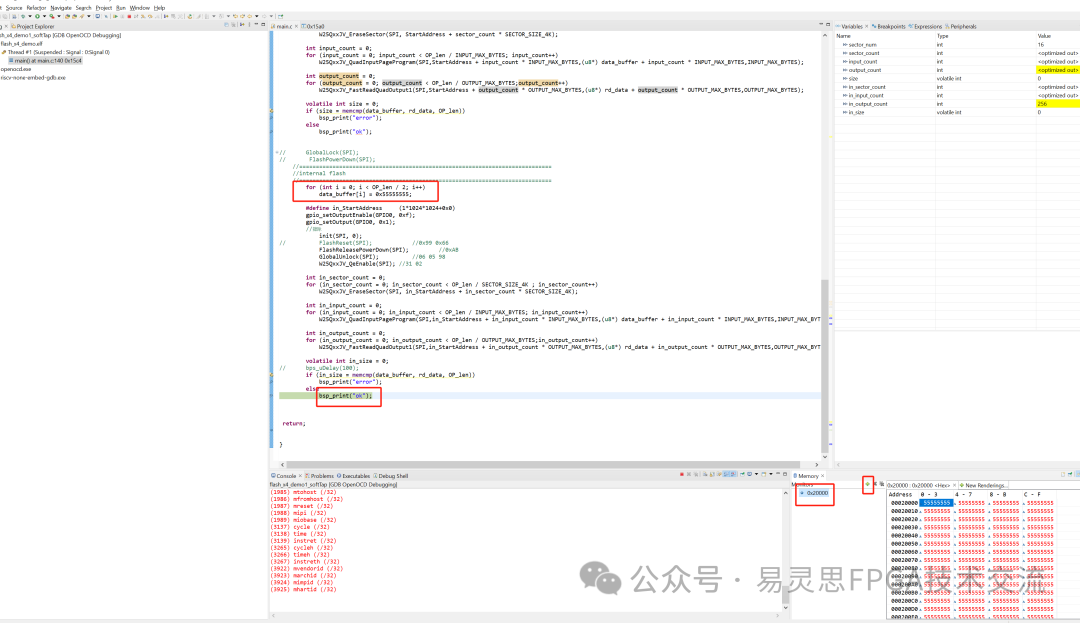

调试

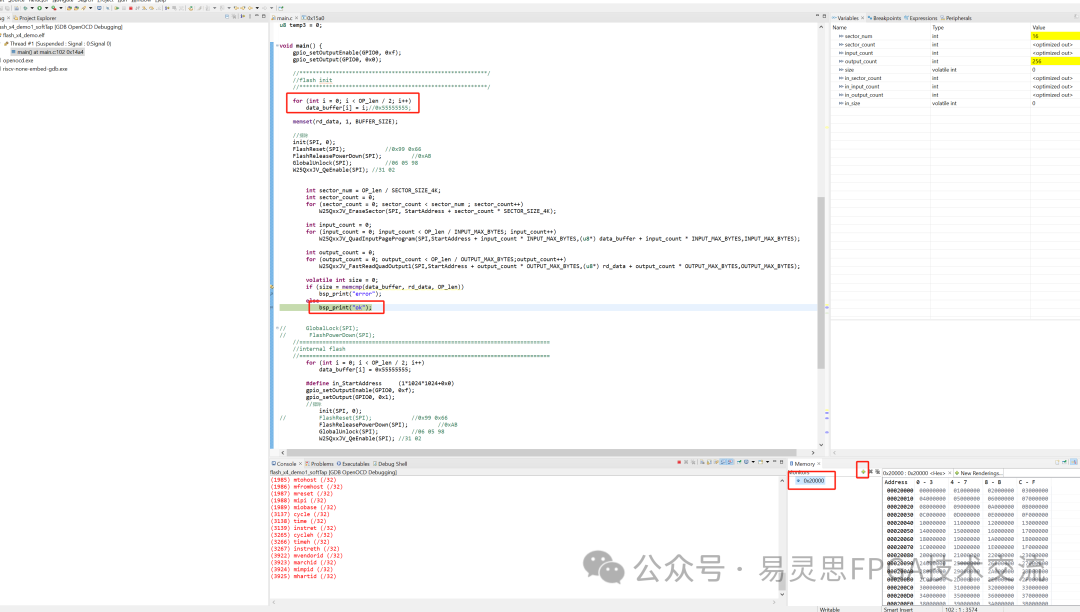

程序经过擦除-->写入-->读出操作后,内存0x20000的数据为下图所示。

程序经过擦除-->写入-->读出操作后,内存0x20000的数据为下图所示。