文章概述

本文介绍了I2S收发器的配置与实现,用于FPGA的VHDL编程。I2S是数字音频的标准化串行通信总线,由SCK、WS和SD三条线路组成。文章阐述了I2S收发器的工作原理,包括数据传输方式、操作理论、配置方法、端口描述以及音频数据事务传输。

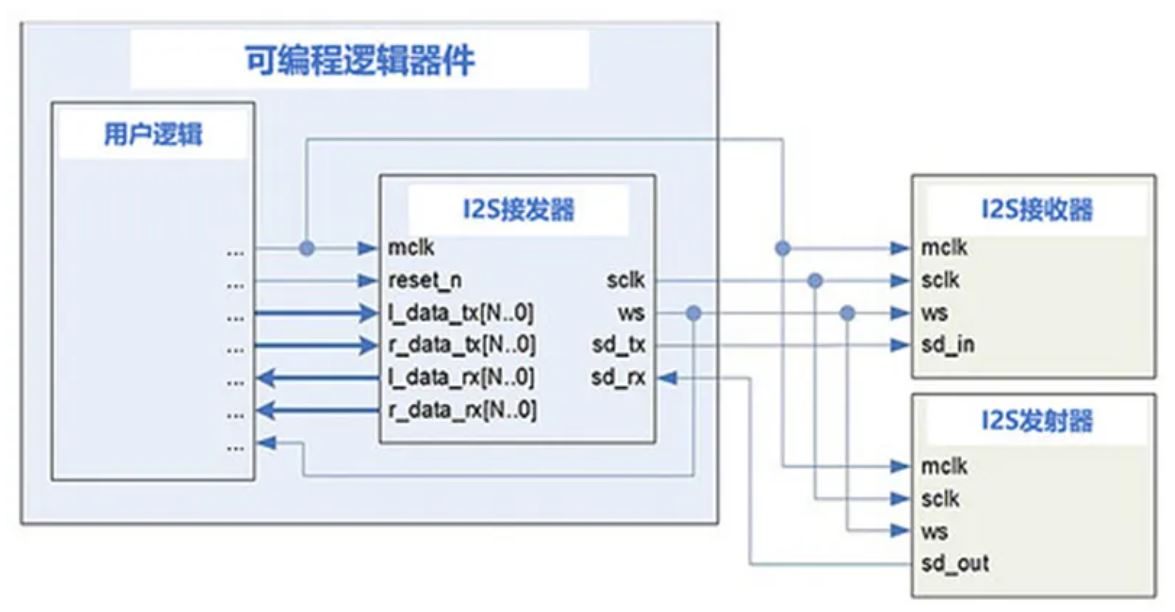

本文详细介绍了一个主 I2S 收发器组件用于 FPGA,以 VHDL 编写。组件通过 I2S 接口接收音频数据,并将接收到的数据在某一采样率上传送给并行接口上的用户逻辑芯片。它还在某一采样率上从用户逻辑芯片上接收并行数据,并通过 I2S 接口将这些数据传输出去。图1说明了将 I2S 收发器集成到系统中的一个典型示例。

背景

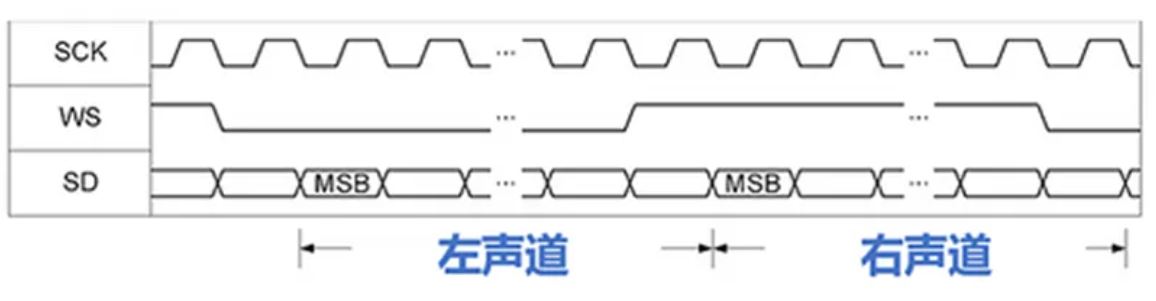

I2S (也称为 IIS) 是用于数字音频的标准化串行通信总线。该总线由串行时钟 (SCK)、字段选择信号 (WS)和串行数据 (SD) 3条线路组成。图2显示了 I2S 通信链路的数据帧。

配置I2S 收发器

I2S 收发器通过在 ENTITY 中设置通用参数进行配置。

sclk_ws_ratio

提供主时钟 (Master Clock)

I2S 收发器需要一个主时钟时钟输入来操作。该时钟是发送到 I2S 收发器正在通信的 I2S 从设备的同一主时钟信号。

端口的描述

I2S收发器接口说明如表1所示。

表 1 . 端口的描述

音频数据事务传输

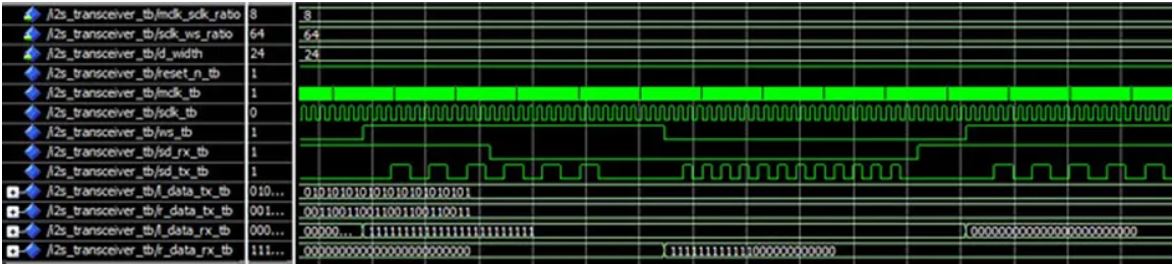

I2S 收发器使 l_data_rx和r_data_rx端口上的用户逻辑可以使用接收到的数据。这两个接收数据端口在每次ws转换时都会更新。由于新的左声道数据仅在ws= ’ 0 '时接收,因此l_data_rx端口与ws的上升沿同时获得新值,即当左声道数据字段完成时。同样,新的右声道数据仅在ws= " 1 " 时接收,因此r_data_rx端口与ws的下降沿并发获得新值,即当右声道数据字段完成时。用户逻辑可以使用ws 信号来指示新数据可用,从而以采样率检索该数据。图3 说明了这种行为。

类似地,I2S 收发器在每个 ws转换的l_data_tx和r_data_tx端口上锁存新的传输数据。用户逻辑可以使用ws信号来指示何时将其输出数据锁存,因此可以自由地在这些端口上呈现下一组传输数据。锁存在ws下降沿上的l_data_tx值在左声道数据字段传输期间在sd_tx上传输。同样,锁存在ws上升沿上的r_data_tx值在右声道数据字段传输期间在sd_tx 上传输。图3 显示了这种行为。

重置(Reset)

reset_n 输入端口必须具有逻辑高,I2S 收发器才能正常工作。该端口上的低信号将异步复位组件。复位期间,组件保持 sclk 、ws 和 sd_tx 端口为低电平。任何当前正在进行的传输都将停止。任何当前正在进行的接收被放弃,l_data_rx 和 r_data_rx 输出端口清空。清除所有内部数据缓冲区。一旦解除复位,I2S 收发器恢复工作。

结论

I2S 收发器是一种可配置的可编程逻辑组件,通过标准 I2S 总线传输和接收音频数据。它作为主控器工作,为接口提供串行时钟和选字信号。它允许用户为特定的采样频率、数据宽度、主时钟和每字串行时钟周期数进行配置。

文章来源:DigiKey得捷