作者:Iris Yang,AMD工程师;文章来源:AMD开发者社区

介绍

这篇博客文章将详细介绍如何通过NOC使用CPM访问片上内存(OCM)。该设计的主要重点是确保PCI接口的地址映射配置正确,使得其可以正确访问OCM地址范围。通过实现这一点,我们可以促进PCIe主接口和OCM之间的高效数据传输和通信。本博客将提供建立此连接所需的配置和步骤指南。

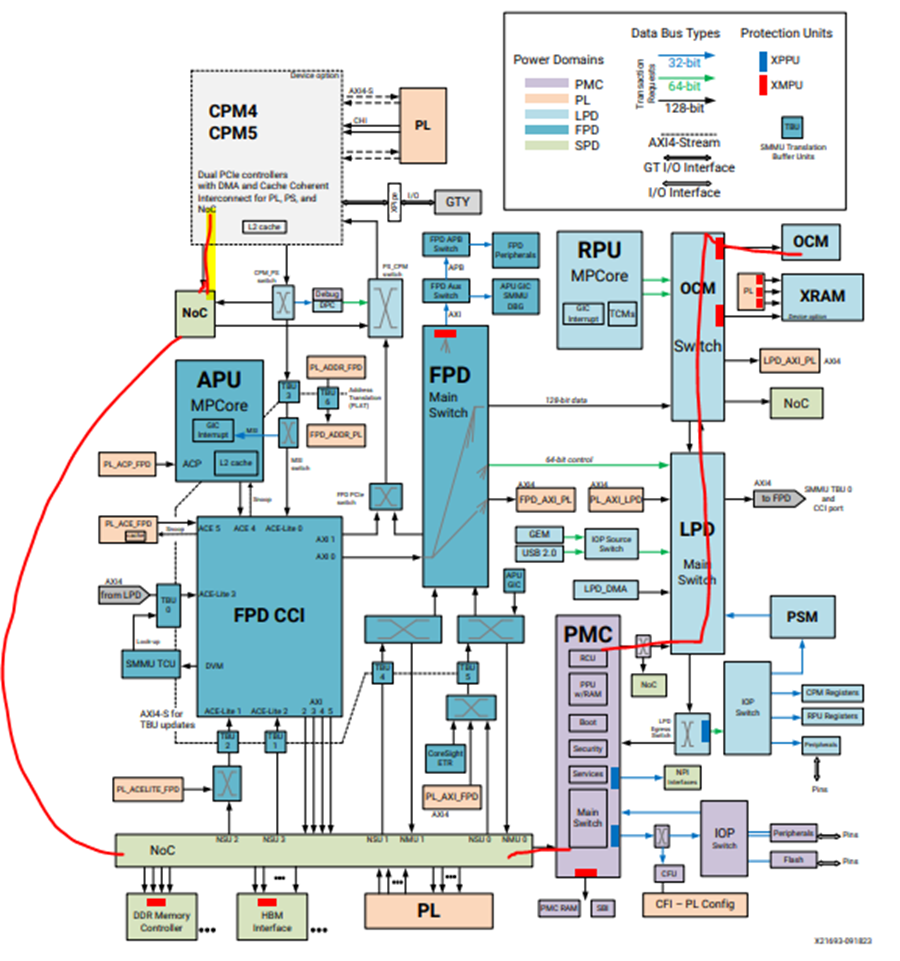

理解片上内存(OCM)

片上内存(OCM)通过其128位AXI接口端口访问256 KB内存。可以通过LPD OCM交换机访问OCM。从RPU的内存访问优先级高于其他内存事务请求。具体的信息请参考am011。

用 CPM生成访问OCM的设计

要生成一个通过CPM(PCIe)访问片上内存(OCM)的设计,需要使用带PCIe连接 Versal CIPS IP,并确保正确的PCIe到AXI地址转换和配置,请按照以下步骤操作:

步骤

准备Versal器件

首先选择带 CPM 的Versal的开发板 (vck190/vpk120 等),并使用Vivado或相关工具设置设计环境。

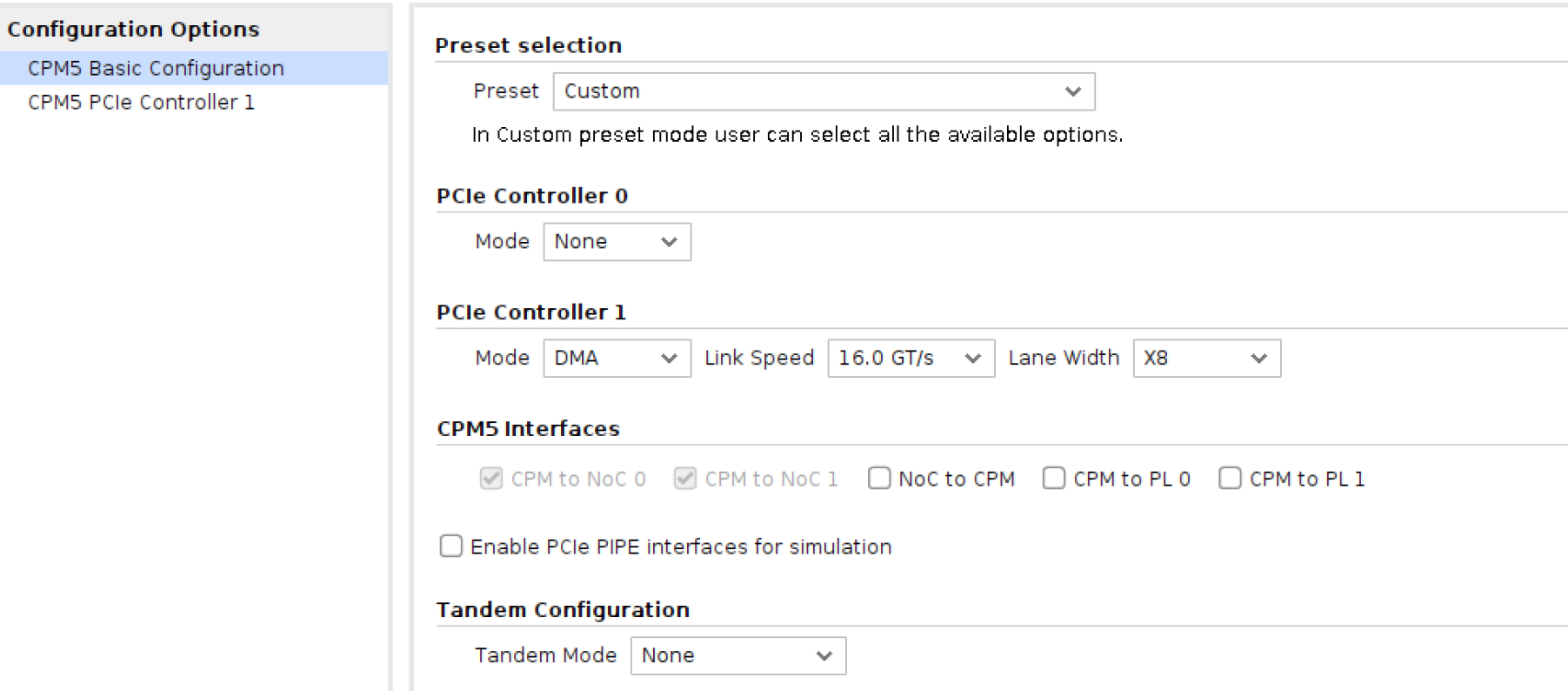

CIPS IP配置:

将CIPS 加入到设计中。

配置PCIe控制器选择DMA模式运行。

根据项目要求选择PCIe接口的所需速度和链路宽度。

CPM配置:

使用CPM接口通过NOC访问OCM,选择QDMA ,桥接 bridge或XDMA模式的应用模式也类似)。

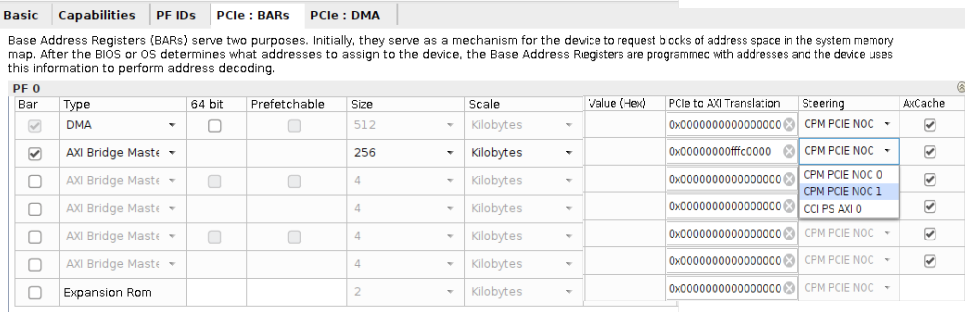

PCIe地址转换:

GUI中,配置PCIe到AXI的地址转换:

启用BAR1(AXI master bridge)进行PCIe地址转换。

将PCIe到AXI的地址转换设置为FFFC0000(与OCM地址范围一致)。将大小设置为256KB,并将方向设置为NOC1。

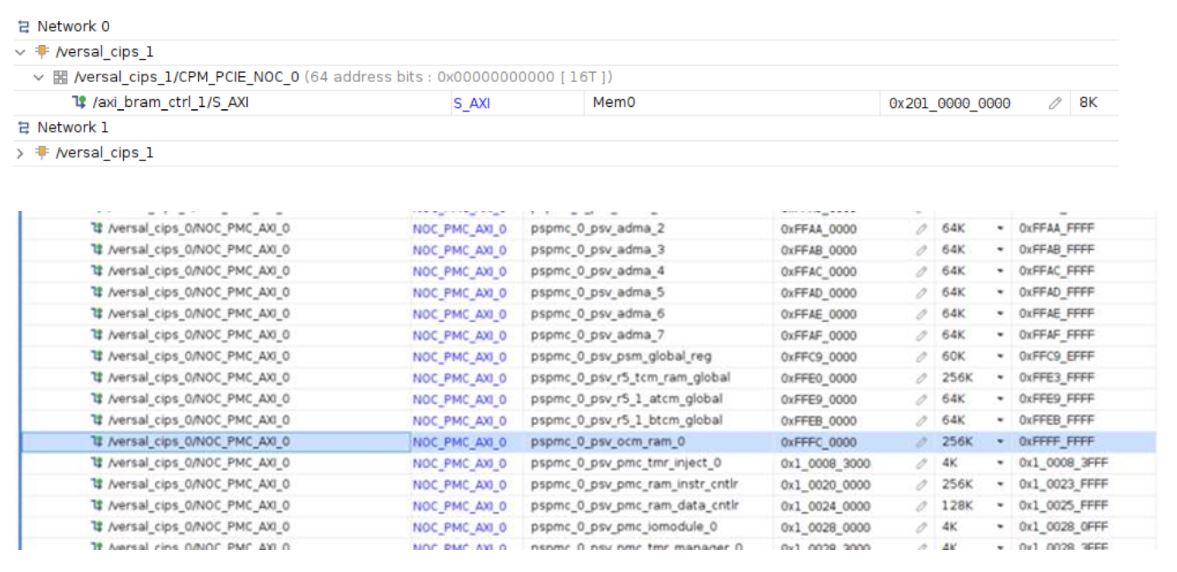

地址编辑器配置 (address editor):

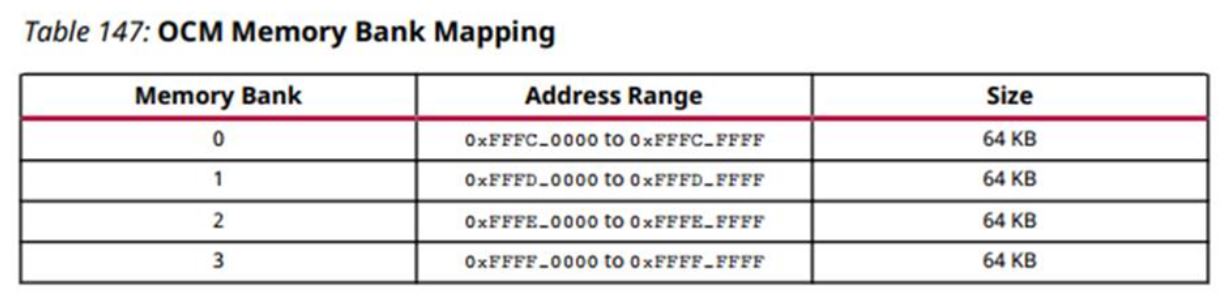

确保在地址编辑器中为 PCIe 访问设置了正确的 OCM 地址(FFFC0000)。这个地址与下方所示的 am011 中的表 147 一致。

测试设计

配置 Versal FPGA、重新启动并运行 lspci,然后执行 devmem2 写命令以测试 OCM 访问,请按照以下步骤进行操作:

配置和测试步骤:

1. 配置 Versal FPGA:

确保 Versal FPGA 配置了所需的设计,包括 PCIe 接口和 CPM 配置,符合您的要求。

2. 重新启动系统:

重新启动系统。

3. 检查 PCIe 设备:

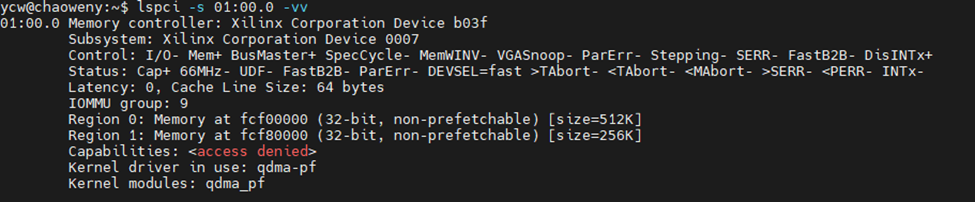

查找与您的 Versal FPGA PCIe 接口对应的 PCIe 设备。设备的Device ID 应该和符合IP 配置的内容,这个例子用了默认的b03f

注意:在此测试中,不需要 QDMA 驱动程序。

重新启动后,使用 lspci 命令列出 PCIe 设备:

4. 使用 devmem2 访问 BAR1:

写入 BAR1:

使用 devmem2 向 BAR1 内的目标地址写入数据。将 <target_address> 和 <data> 替换为适当的值:

devmem2 <target_address> w <data>

读取 BAR1:

使用 devmem2 从 BAR1 内的目标地址读取数据。将 <target_address> 替换为适当的地址:

devmem2 <target_address>

结论:

通过遵循上述步骤和配置,应该可以通过 CPM 使用 CIPS IP 在具有 PCIe 连接的 Versal 设备上访问 OCM。用户需要确保地址转换和配置设置是正确的。