随着电子产品中图像和视频的分辨率不断增加,需要更大的带宽进行传输。然而,传输带宽的增长速度远远落后于图像分辨率的增长速度,导致带宽瓶颈问题。尽管可以通过增加更多的链路数或者其他更昂贵的方法来解决这种问题,但是这些方法在系统的成本、功耗和兼容性方面存在巨大的缺陷。因此,需要有一种图像/视频压缩算法,降低传输带宽的需求,从而解决了这一问题。VESA的显示流压缩标准DSC(Display Stream Compression)就是为了解决这个问题而产生的视频压缩方案。

自2014年推出以来,DSC在实现视频传输压缩方面取得了广泛的成功。DSC已经被包括DisplayPort、HDMI和MIPI DSI在内的主要显示接口标准所采用,它能够为超高清(UHD)显示应用提供了视觉无损压缩,同时也有助于在DisplayPort和USB-C接口上实现高动态范围(HDR)和8K视频传输。经过DSC压缩后,在HDMI 2.1 的 48 Gbps 和 VESA DisplayPort 1.4 的 32.4 Gbps 物理带宽上能够传输8K@60 fps的视频流。

使用DSC有许多优势。首先,它可以降低传输带宽的需求,使得高分辨率图像和视频的传输更加轻松。其次,使用DSC可以降低系统的成本,减小设备的尺寸,降低电磁干扰,并节省功耗。最重要的是,DSC可以在保持视觉无损和几乎无延迟的情况下压缩图像和视频数据,从而确保用户获得高质量的图像和视频体验。

目前,DSC已经被广泛应用于视频传输的各个领域。首先是移动应用领域,例如智能手机和平板电脑。随着移动设备中图像和视频的分辨率不断提高,使用DSC可以降低传输带宽,提高系统性能,并延长电池寿命。其次是汽车应用领域,汽车特别是新能源电车中涉及到许多摄像头和显示器,使用DSC可以降低传输通道数量,减少系统成本和功耗。另外还有AR/VR和头戴式显示器应用,使用DSC可以降低传输延迟,提高视觉体验。此外,DSC还可以应用于USB Type-C接口、电视和机顶盒等领域,以满足高带宽传输需求。

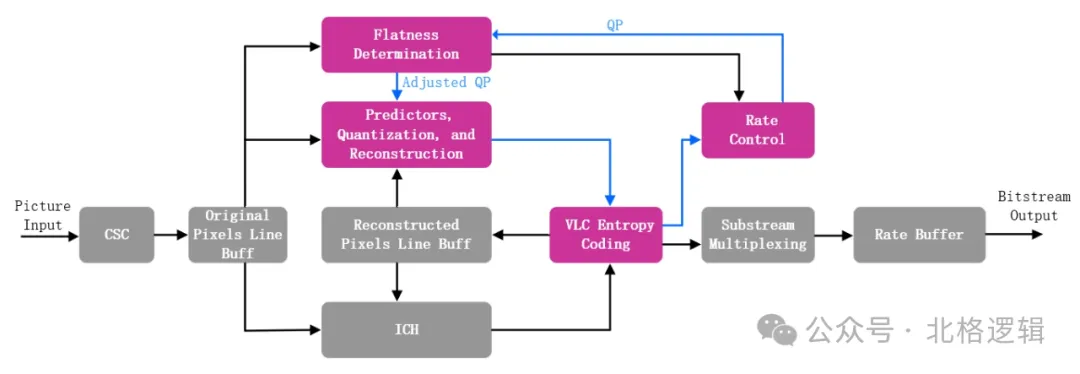

DSC编码器处理流程

DSC 主要由预测(MMAP、BP、MMP三种预测模式,其中BP是可选的模式)、量化与重建、ICH(历史颜色索引)、VLC熵编码、码率控制、平坦度检测等模块组成。目标压缩倍数在3倍左右,处理延迟约为1行,提供视觉无损的画质。MMAP预测方式中,最佳情况下,只需要用3比特就可以编码三个像素(即一个编码组);平均情况下,用8比特编码一个像素是比较容易做到的。在ICH模式下,满足条件时三个像素只需要用16比特即可编码。因此,对于DSC编码方案而言,3倍压缩达到视觉无损并不困难。DSC可以指定将一个24bit的像素,压缩到8.0625或者7.9375比特,压缩后的比特数支持1/16比特的精度。通过精准的码率控制,DSC可以实现微观粒度上的稳定码率,保证压缩后的码率在MIPI DSI/DP等接口上传输时,能够跟图像帧timing保持一致,不会出现overflow or underflow。同时,通过控制 rate buffer的 fullness,以及按平坦度信息调节量化参数,在不浪费码率的情况下,可以保证在图像复杂区域和平滑区域都获得大致相等画质。DSC编码器和解码器采用基本一致的处理流程,在解码端可以根据已知信息推断中当前编码组采用的编码模式和量化参数, 减少控制信息的传递,提高了编码效率。DSC一个slice每次完成3个或6个像素的编码或解码,整个处理流程由若干个时钟周期完成。为了增大DSC的编解码性能,就需要有多个slice并行计算,根据需要可以将整个图像等分成多个slice,slice之间的处理完全独立。

DSC压缩信噪比

上图是一张色深为8的RGB图像经过DSC压缩后的信噪比,横坐标是压缩倍数,BPP行表示的是压缩后每像素的比特数,MAE行表示的是平均绝对误差。可以看到1.6倍-3倍压缩期间,信噪比大于48dB,压缩后的图像质量非常高,仅有非常小的误差。在这种情况下,原始图像和压缩后的图像之间的差异几乎不可察觉。在4倍压缩时,信噪比也有42dB,人眼很难察觉到这种压缩水平下图像的失真。这意味着压缩后的图像在视觉上与原始图像非常接近。

接下来,介绍一下DSC IP在FPGA实现中一些特点。DSC在预测和码率控制阶段设计精巧,可以在有限的码率下达到优秀的画质,同时对码率在微观层面进行精准控制,保证编码后的码率达到像素级的稳定输出。然而,达成这个目标是需要付出代价的。本文图2中高亮标注的几个模块是DSC的timing关键路径。预测模块完成当前编码组的计算后,并不能立即开始下一个编码组的处理。需要经过VLC熵编码模块选定编码模式后才能获得最终的重建值,再由Rate Control模块和Flatness Determination模块产生量化参数,才能进行下一个编码组的处理。因此,DSC的每个模块只在处理周期的一部分cycle内是处于工作状态的。在FPGA实现中,由于DSC的功能模块没有工作在全流水状态下,导致DSC的逻辑使用量相对偏高,同样的处理性能,DSC编码器需要的逻辑资源是JPEG XS的约4.5倍,是JPEG2000的约1.2倍。为了提高各个模块的在处理周期中有效利用率,需要尽量减少处理周期的cycle数,这又导致DSC的每一级流水的处理复杂度偏高,逻辑级别大,因此DSC IP在FPGA中的主频一般设置在150Mhz比较合适。对于DSC解码器,由于可以提前计算出当前编码组的量化参数,同时ICH模块不需要查表,解码器的处理周期变短,使用的逻辑资源也更少。相同处理性能下,DSC解码器的资源使用量是编码器的70%。为了降低DSC IP在FPGA中的逻辑占用量,一个可选的方案是关闭BP预测功能,BP功能约占编码器20%的逻辑资源。

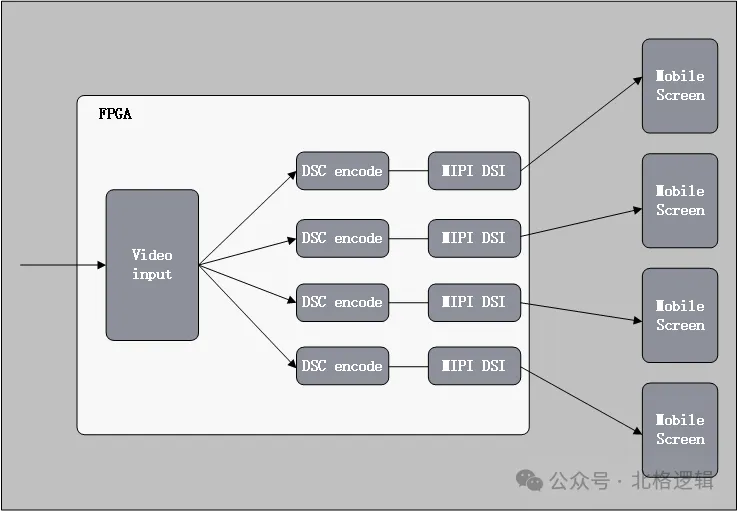

北格逻辑致力于为视频行业提供高性能的、基于FPGA的视频处理IP。我们从2020年开始,就保持着对DSC 编码方案的持续关注,在我们接触到的应用场景中,DSC已经广泛的应用于各种视频高速传输接口。例如,手机处理器Processor和显示面板驱动IC之间通常通过带DSC功能的MIPI接口进行连接。结合FPGA应用场景,在手机屏幕老化测试时,可以用一块FPGA驱动多个MIPI DSI接口,每个接口都支持DSC编码,这样就可以极大的提高测试效率。另外,在LED显示屏的视频传输过程中,不压缩情况下一路1080P就需要4条千兆网线才能传输。如果采用了DSC方案,压缩3.5倍,只需要一根千兆网线就能完整传输一路1080P,而且能够保证低延迟、视觉无损。最契合的是,DSC解码IP比较小,而LED显示屏的每块小屏都对应着一块小的接收卡,接收卡的数量远远多于发送卡,接收卡解码IP越小,方案成本越低。因此,我们决定结合自身在视频编解码领域的深厚积累以及FPGA工程实现上的丰富经验,基于DSC最新规范v1.2b开发DSC FPGA IP,为行业提供高性价比的DSC解决方案。在标准版本的基础之上,我们可以提供IP定制服务,通过去除可选的编码机制(例如BP)以及限定色深等方式,生成符合需求的最小资源版本,提供FPGA方案的性价比。

DSC与MIPI DSI结合用于驱动带DSC功能的手机屏

以下是北格逻辑DSC 编解码IP的技术特性:

符合 VESA DSC v1.2b 标准 支持所有 DSC v1.2b 强制和可选编码机制 向后兼容 DSC v1.1 版本 可配置的最大显示分辨率高达 8K(超高清) 视频色深支持 :8 位、10 位、12 位 支持YUV 和 RGB 视频格式 并行slice数量支持:1、2、4、8个 单slice处理性能:1080P@60fps 128 字节的PPS 每像素压缩后比特数:6.0-63.9375比特(对应于压缩倍数是1-4倍) 编解码/解码器各自延迟:约1行,可配置 视频输入输出接口采用AXI-Stream 寄存器配置采用AXI-lite接口 可与MIPI DSI 1.2、eDP 1.4b、DP 1.4以及 HDMI 2.1搭配使用 编解码器之间可以根据各自能力列表协商编码模式