嵌入式系统等需要进行大量计算和数据处理的应用,通常使用微控制器、微处理器和现场可编程门阵列(FPGA)等器件来执行复杂的计算例程,因为这些器件具有多功能性、高速度和灵活性。然而,这些推荐使用的器件也存在限制和不同的电源要求,如果在系统开发的早期阶段未加考虑,系统的性能和可靠性可能会受影响。其中一个限制是掉电状况下系统可能出现故障。当电源电压降至最低工作电压以下时,微控制器可能会发生故障并导致系统出错。幸运的是,电压监控器专门设计用于解决这个问题。

本文讨论了高性能电压监控器,包括ADI公司产品系列中的一些产品,介绍了电压监控器的功能、输入和输出基础以及高性能电源监控产品的其他基础知识。

电压监控器定义及其工作原理

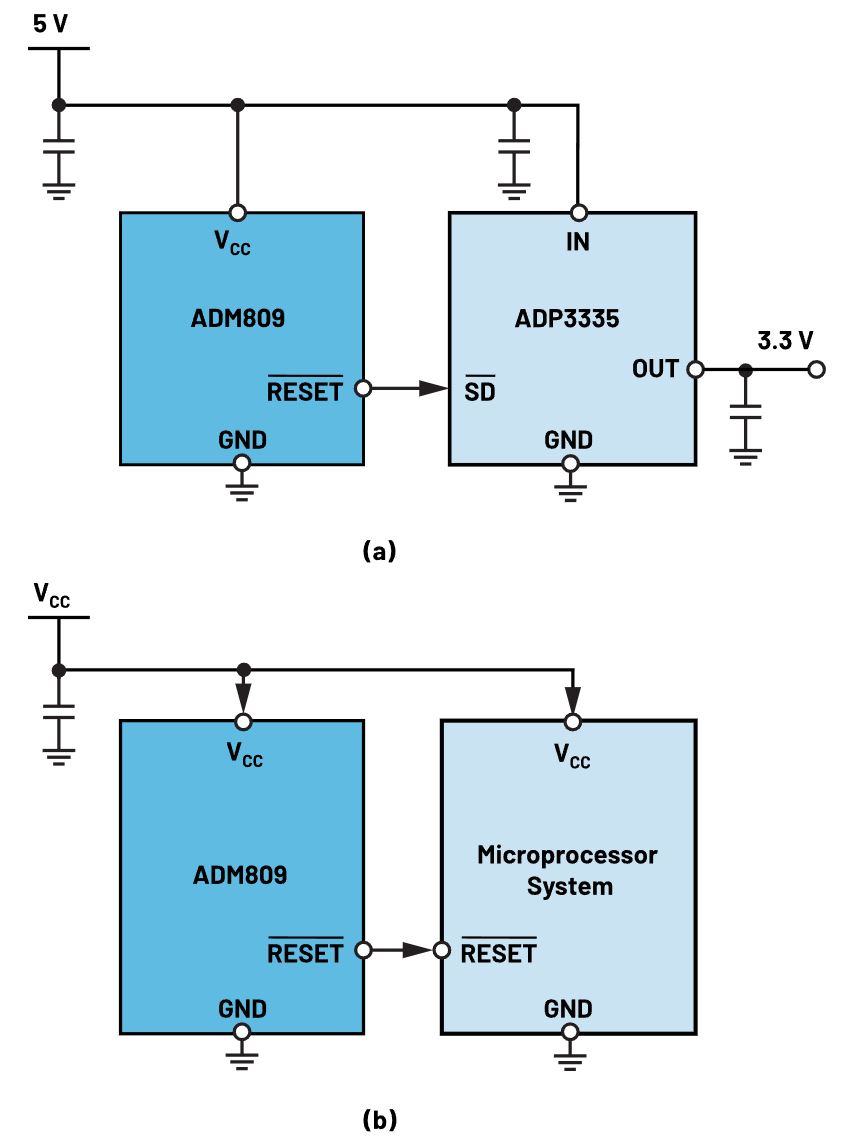

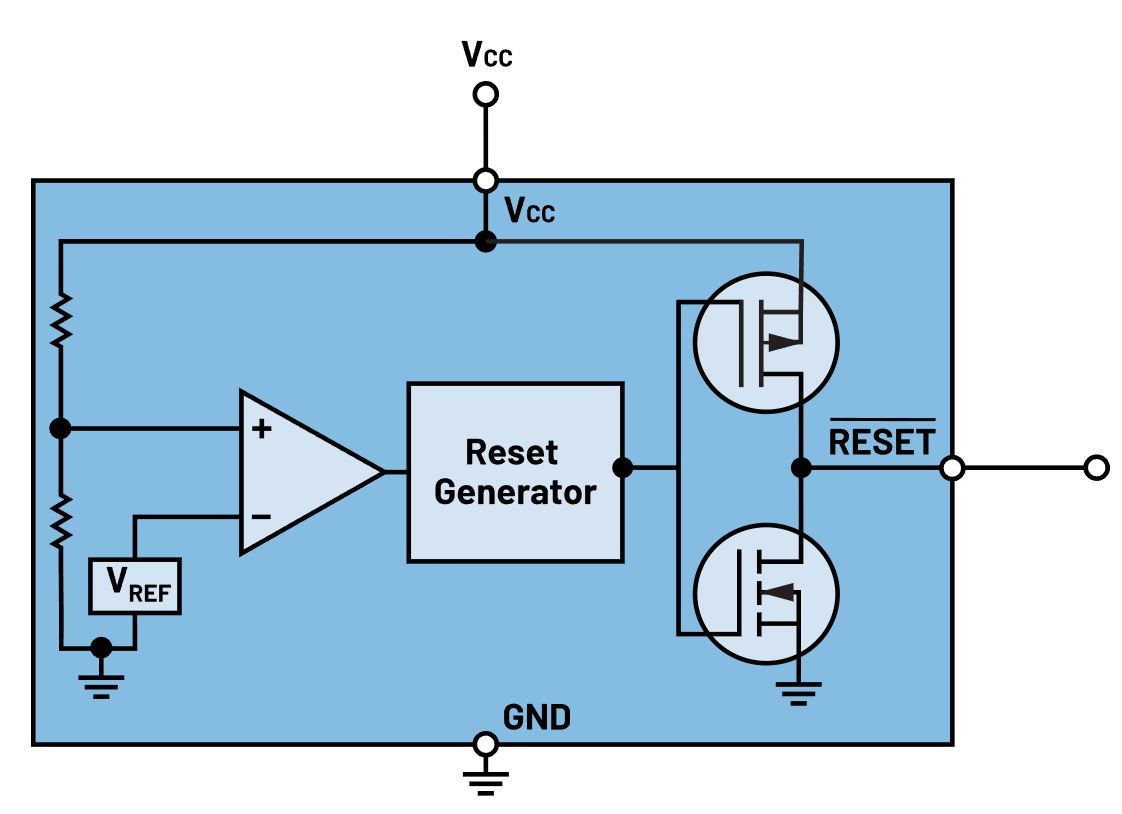

电压监控器是一类用于监控电压供应轨的器件,只要满足监控条件,它就会提供一个可用来执行某种操作的输出。它会检测被监控电压供应轨是否低于或超过预定义的电压水平(称为阈值)。它提供的输出信号通常称为复位信号,用于将另一个器件置于另一种工作模式,例如复位模式或活动模式。对于那些在特定电压范围之外运行会导致错误和故障的应用来说,使用电压监控器也是十分合适的。有时,复位输出也用于使能和禁用另一个器件,例如在任何需要一定输入电压范围才能正常运行的应用中。一个典型的应用例子是使用电压监控器来让稳压器正常运行,如图1a所示。为了确保启动期间正常运行,LDO稳压器要求输入中有足够的能量,或者说需要足够高的输入电压水平。

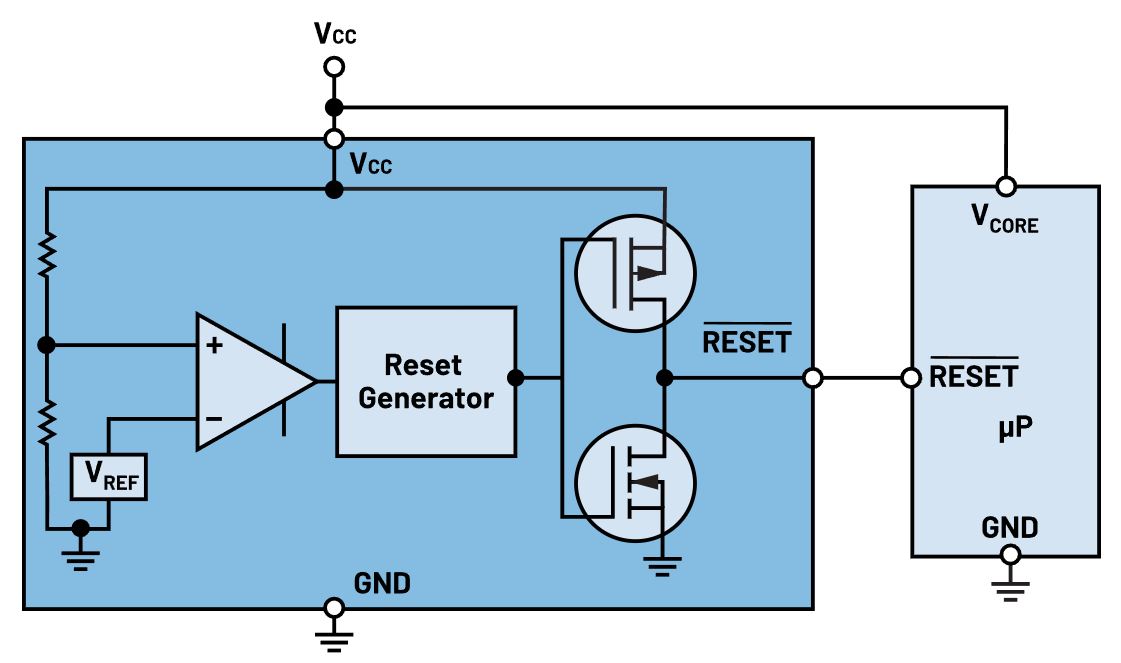

众所周知,电压监控器是与微控制器或MCU密切相关的搭档。当命令正在执行的时候,如果电源电压降至最低工作范围以下,MCU就有发生故障和造成系统出错的风险。在这种情况下,MCU的电源电压即为被监控电压,MCU的最低工作电压应为阈值电压。我们将在文中进一步讨论如何定义阈值电平。用于监控微控制器电源的电压监控器的一个简单例子是ADM809如图1b所示。监控器检测被监控的电压水平,并将其馈入 VCC 引脚。一旦被监控的电压低于阈值,低电平有效复位输出就会将微处理器置于复位模式,直至电压供应恢复到正常水平。

图1. ADM809是电压监控器的一个简单例子,它监控输入电压以(a)在输入电压水平处于正确范围以内时使能LDO稳压器,并(b)在掉电状况下将微处理器系统置于复位模式。

电压监控器有哪些重要输入规格参数?

关于电压监控器,需要了解四个重要输入规格参数。这将有助于系统设计人员实施电压监控器来提升系统在应用中的可靠性。这些规格参数包括复位阈值、阈值精度、复位阈值滞回和上电复位。

复位阈值

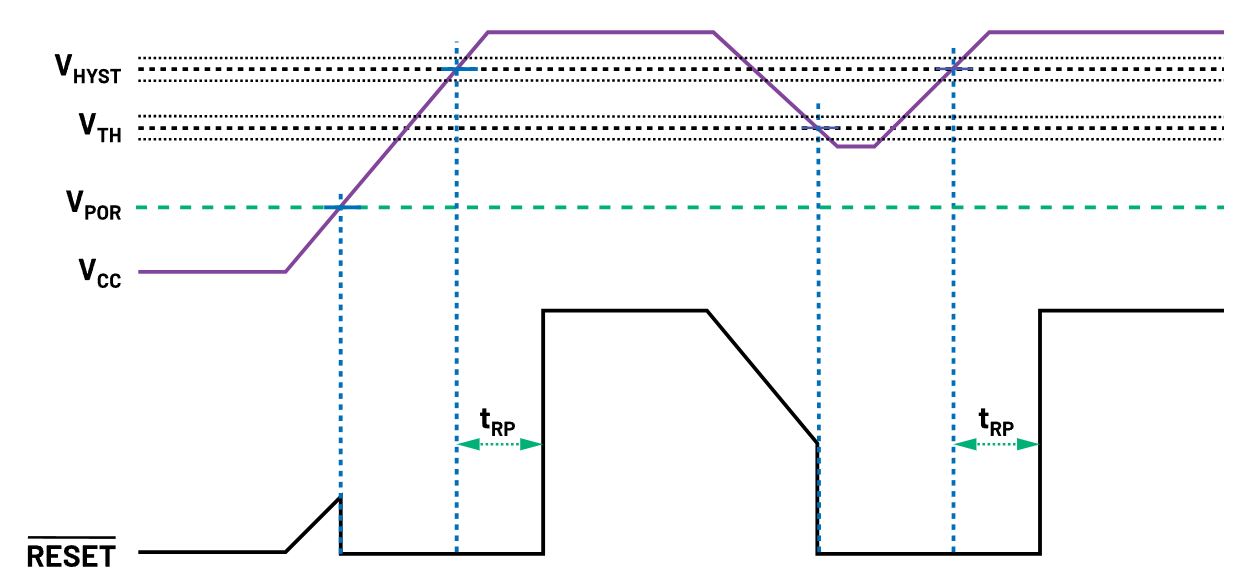

复位阈值是电压电平;当被监控的电压低于此值时,它就会发出复位信号。在电压监控器产品中,复位阈值通常标记为 VTH。当被监控电压 VCC降至复位阈值电压 VTH以下时,它会产生低电平复位输出,如图2中的时序图所示。在应用中,阈值电压设置为允许系统正常运行的最小电压。

图2. 电压监控器的被监控电压 VCC和复位输出信号的时序图。

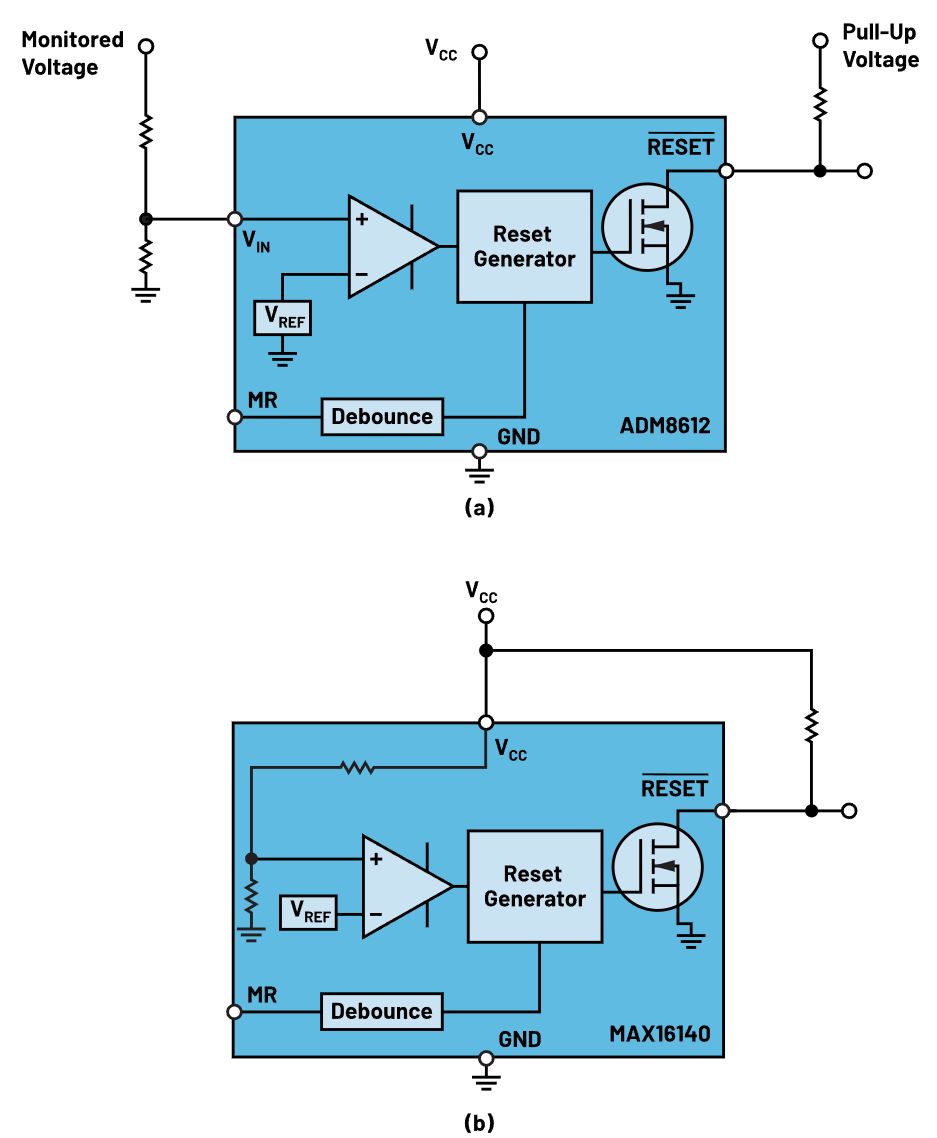

设置复位阈值的一种方法是通过外部电阻分压器。被监控电压的一小部分与基准电压源进行比较,以了解被监控电压是否高于或低于复位阈值,如图3a所示。ADM8612 是此配置的一个例子。一些电压监控器的复位阈值是在工厂通过激光调整由内部电阻分压器设置的,例如 MAX16140。这带来了一些优势,例如外部元件更少,可以为解决方案腾出额外空间,满足紧凑型应用的需求,如图3b所示。它还能实现更高的精度,因为它不依赖于外部因素(例如使用具有容差的标准值电阻)。然而,外部电阻方案支持灵活地调整复位阈值电平。

图3. 复位阈值的设置方法:(a) ADM8612复位阈值通过外部电阻分压器设 置,(b) MAX16140复位阈值通过工厂调整的内部电阻分压器设置。

阈值精度

阈值精度是指实际阈值与计算的复位阈值或目标复位阈值的接近程度。一些因素会影响阈值的精度,包括电阻分压器和基准电压。电阻分压器和基准电压都是模拟电路,受温度等环境因素的影响。这导致复位阈值有一定的容差。基准电压和电阻越稳健,容差就越严格,阈值精度就越高。阈值精度通常以百分比表示。假设电压监控器的阈值精度为±1%,阈值设置为3.3 V,那么实际阈值可能在3.267 V至3.333 V左右。

了解阈值精度非常重要,因为这对于设置复位阈值至关重要。如果在设置复位阈值时不考虑精度,系统可能会陷入不理想的故障区域。

复位阈值滞回

复位阈值滞回是指被监控的电压回到正常区域后,取消复位信号所需的额外电压。在监控欠压的电压监控器中,复位阈值滞回通常表示为 VHYST 或 VTH+HYS。滞回有多项益处。首先,它确保被监控的电压回到正常水平,并且相对于阈值有一定的安全裕量。其次,它能让电源在复位取消之前先稳定下来,从而有助于解决电源噪声和不稳定性问题。在没有滞回的情况下,当被监控电压超过阈值时,电压监控器会反复发出或取消复位信号。这可能发生在有电源噪声的应用中,或发生在电池供电的系统中,因为受内部电阻的影响,电压会随着负载电流而下降。图4中的紫色阴影区域显示了一个例子。同时,由于存在滞回,复位输出将使系统保持复位模式,直到电源稳定,从而消除系统的不稳定和振荡行为,如图4.4中的蓝色阴影区域所示。

图4. 有滞回和无滞回的复位输出行为比较。

上电复位

在启动期间,当电源电压开始上升时,电压监控器的内部电路没有足够的偏置。因此,复位输出处于未定义状态。随着电源电压继续上升,它将达到某一电压供应水平,使电压监控器脱离未定义状态并发出有效的复位信号。让监控器处于规定状态并提供有效复位输出的最小电源电压称为上电复位电压或 VPOR。考虑图3b中的电压监控器简化示意图。假设开漏复位输出上拉至 VCC,在未定义状态下,复位输出将反映电源电压 VCC。这会在复位输出中产生一个毛刺,称为上电毛刺。当电源电压达到 VPOR时,监控器就会发出有效的复位输出信号,如图5所示。

图5. 启动过程中的上电毛刺和上电复位电压 VPOR。

在某些应用中,上电毛刺会被忽略且无关紧要,例如在高压系统中。但是,对于某些应用来说,例如在逻辑高电压阈值较低的器件中,这是不可取的。

电压监控器有哪些输出规格参数需要考虑?

设计电压监控器时,需要考虑的一个因素是复位输出极性和时序。您可以根据应用选择极性——低电平有效输出或是高电平有效输出。

低电平有效

低电平有效输出意味着,只要被监控电压低于阈值电压,复位输出就会变为低电平。图2中的时序图显示了具有低电平有效输出的电压监控器的响应。为了便于识别,低电平有效复位输出标记为RESET(读作RESET杠)。当被监控电压上升到阈值电压以上时,RESET输出将在指定时间内保持有效,然后才会变为高电平。此时间延迟称为复位超时周期 (tRP),它可以是固定时间,也可以通过外部电容调整。

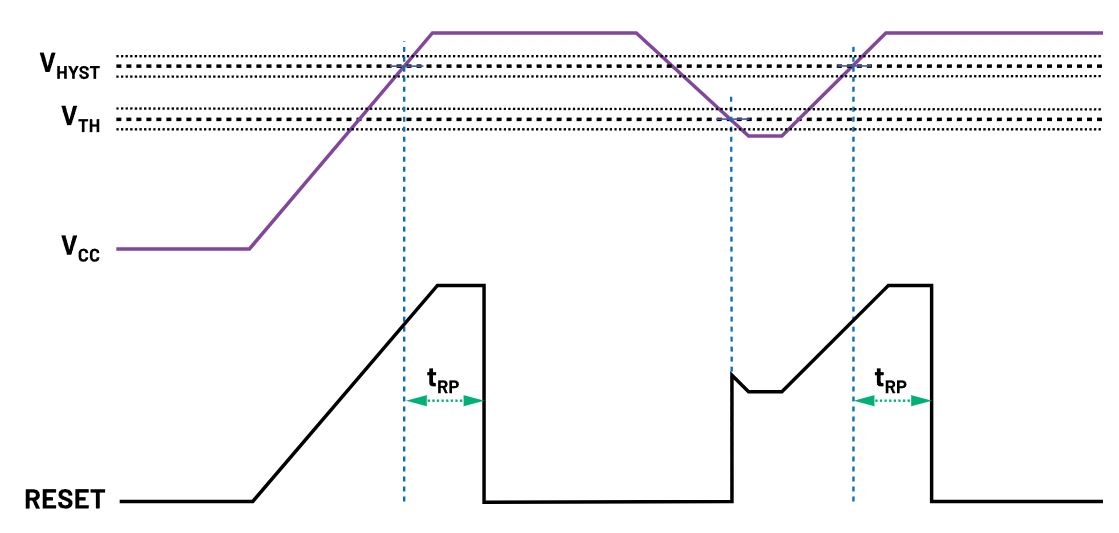

高电平有效

根据输出要求,系统可能需要高电平有效输出。与低电平有效输出相反,在高电平有效输出中,当被监控电压低于阈值时,复位输出变为高电平;当被监控电压在复位超时周期 tRP后上升到阈值电压以上时,复位输出变为低电平。图解参见图6。

图6. 高电平有效复位输出的VCC和复位信号的时序图。

根据具体应用,需要考虑的另一个因素是输出拓扑结构。主要使用两种输出拓扑结构——开漏拓扑和推挽拓扑。

推挽输出拓扑

推挽输出拓扑由一对互补MOSFET组成,如图7所示。当底部FET关断且顶部FET导通时,复位输出变为高电平;当底部FET导通且顶部FET关断时,复位输出变为低电平。推挽输出提供从低电平到高电平、从高电平到低电平的几乎轨到轨的高速响应。

图7. 推挽输出拓扑。

低电平有效推挽复位输出适用于大多数应用,但也可采用其他输出类型。如图8所示,单电压系统中的推挽输出很简单,但多电压系统中的推挽输出需要更加留心,尤其是当微控制器只有一个复位输入时。

图8. 单电压系统。

开漏输出拓扑

对于开漏拓扑,监控电路的复位输出是内部MOSFET的漏极。为了产生类似图3b所示的逻辑信号输出,需要从复位连接一个外部上拉电阻到电源电压。当MOSFET导通时,复位信号变为低电平;当MOSFET关断时,复位信号变为高电平。上拉电阻可以连接到除监控电路电源之外的电压轨。这对于需要不同于监控器电源电压的复位电平的系统来说非常有利。

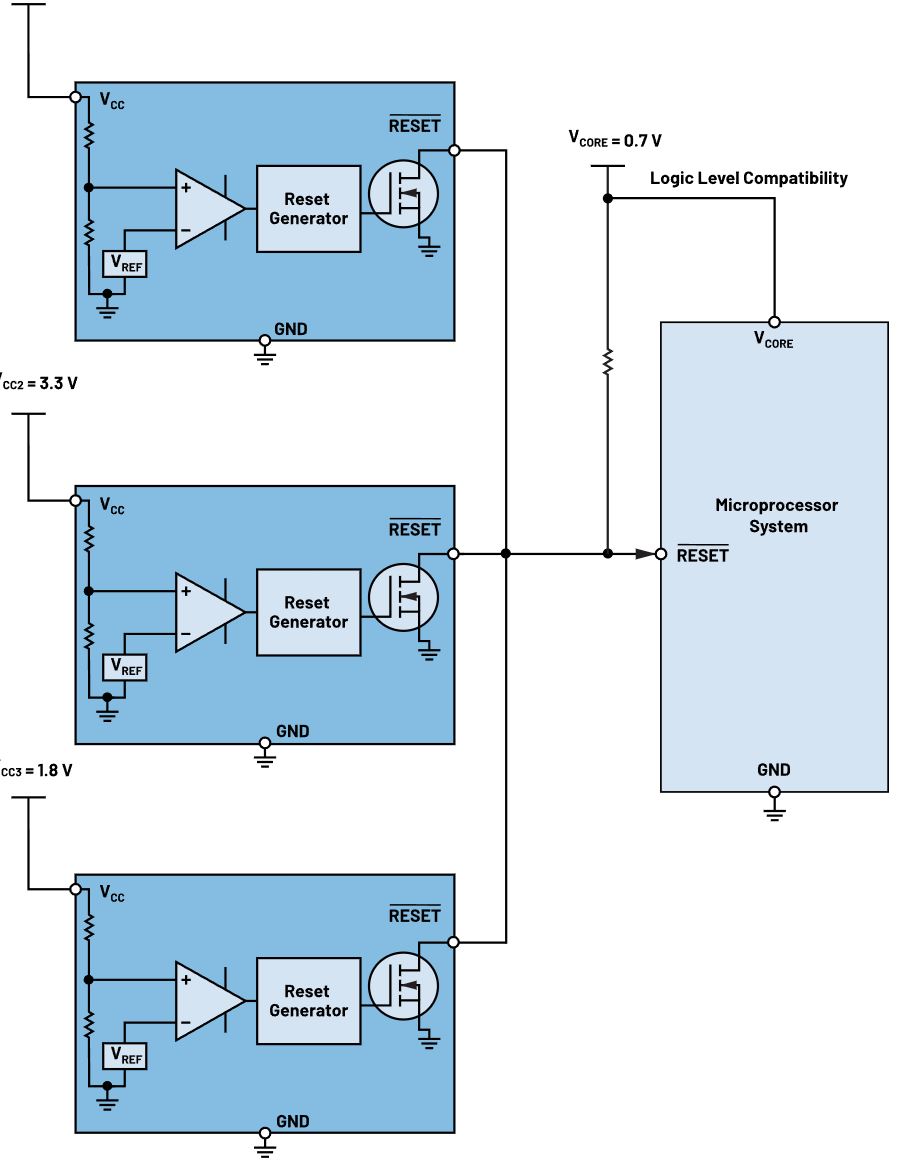

开漏输出的另一个优点是“线或”功能。将两个或多个监控电路的开漏输出连接到同一总线上,可以实现“负逻辑或”电路。这意味着,当任何一个监控电路的复位输出变为低电平时,总线为低电平。仅当所有复位输出都是高电平时,总线才为高电平。如果想要监控多个电源,并在任何一个电源电压下降时触发复位,这种拓扑会很方便。

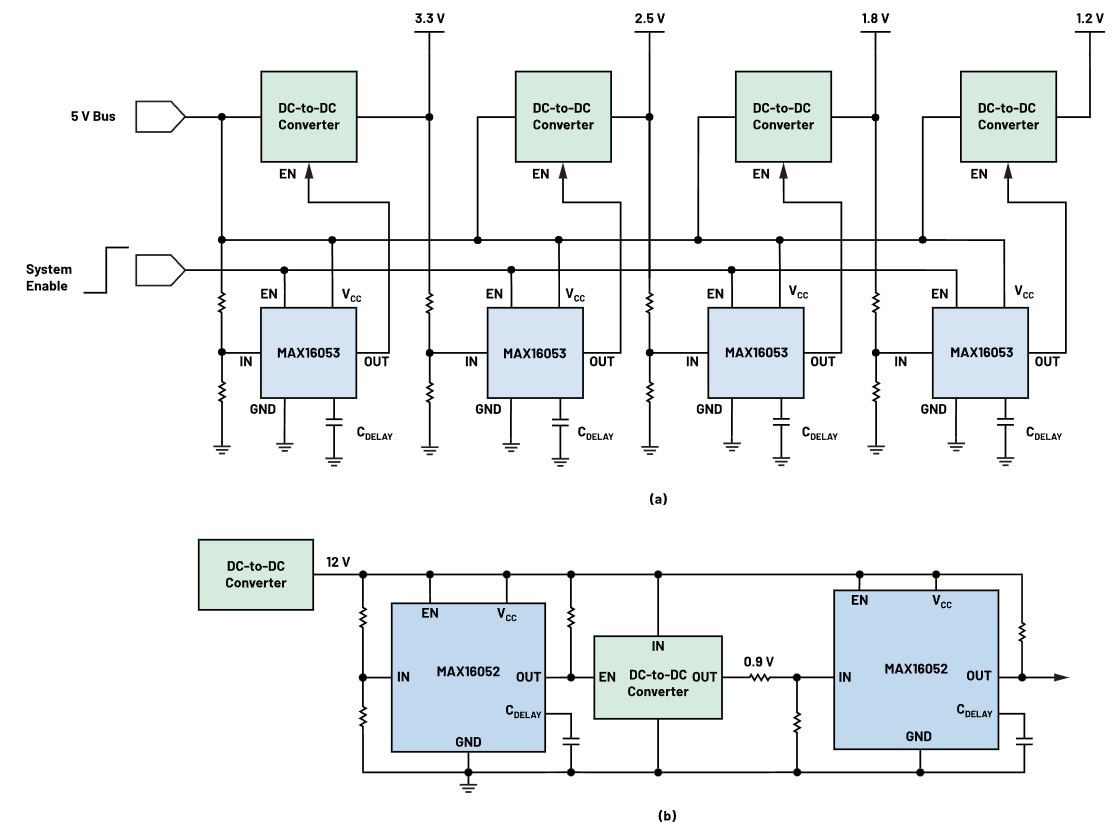

应用案例

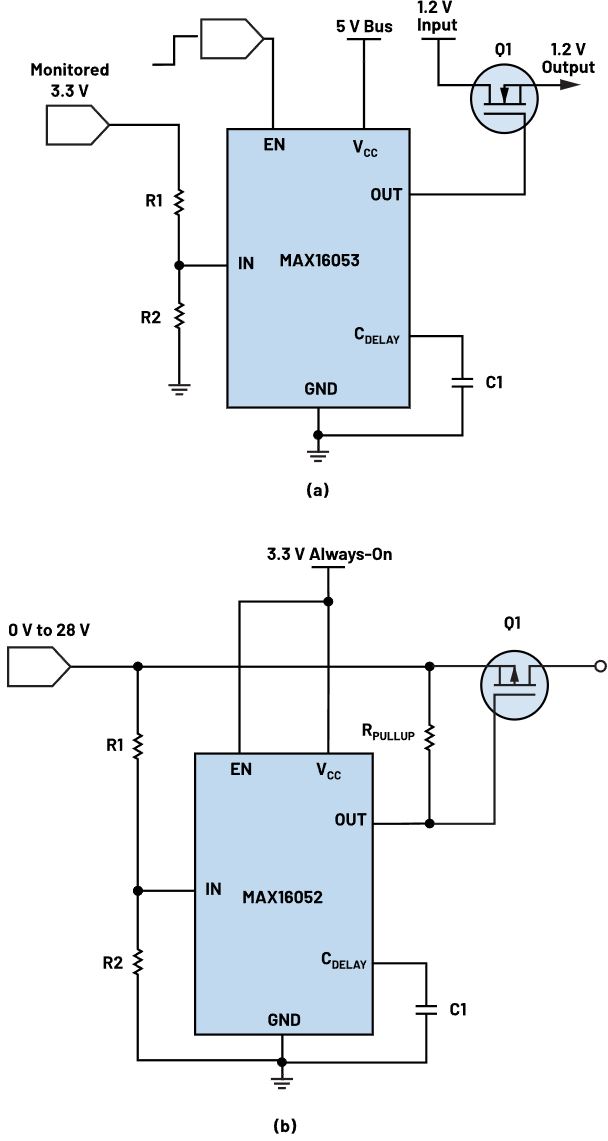

图9、10和11显示了电压监控器不同输出拓扑和极性的一些典型应用案例。图9显示了一个应用开漏拓扑的多电压系统示例。在多电压轨系统中,可以利用菊花链连接的低电平有效输出来执行时序控制,如图10a和10b所示。在某些应用中,正确的电源时序控制可能是首要的考虑因素之一。多轨系统(如基于FPGA的解决方案)通常需要并指定适当的电源时序,以防止出现系统故障和不稳定情况。图11a和11b显示了应用高电平有效输出的示例。对于这些情况,高电平有效输出用于使能或禁用高侧MOSFET,以实现开/关控制方案。此类配置可用于过压保护、低压时序控制等电路。高侧MOSFET也可使用电压监控器的低电平有效输出来驱动。有关详细信息,请参阅文章“利用低电平有效输出驱动高侧MOSFET输入开关以实现系统功率循环。”

图9. 多电压系统共用一个微处理器复位输入。

图10. 使用低电平有效输出(a)推挽拓扑和(b)开漏拓扑的多轨时序控制

图11. 高电平有效输出极性的应用。(a)采用推挽拓扑的N沟道MOSFET低压时 序控制。(b)采用开漏拓扑的P沟道MOSFET过压保护电路。

结论

电压监控器用于使能、禁用或复位另一个器件。监控器的常见应用是复位微控制器。监控器保护系统免受错误和故障的影响,从而提升应用的整体可靠性。设计时需要考虑电压监控器的输入、输出和时序规格。监控器具有不同的输出拓扑和极性,在不同的应用场景中可以发挥不同的优势,从而实现预期功能并提高系统可靠性。

本文转载自:亚德诺半导体