Speedster7t FPGA的亮点

. 在Int4整数格式下,可提供多达82K的乘累加单元(MAC)和高达122TOPS的运算能力

. 支持多种浮点格式和整数格式

创新的高性能FPGA系列产品

Achronix的Speedster®7t系列是一种革命性的FPGA架构,它经过了高度优化以满足人工智能/机器学习和高带宽数据加速应用日益增长的需求。Speedster7t FPGA系列产品专为这些高带宽工作负载而设计,具有一个革命性的全新二维片上网络(2D NoC)和一个针对人工智能/机器学习进行优化的、高密度的机器学习处理器(MLP)阵列。通过将FPGA的可编程性与ASIC的布线结构和计算引擎完美地结合在一起,Speedster7t系列产品创造了一类全新的“FPGA+”技术。高速接口支持世界级的带宽对于高性能计算、机器学习和硬件加速而言,至关重要的是在片内和片外传输数据的能力,无论是支持输入和输出的数据流,还是存储/缓冲这些数据。Speedster7tFPGA的架构可支持前所未有的带宽。

112Gbps SerDes

Speedster7t器件拥有多达32个业界最高性能的SerDes接口,可在1-112 Gbps的速率上运行。

PCIExpress Gen5

Speedster7t FPGA配备了多个PCIeGen5接口,同时支持16通道(×16)和8 通道(×8)配置。PCIe控制器接口支持双重操作,既可以作为端点(endpoint),也可以作为根复合体(rootcomplex)。

400GE以太网

每个Speedster7tFPGA都包括多个由8个SerDes通道和以太网MAC组成的以太网子系统,以支持广泛的应用。每个以太网MAC都具有很强的灵活性,可以支持总带宽高达400G的多个端口,同时每个SerDes通道都可以实现10G到100G之间的线路速率。高性能的以太网接口通过NoC连接到FPGA内部。

GDDR6

Speedster7t器件是唯一支持GDDR6存储器的FPGA,GDDR6存储器是目前可用的带宽最高的外部存储器件。Speedster7t FPGA具有多个GDDR6 SDRAM控制器端口,能够以可获取的最低DRAM成本(每存储位)提供最快的SDRAM访问速度。

每个GDDR6存储控制器都能够支持512 Gbps的带宽。因此,Speedster7t器件中多达8个的GDDR6控制器可以支持4Tbps的GDDR6累加带宽,并且以很小的成本就可提供与基于HBM的FPGA等效的存储器带宽。

DDR5

Speedster7t FPGA包括了DDR5存储器接口支持,以满足更深入的缓冲需求。PHY和控制器支持多种配置,例如印制电路板(PCB)上的各种焊接组件,UDIMM、SODIMM、RDIMM和LRDIMM模块,以及从4位到72位的位宽。PHY和控制器支持JEDEC规范定义的所有标准特性,并且与所有主要供应商的存储器均可兼容。PHY到硬件控制器的接口符合DFI 4.0规范,这使得设计人员可以用其软件控制器来替换硬件控制器。

全新的片上网络提供ASIC级别的性能

Speedster7t FPGA具有革命性的全新二维片上网络(2D NoC),旨在支持业界最高性能的接口协议。NoC还支持各种高速接口和存储器接口之间的直接连接。通过简单地针对任务配置NoC,一个主处理器可以直接从任意一个PCIe Gen5接口将数据传输至任意一个GDDR6或DDR5存储控制器,在这个应用案例中,没有用到FPGA的可编程逻辑,因为NoC可以管理所有事情——这种数据传输也不需要FPGA阵列内的可编程互连。NoC使用一系列高速的行和列网络通路在整个FPGA内部分发数据,从而在整个FPGA结构中以水平和垂直方式分布数据流量。NoC中的每一行或每一列都有两个256位的、单向的、行业标准的AXI通道,可以在每个方向上以512 Gbps的传输速率运行。

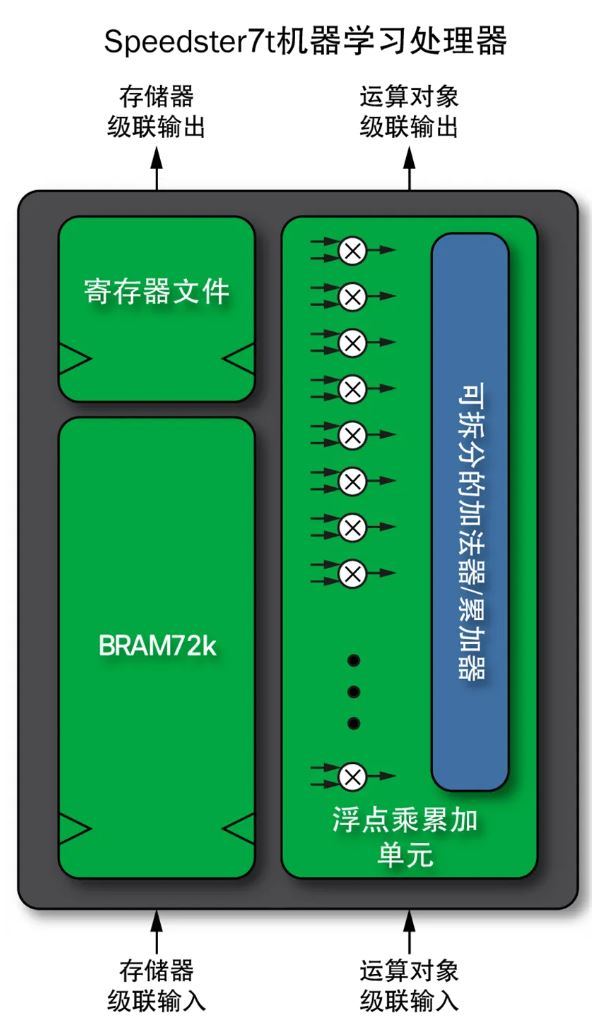

高度优化的计算性能

每个Speedster7t器件都具有大量的可编程数学计算单元,这些单元被集成至全新的机器学习处理器(MLP)模块中。每个MLP都是一个高度可配置的计算密集型单元模块,具有多达32个乘法器/累加器(MAC),支持4位到32位的整数格式和各种浮点模式,包括对Tensorflow的Bfloat16格式以及可显著提高性能的高效块浮点格式的原生支持。

MLP模块包括紧密集成的嵌入式存储器模块,以确保机器学习算法将以750 MHz的最高性能运行。这种高密度计算和高性能数据传输的结合造就了一种处理器结构,该结构可提供基于FPGA的最高可用的TOPS级别运算能力(TOPS即Tera-OperationsPer Second,每秒万亿次运算)。

内置安全功能

为了应对第三方攻击的威胁,Speedster7t FPGA配备了最先进的比特流安全保护功能,它们具有的多层防御能力可保护比特流的保密性和完整性。密钥是基于防篡改物理不可克隆技术(PUF)进行加密的,比特流由256位的AES-GCM加密算法进行加密和认证。为了防止边信道攻击,比特流被分段,每个数据段使用单独导出的密钥,且解密硬件采用差分功率分析(DPA)应对措施。此外,2048位RSA公钥认证协议被用来激活解密和认证硬件。用户可以确信的是当他们加载其安全比特流时,它是预期的配置,这是因为它已通过RSA公钥、AES-GCM私钥和CRC校验进行了身份验证。

设计工具支持

从设计验证到比特流生成和系统调试,Achronix的ACE设计工具现在可以为Speedster7t FPGA提供全面的支持。设计人员可以使用功能强大的布局规划工具(floorplanner)进行设计优化,并且在进入时序驱动的布局布线之前为所有设计模块实例分配区域或位置。ACE还包括一个关键的路径分析工具,可以分析时序以确保设计符合其性能要求。设计人员还可以使用ACE强大的Snapshot嵌入式逻辑分析器来创建复杂的触发条件,并显示在Speedster7t器件中运行的信号。

经验证的、可向低成本ASIC转换的途径,用以满足大批量需求

Achronix提供独立高性能FPGA芯片又提供嵌入式FPGA(eFPGA)知识产权(IP)的公司。Achronix在Speedcore™ eFPGA IP中采用的技术与其在Speedster7t FPGA中所使用的一样,可支持从Speedster7t FPGA到ASIC的无缝转换。FPGA应用通常具有一些必须保持可编程性的功能,而其他功能则是专用于特定系统应用的固定功能。对于转换为ASIC而言,固定功能可以被固化进ASIC结构中,从而减小芯片面积、降低成本和功耗。当客户使用Speedcore eFPGA IP将Speedster7t FPGA转换为ASIC时,有望节省高达50%的功耗并降低90%的成本。

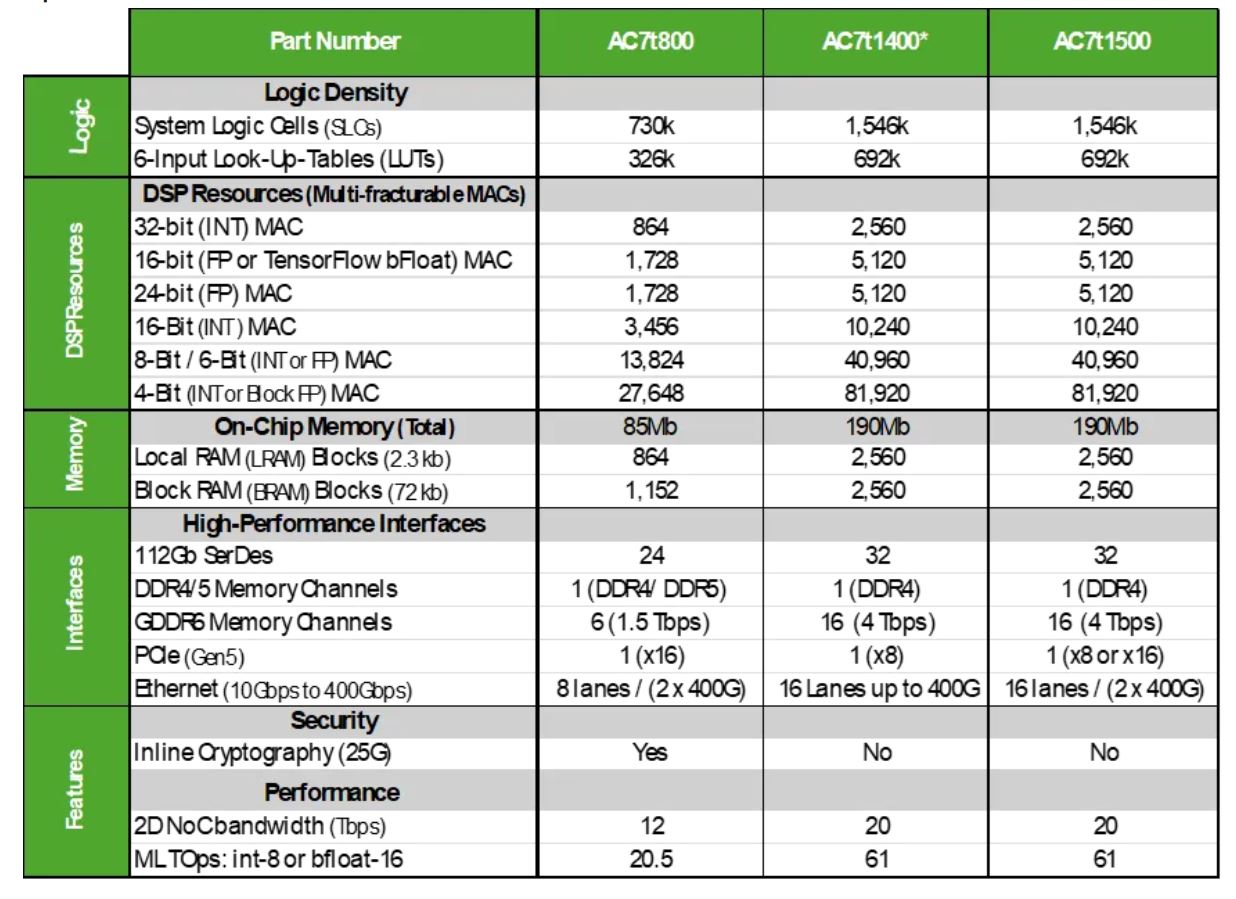

Speedster7t系列产品表

文章来源:Achronix