作者:Nathan Xu,AMD工程师,来源:AMD开发者社区

最新的DisplayPort TX/RX 1.4 Subsystem IP v3.1支持eDP v1.4b, 支持下面的eDP features:

Reduced Aux timing because the Aux sync pattern is reduced from 8 pulses to 16 pulses

Alternate Scrambler Seed Reset (ASSR)

Enhanced Framing

Fast link training

Black video

Backlight control by way of Aux

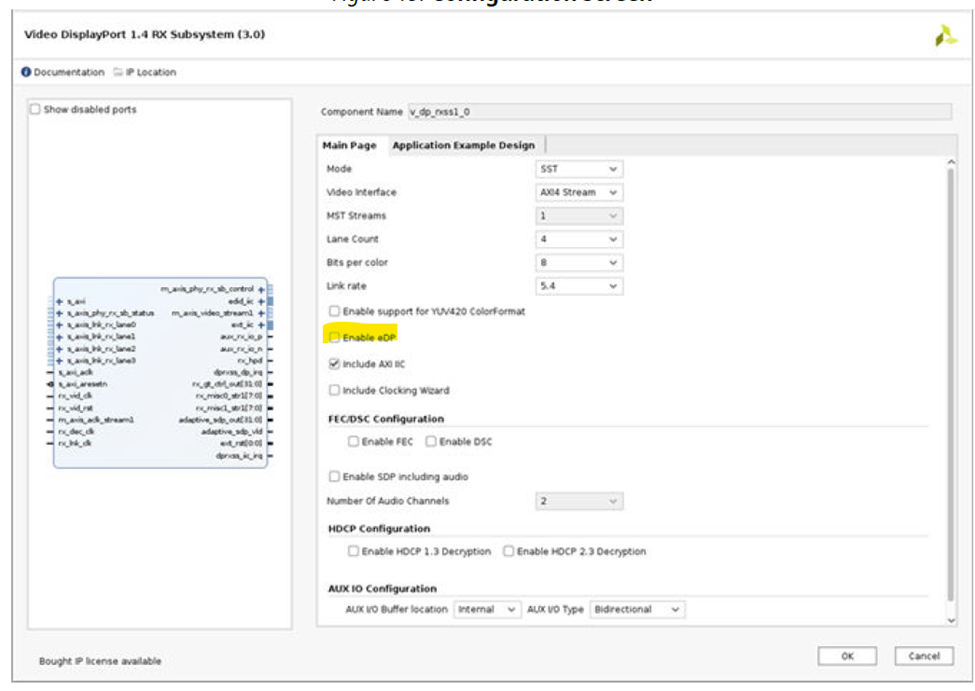

用户可以在DisplayPort RX Subsystem IP GUI设置”enable eDP”.

或者可以用下面的TCL命令使能eDP.

set_property -dict [list CONFIG.EDP_ENABLE {true}] [get_bd_cells v_dp_rxss1_0]

eDP与DisplayPort 1.4使用相同的硬件(connector, FMC/PCB, pinouts)

eDP -> fast link training:

按照eDP spec要求, ”fast link training"是必须支持的. 根据协议里”fast link training"的定义, 在DP cable连接上之后, 第一次training是"Full link training"(也就是DP协议定义的使用AUX接口通信的normal training), 在后面的eDP training, AUX transactions不需要. AMD DisplayPort 1.4支持这样的eDP ”fast link training", 还有一些其他形式的eDP training, 比如不需要"Full link training"的Aux Less training, 这不是协议要求必须支持的, AMD DisplayPort 1.4 IP不支持这样的training.

eDP example design:

目前没有eDP的example design, 但是, 你可以产生DisplayPort 1.4的example design, 然后在该example design 使能eDP, 我们在ZCU102做过这样的测试, eDP是可以工作的.

eDP AUX Sync pulse设置:

我们看到, AMD的DisplayPort 1.4 TX IP在配置为eDP时, 不能读取某些eDP monitor的RX DPCD, 导致training失败.

有些eDP monitor对AUX pulses的要求是, AUX SYNC应该是16 cycles(8 preamble 0s + 4 cycles of High + 4 cycles of Low).

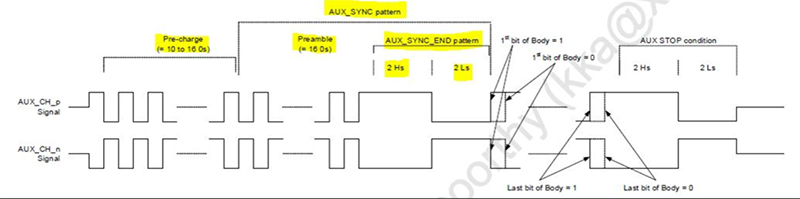

下面是协议上AUX pulses的要求. AUX_SYNC = 24 cycles (16 preamble 0s + 4 cycles of High + 4 cycles of Low), 如下:

AMD的DP 1.4 IP对AUX pulses的要求是AUX_SYNC = 24 cycles. 如果看到AUX 读取失败, 可以调整下面DP 1.4 TX的寄存器(地址是0x02C), 把16改为8. 这样能解决AUX Sync pulse不一致的问题.

Address offset : 0x02C

[4:0] - sync_pulses_request

[12:8] - sync_pulses_reply