作者:lucien,来源:北格逻辑

北格逻辑的 VESA DSC IP 推出已近半年,在此期间,我跟众多对DSC IP感兴趣的朋友进行了大量的交流。现将交流成果进行总结,详细阐述 DSC IP 在 FPGA 中的应用特点,期望能为大家在选择 DSC 解决方案时提供有益参考。

DSC IP 在FPGA上部署的局限性

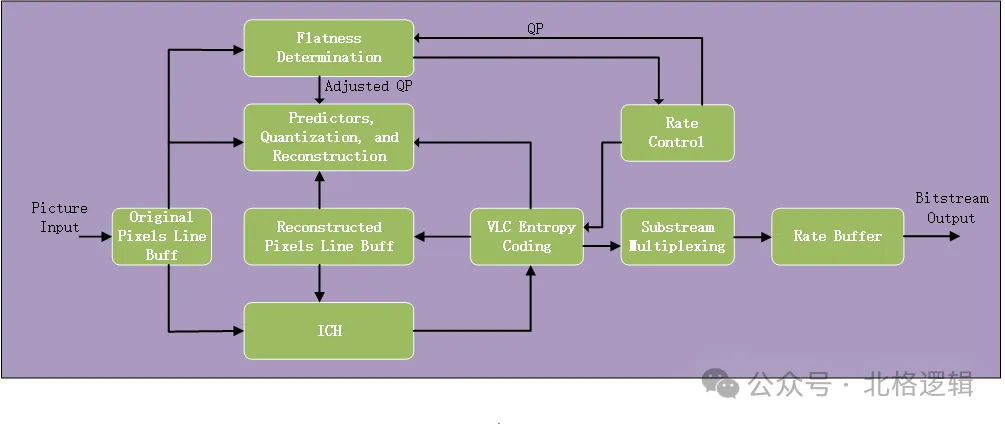

首先给一个结论:DSC IP并不适合在FPGA里面部署,理由是它占用的资源太多了。作为一个针对视频传输接口设计的图像压缩算法,DSC为了在压缩过程中尽量减少失真,付出了巨大的代价,导致DSC IP不仅资源使用量大,工作主频也跑不高。为了得到最佳的编码效果,DSC有三种不同的预测方式和ICH历史颜色索引功能,从中挑出兼顾最小码率和最小失真的编码方式,其中MMAP、BP、ICH占用的逻辑资源都不小,相当于类似功能的模块DSC有4个,资源使用量自然偏大。DSC在编码过程中,将三个像素组成一个group,无论是预测模式和ICH都需要使用上一个group的重建值(即在解码端恢复出来的像素值),无法将多个组展开并行计算。为了提升处理性能,必须将单个group的处理时间减少,这导致在MMAP模块中的逻辑级数很大。这是因为在MMAP中三个像素做预测时,第二个像素需要用到第一个像素的反向量化残差(先要计算出预测值,然后计算残差,再量化截断),第三个像素需要用到第二个像素的反向量化残差,而且整个MMAP的复杂预测过程需要在1-2时钟内完成。过大的逻辑级数会导致DSC的主频最大只能跑到200Mhz左右。

图1.DSC编码流程

FPGA 部署 DSC IP 的成本考量

由于 DSC 资源使用量大,且无法通过提升主频来降低资源使用,在 FPGA 中部署 DSC IP 的成本相对较高。DSC编码IP单个slice的处理性能是1080P@60fps,工作主频是200Mhz(UltraScale/UltraScale+ ,-2/-3速率)。好消息是,DSC 解码IP单个slice的处理性能是1080P@120fps,工作主频能跑到400Mhz(UltraScale/UltraScale+, -2/-3速率)。DSC解码IP能跑更高主频是因为在解码器中MMAP三像素能够并行处理,第二像素和第三像素需要的反向量化残差就是解码的输入数据简单移位即可获取。

DSC IP 与视频接口 IP 的协同

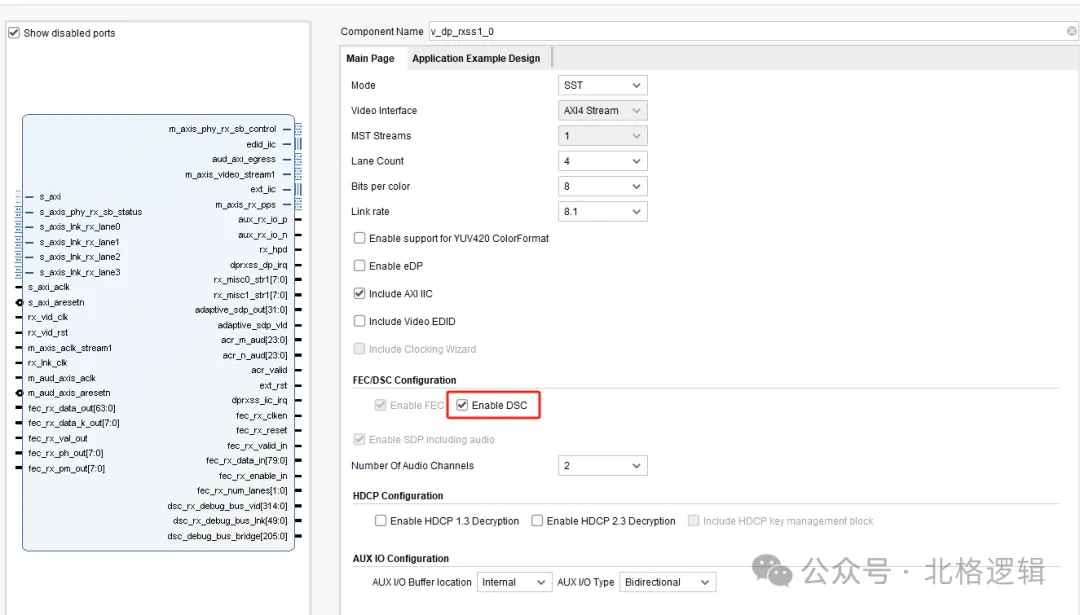

DSC IP应用于FPGA时,需要相应的视频接口IP支持传输压缩后的码流。DP1.4、MIPI CSI 1.3、HDMI2.1以及后续版本在规范中都定义了对DSC压缩后码流的支持。下面以AMD 的DP1.4接口IP为例,简单介绍一下DP接口与DSC编码的配合。在AMD的DP1.4 RX IP中,可以在生成IP时选中“Enable DSC",选中后生成的IP接口会包含” AXI4-Stream DSC Video Interface“和” AXI4-Stream PPS Receive Interface“。其中”AXI4-Stream DSC Video Interface“接口的输出的是DSC压缩的码流;” AXI4-Stream PPS Receive Interface“接口输出的是DSC的PPS数据。PPS数据中包含DSC编解码的所有参数,依据这些参数,就可以将DSC压缩码流解码成像素数据。

图2.在DP1.4 RX IP中打开DSC enable 选项

典型应用场景介绍

目前,DSC IP 在FPGA中的应用场景主要集中在以下两个场景:

1.各类显示屏生产测试:显示屏中嵌入了支持 DSC 解码的芯片,因此在显示屏测试设备中,需嵌入 DSC 编码功能。在该场景下,测试设备以 FPGA 作为视频生成器,将服务器上的测试视频导入 FPGA 后,利用 DSC 进行编码,再通过 MIPI DSI 等接口输出至显示屏,从而对显示屏进行测试。

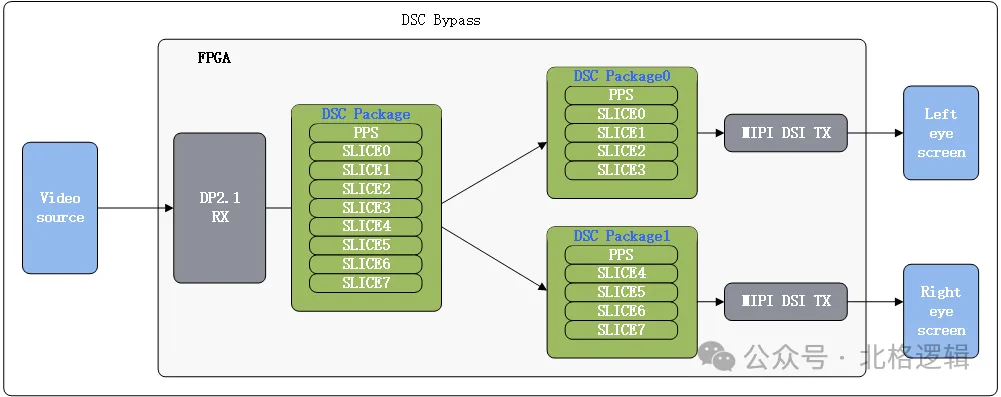

2.VR/CR 等应用中大分辨率、高帧率接口转换:在这类场景中,DP、DSI 等接口需借助 DSC 压缩功能提升视频接口传输能力。输入接口的 DSC 压缩包只需解封装,按照输出接口要求重新打包即可输出。此场景实现的是 DSC bypass 功能,由于无需真正的解码和重新编码,资源耗费较少。重新打包并生成 PPS 后,即可从输出接口输出,此时无需选用大容量的 FPGA 就能实现 DSC bypass 功能。以 VR 实际应用为例,在 DP2.1 接口输入大分辨率图像,将其拆分成2个小分辨率输出至 VR 的2个 MIPI 显示屏。在此过程中,DSC 压缩后的数据以 slice 为单位,先解封装再重新打包,并重新生成 PPS,便可将 DP2.1 输入的压缩数据分成多份分别输出,同时确保多个输出屏的同步性。

图3.在FPGA中实现DSC bypass功能

如果您对DSC IP具体的技术参数感兴趣,请移步到我司官网查看:北格逻辑。欢迎您与我们进行技术交流。