来源:内容编译自design-reuse,谢谢。

近日,美国半导体初创公司 Zero ASIC 宣布推出世界上第一款开放标准 eFPGA IP 产品Platypus。据他们所说,Platypus 是第一个也是唯一一个具有以下特点的商业 eFPGA IP 产品,是一个100%开放和标准化的FPGA架构、100% 开源 FPGA 比特流格式、100% 开源 FPGA 开发工具。

资料显示,Zero ASIC 是一家位于马萨诸塞州剑桥的半导体初创公司。该公司的使命是通过芯片和自动化实现硅片的普及。Zero ASIC 正在构建世界上第一个可组合芯片平台,使数十亿个独特的硅片系统能够在数小时内从现成的芯片目录中组装出来。

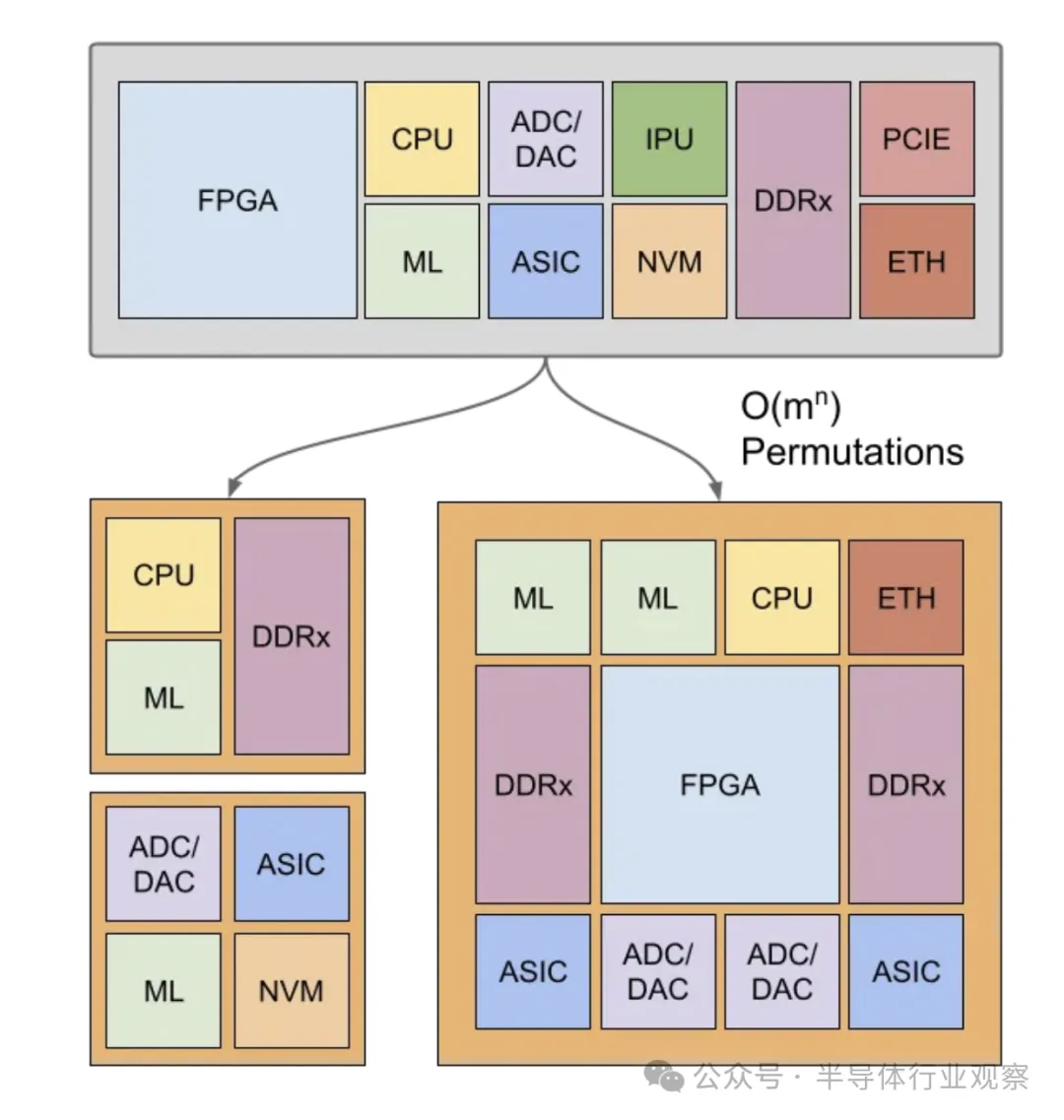

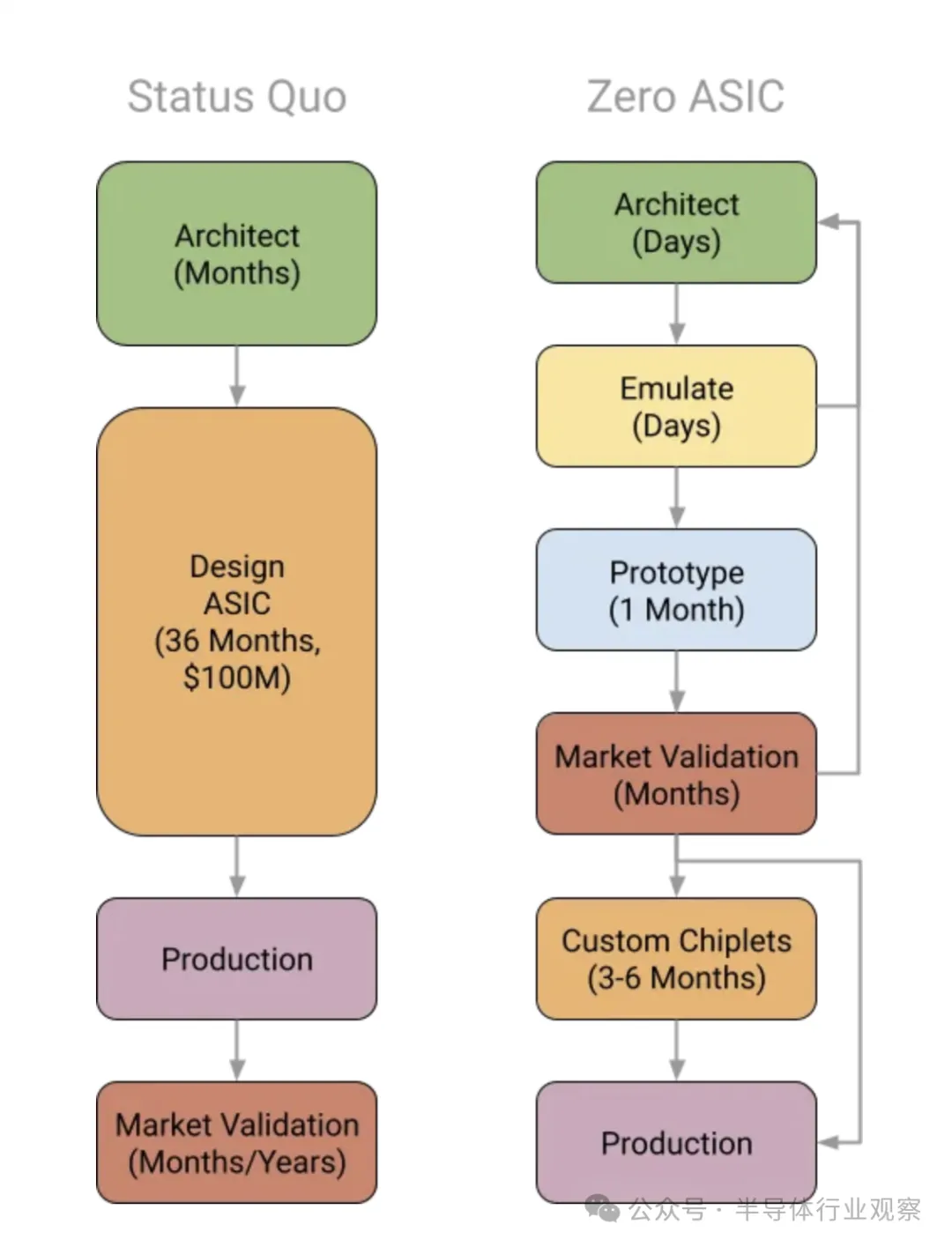

如图所说,Zero ASIC 正在构建世界上第一个可组合芯片平台,该平台能够从现成的芯片目录中在数小时内组装数十亿个独特的硅系统,拥有以下特征:

标准化芯片——首次演示完全标准化的芯片,支持 O(m^n) 系统排列(m=库大小,n=基板插座)。

智能基板——有源 3D 硅基板将计算和网络分离,实现类似乐高的系统组合。

世界领先的能源效率——低于 0.1 pj/bit 的芯片通信效率。

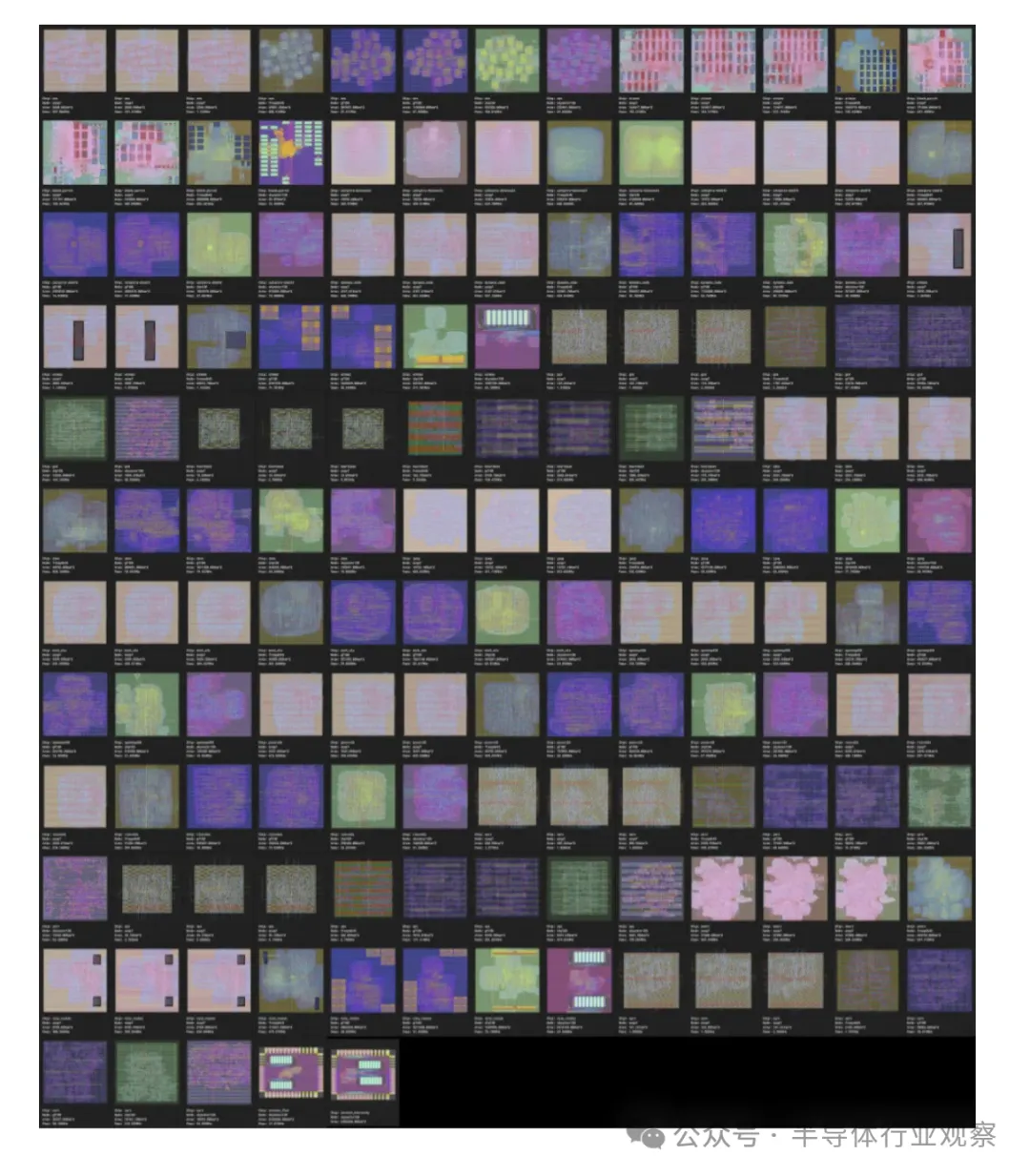

这个可扩展处理器 IP 生成器平台能够根据每个应用程序快速生成定制的 FPGA、CPU、NOC 和 DSP,以满足最严格的系统要求。

自动化——按下按钮即可实现 100% 自动 IP 生成;

可扩展——性能从边缘可扩展到数据中心。

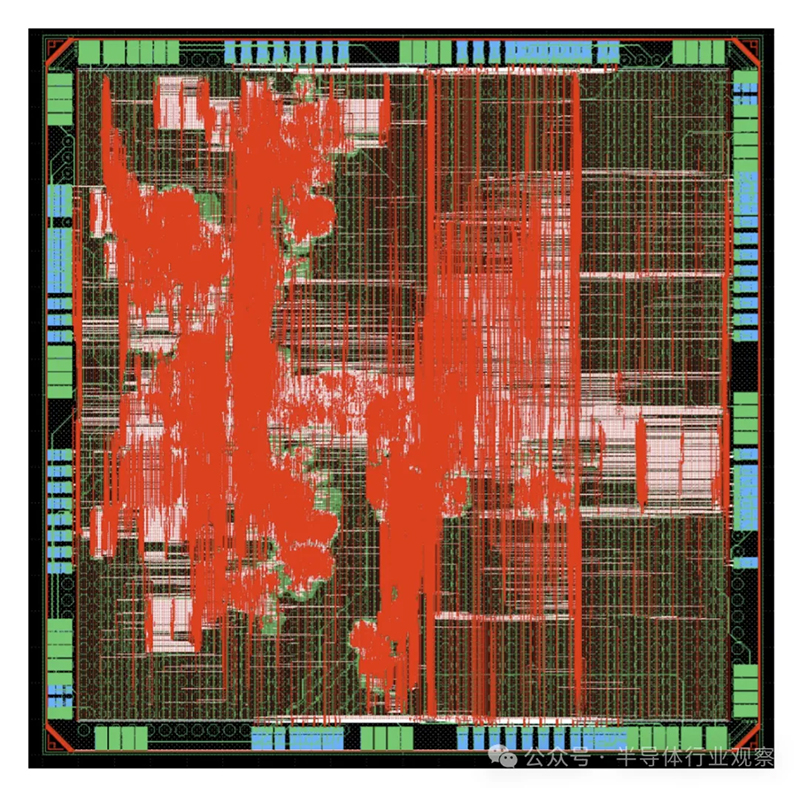

成熟——我们的 IP 生成器已用于 65nm、28nm、16nm 和 12nm 芯片的流片。

为了降低定制 ASIC 的门槛,Zero ASIC 开发了开源硬件编译平台SiliconCompiler。

经过实战检验——经过硅验证的流程支持大量开源和专有 EDA 工具和 PDK。

24 小时流片周期——优化的云规模构建基础设施可实现快速的设计周期。

确定性——标准化清单和设计即代码方法能够保证编译确定性。

开源——没有锁定或隐藏的议程!

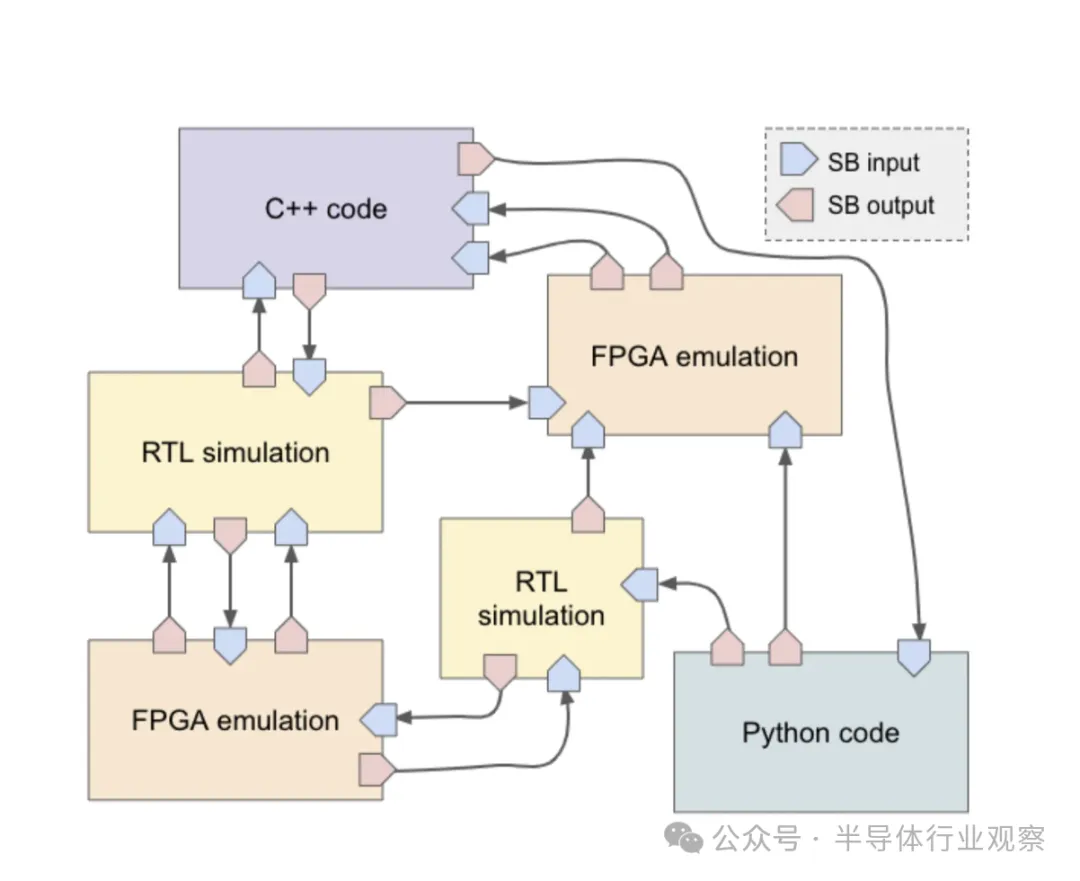

公司的Switchboard数字孪生平台可实现近乎实时的仿真,让团队能够在投入昂贵的制造周期之前优化系统硬件和软件。

快速地——与领先的商业模拟器相比,我们的芯片优化数字孪生平台可使构建和运行时间提高一个数量级。

可扩展——我们对延迟不敏感的特点可实现晶圆级设计及更大规模的设计。

灵活的——标准化模型接口有利于高级模型(例如 QEMU)、周期精确的 RTL 模拟器(例如 Verilator)和硬件在环系统(例如 AWS F1 FPGA)之间的无缝转换。

在他们看来,这款产品将重塑 ASIC 设计:

步骤 1:模拟——利用Digital Twin平台优化硬件和软件。

步骤 2:原型——构建基于快速小芯片的原型。

步骤 3:优化——根据市场反馈优化芯片组成。

步骤 4:进入市场——下达生产采购订单并开始制造。

最后获得利润!

如他们所说,过时是航空航天、国防、医疗保健、通信、汽车和工业应用中基于 FPGA 的系统的一个关键问题,这些系统的使用寿命为 10 至 50 年。例如,以 F-35 战斗机的开发为例,它始于 1997 年,直到 2021 年才全面投入生产。在此期间,晶体管密度增加了 10,000 倍,FPGA 行业推出了六代新架构。半导体技术的不断发展与基础设施开发周期缓慢之间的这种不匹配导致美国军方估计有 500 亿至 700 亿美元的过时相关 NRE 成本,而所有替换半导体零件中有 15% 是假冒的。

自 20 世纪 80 年代 FPGA 诞生以来,商用 FPGA 产品变得越来越复杂、标准化程度越来越低、透明度越来越低,加剧了与零件过时和假冒相关的问题。在最好的情况下,FPGA 设备或 eFPGA IP 核的停产通知需要重新设计整个子系统。在最坏的情况下,这可能会导致整个程序的终止。

解决 FPGA 过时和假冒问题的下一个合理步骤是摆脱单一来源部件并建立一套开放标准的 FPGA 架构,类似于为存储器和无源元件创建的成功标准。

过去 25 年来,人们曾多次尝试开放 FPGA。1997 年5 月,通用布局布线 (VPR) 开源 FPGA 研究平台问世,自此帮助降低了高质量、可重复的 FPGA 研究的门槛。遗憾的是,VPR 仍然只是一个研究工具,商用 FPGA 仍然没有完全开放的 RTL 到位流程。

为了解决缺乏完全开放的 FPGA 设备的问题,DARPA 于 2018 年资助了 OpenFPGA 和 PRGA FPGA 生成器研究项目。虽然这些开源生成器促进了几种学术芯片的流片,但最终的设计既没有标准化,也没有商业化。

为了规避 FPGA 不透明的问题,人们采取了不同的方法,对商用 FPGA 进行逆向工程。然而,随着 FPGA 复杂性随着摩尔定律的推移而激增,这项任务变得越来越困难和昂贵。

尽管做出了这些努力,但截至目前,市场上仍然没有一款开放、标准化的商业 FPGA 产品。

随着 Platypus eFPGA 系列的推出,Zero ASIC 通过在开源 Apache 许可下公开发布其商用 Z1000 eFPGA IP 的完整架构描述和比特流格式,向标准化 FPGA 迈出了重要的一步,目标是使其成为一个开放标准。

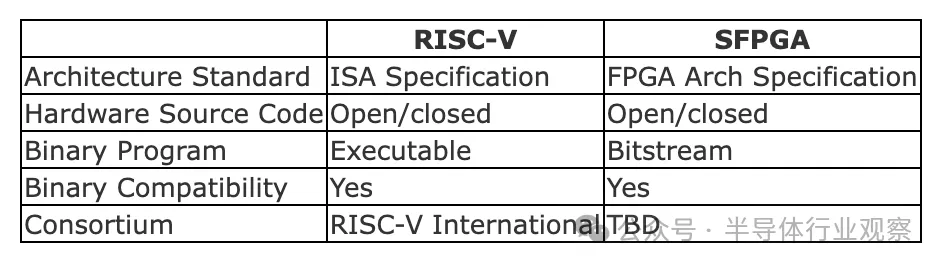

从历史上看,开放标准已被证明是防止过时和掠夺性定价策略的有效方法。值得注意的无处不在的开放硬件标准包括 RISC-V ISA、IEEE 以太网 PHY、JEDEC 存储器、无源封装(例如 0603、0805)、PCIe 和 USB。就像 RISC-V 一样,创建开放标准并不意味着实现必须是开源的。下表说明了成功的 RISC-V ISA 标准与拟议的 FPGA 方法之间的相似之处。

RISC-V ISA 最初是加州大学伯克利分校的一个不起眼的研究项目,第一份规范于 2011 年发布。2014 年,David Patterson 和 Krste Asanovic 提出了令人信服的论据,阐述了 ISA 应该免费的原因,从而引发了 RISC-V 运动。十年后,RISC-V 现在每年出货量达数十亿台设备。

“开发开放标准的 FPGA 架构和符合标准的组件生态系统将彻底改变基于 FPGA 的系统设计,就像 RISC-V 改变了 CPU 设计一样。就像 RISC-V 一样,市场动态将决定开放标准的潜在优势是否能克服供应商锁定的现状惯性。” —Andreas Olofsson说。

本文转载自:半导体行业观察