在投影显示与车载 HUD 领域,设备光轴与投射平面夹角偏差所引发的梯形失真问题,长期以来一直是行业面临的棘手难题。传统的光学补偿方案因受机械结构调整范围的限制,在应对复杂安装场景时往往力不从心。北格逻辑的 Keystone 梯形校正 IP,借助高效的数字图像预处理技术,成功构建了光学失真与数字补偿的闭环系统。

梯形校正技术的核心在于运用逆向几何变换算法,通过将标准矩形图像预先变形为适配光学路径的任意四边形,与投影系统产生的梯形畸变形成空间矢量中和。这种 “数字先行” 的校正理念,确保了最终投射图像无论在何种安装角度下,都能精准呈现矩形显示效果。此方案可广泛应用于超短焦投影、多平面融合 HUD 等前沿显示领域,有力推动智能座舱与沉浸式影音体验迈入新的发展阶段。

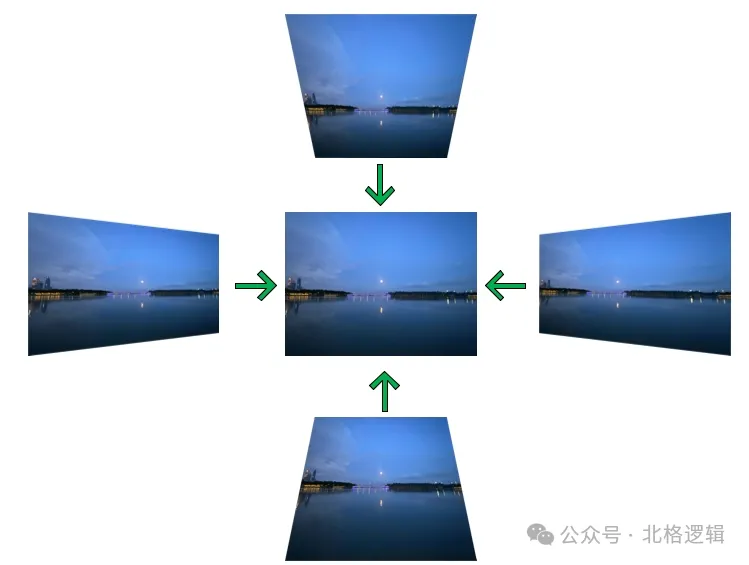

图1.keystone校正效果

Keystone 梯形校正技术主要由透视变换算法和插值算法两部分构成。基于单应性矩阵的透视变换算法,构建了三维空间坐标转换模型。通过建立目标图像与源图像的双向坐标映射关系,实现了亚像素级的几何校正精度。该算法支持动态参数更新,能够在 0.5 秒内完成新坐标系的实时重建。针对不同应用场景,该技术提供了可配置的插值方案:

高效模式:双线性插值采用 2×2 像素矩阵,在计算资源与图像质量之间达成了极佳的平衡。

品质模式:双三次插值基于 4×4 像素邻域,借助三次卷积核函数,实现了影院级的平滑过渡效果。

北格逻辑设计的 Keystone IP 核,采用全硬件加速架构,在 FPGA 平台实现时具备以下显著技术亮点:

采用纯硬件流水线设计,无需上位机软件参与参数计算及流程控制,可兼容各类无处理器架构的 FPGA 芯片。

配置极为简便,仅需输入源图像和目标图像的 4 个顶点坐标即可投入工作。

设计紧凑高效,所占用的逻辑资源少。

变形幅度大,缩放能力强,能够充分满足大幅度变形及不同投影距离的需求。

参数生效迅速,0.5 秒内新配置即可生效。

支持 4 个独立形变区域并行处理,各区域可配置不同变换参数,适用于投影区域由多个平面组成的复杂情况。

整个计算过程中,仅需对源图像进行一次写入和读出操作,以及对变形参数进行一次读出操作。每次 DDR 读写 burst 长度不小于 128,数据位宽为 256bit,有效避免了频繁的读写切换和跨行操作,内存使用效率极高。

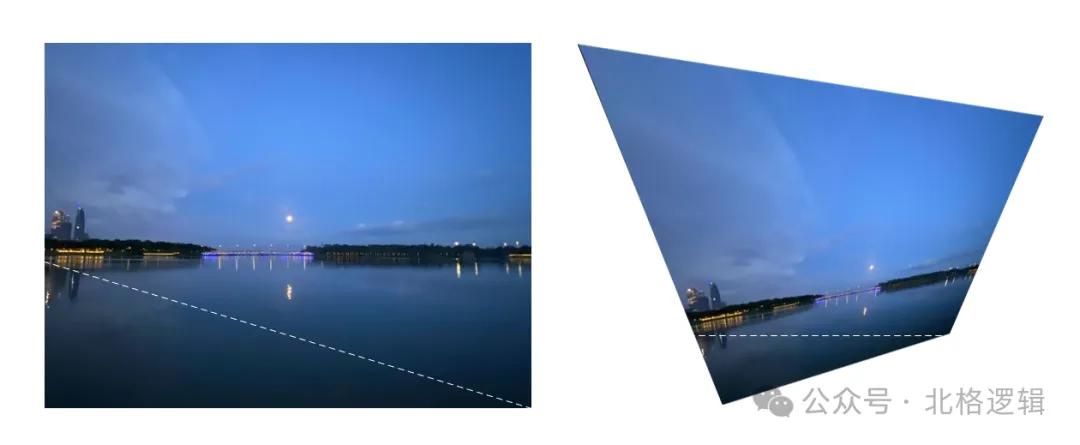

图2.keystone目标图像单行像素在源图像中的映射线

配置生效时间: 小于 0.5 秒;

计算性能:能够实时处理 4K@60fps 的图像;

变形幅度:目标图像单行像素最大可映射1024行源图像数据;

缩放幅度:1 - 4 倍连续可调;

计算延迟:1 帧。

北格逻辑致力于为FPGA生态圈提供高质量的图像处理类IP,未来我们会升级keystone IP,增加桶形失真和枕形失真的校正,提供更多强大的畸变校正功能。目前keystone IP在多块开发板上提供了演示程序,欢迎各位朋友实测。更多细节,敬请关注北格逻辑官网:www.berglogic.com。

文章来源:北格逻辑