作者:Xu Dong,AMD工程师;来源:AMD开发者社区

本篇博文旨在将 O-RAN 仿真系列博客扩展至多个分量载波 (CC) 的用例。其中还涉及到 O-RAN 通道处理 (OCP) 模块中的 CCID 配置。

软件版本:

Vivado 2023.2,含来自(答复记录 000035790)的补丁

设计生成:

第 1 步:请参阅 O-RAN 仿真系列博客,了解如何将 PCAP 文件转换为 MEM 文件。

注释:我在本篇博文中使用的 PCAP 可从此处下载:Zynq UltraScale+ RFSoC DFE Tools Secure Site -> IP Cores and Ref Design v2023.1 -> Keysight Configuration Files for TRD Test Report -> e1_cc2_u0_bw100_nocomp_prach127.pcap。此 PCAP 含 2 个 CC。

用户不应局限于使用该 PCAP 文件,任何不少于 2 个 CC 的 PCAP 都应有效。

第 2 步:遵循 O-RAN 仿真博客中的设计示例生成步骤进行操作。

参数配置:

生成设计后,需要基于您自己的 PCAP 文件修改以下参数:

参数名称 | 描述 | 本篇博文中的 CC0 值 | 本篇博文中的 CC1 值 | 相关寄存器 |

ipdtb.ena_vlan | VLAN 使能:如果 PCAP 中存在 VLAN 标签,则设为 1 | 0 | 0 | 0x2200 |

ipdtb.cc | CCID | 0 | 1 | 影响所有 CC 相关寄存器,CC1 寄存器地址 = CC0 地址 + 0x70,CC2 寄存器地址 = CC1 地址 + 0x70,依此类推 |

ipdtb.nugy | CC 子载波间隔参数集 (numerology) | 0 | 0 | 0xe100 (CC0) |

ipdtb.rbs | 此 CC 的 RB 编号 | 273 | 273 | 0xe100 (CC0) |

ipdtb.pd_d_sn | 下行链路符号缓冲器编号 | 5 | 5 | 0xe114(CC0) |

ipdtb.pd_d_ss | 每个 CC 0 的下行链路用户平面数据指针的起点 | 0 | ipdtb.pd_d_sn + ipdtb.pd_d_ss | 0xe114(CC0) |

ipdtb.pd_d_bs | 下行链路数据缓冲器起始索引。它与每个 CC 的起始索引相关联。 | 0 | ipdtb.pd_d_sn | CC0: |

ipdtb.pd_d_bw | 每个符号的缓冲器大小。计算每个符号缓冲器所需的字数。 | 1780 | 1780 | 决定 ipdtb.pd_d_bs 相关寄存器的值。 |

ipdtb.pd_c_sn | 用于适配接收窗口的下行链路控制符号的最大数量。 | 4 | 4 | 0xe114(CC0) |

ipdtb.pu_c_sn | 与 pd_c_sn 类似,但 pu_c_sn 用于上行链路控制符号。 | 4 | 4 | 0xe114(CC0) |

ipdtb.pd_cmsy | 该 CC 每个符号的 PDxCH Ctrl 报文数 | 12 | 12 | 0xe160 (CC0) |

ipdtb.pu_cmsy | 该 CC 每个符号的 PUxCH Ctrl 报文数 | 12 | 12 | 0xe164 (CC0) |

ipdtb.pu_cta_sym | 上行链路,指定 CTRL_TIME_ADV 偏移 10 ms 选通的符号数 | 3 | 3 | 0xe120 (CC0) |

ipdtb.pu_cta_cyc | 上行链路,指定 CTRL_TIME_ADV 偏移以上 abs_symbol 偏移的时钟周期数 | 10056 | 10056 | 0xe124(CC0) |

ipdtb.pu_bidf_sym | 上行链路,指定 UL BID Forward 偏移 10 ms 选通的符号数 | 3 | 3 | 0xe144(CC0) |

ipdtb.pu_bidf_cyc | 上行链路,指定 UL BID Forward 偏移以上 abs_symbol 偏移的时钟周期数 | 13000 | 13000 | 0xe148(CC0) |

ipdtb.pd_cta_sym | 下行链路,指定 CTRL_TIME_ADV 偏移 10 ms 选通的符号数 | 2 | 2 | 0xe130(CC0) |

ipdtb.pd_cta_cyc | 下行链路,指定 CTRL_TIME_ADV 偏移以上 abs_symbol 偏移的时钟周期数 | 2056 | 2056 | 0xe134(CC0) |

ipdtb.pd_tdecap | 下行链路,指定用户平面数据接受窗口的结束位置。该值即与 10 ms 选通的偏移。 | cc_dl_setup_d_cycles = ACTUAL_PERIOD_CP - (tDECAP / | 25948 | 0xe138 (CC0) |

ipdtb.pd_udcmphdr | 下行链路:pd_udcmphdr[7:4]:IQ 宽度 | 0x00(无压缩,IQ 宽度为 16 位) | 0x00(无压缩,IQ 宽度为 16 位) | 0xe11c(CC0) |

ipdtb.pu_udcmphdr | 上行链路:pu_udcmphdr[7:4]:IQ 宽度 | 0x00(无压缩,IQ 宽度为 16 位) | 0x00(无压缩,IQ 宽度为 16 位) | 0xe118(CC0) |

下一步是将这些值传递给仿真任务。

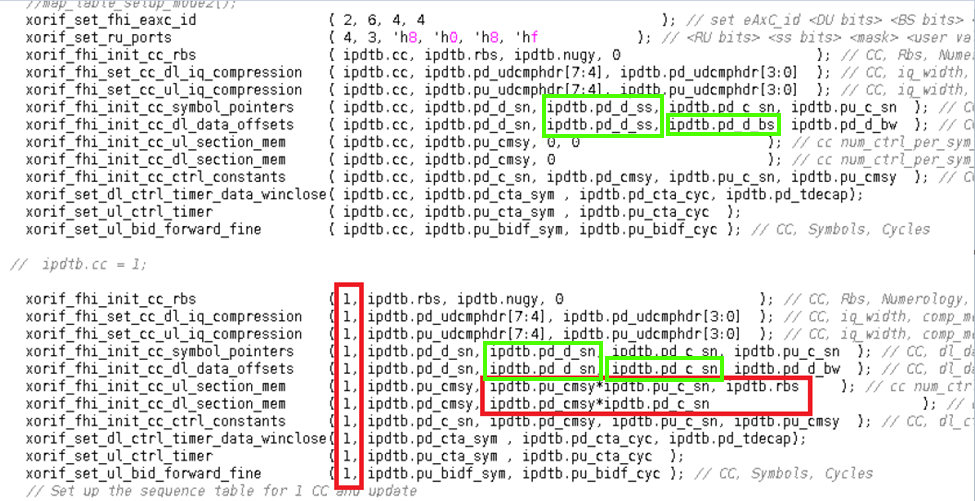

xorif_set_fhi_eaxc_id 和 xorif_set_ru_ports 适用于所有 CC。本篇博文中的值是以 DFE TRD 参考设计内部的 DFE TRD 配置文件 orif_example1.py 为基础计算所得的。

以下截屏显示了分配的值。各矩形中的值显示了 CC1 与 CC0 的差异。

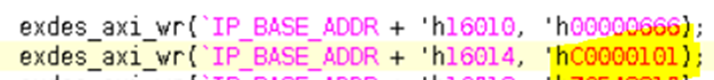

下一步,注释掉与 cc_reload/cc_enable 相关的任务(原因是多 CC 用例存在已知问题)。手动给寄存器赋值。每个位对应表示一个 CC。

对于 1 个 CC,赋值 `h1

对于 2 个 CC,赋值 `h3

对于 3 个 CC,赋值 `h7

对于 4 个 CC,赋值 `hf

依此类推

如果设计包含 OCP(O-RAN 通道处理),则可控制第二个 CC 的寄存器 0x16014 中的 CCID 数量。

仿真波形观察

现在,2 个 CC 的所有参数均已配置完成,让我们来看看仿真波形。

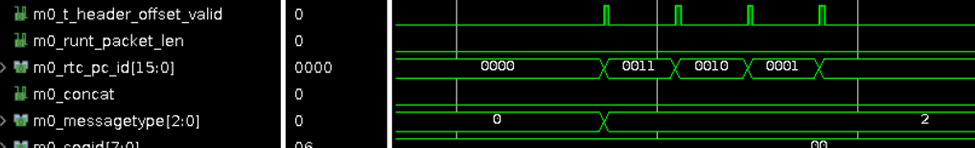

在以下示例中,rtc_pc_id 内接收到一个控制平面数据包(报文类型 =2),其中含 2 个 CC

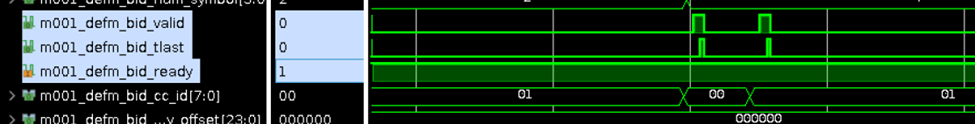

您可关联的 SS Deframer 串流中的 BID 接口内看到 2 个 CC_ID:

如果收到用户平面的数据包(报文类型 = 2),那么可以确认 2 个 CCID 都出现在 mXXX_defm_data_tuser 的位 [30:27] 上

在 OCP 的 m_dl_ft_* 接口上,可以看到 2 个 CCID 都出现在位 7:4(当前数据包的 CC ID)上